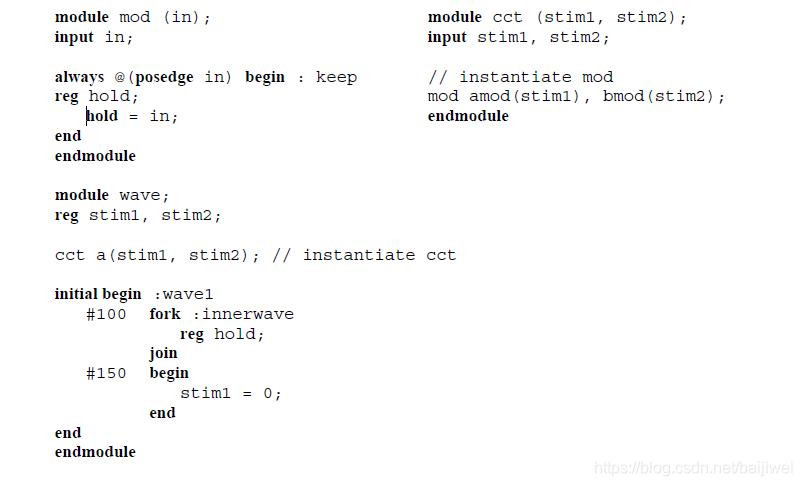

在Verilog里面采用module/endmodule 来组成整个design的hierarchy结构, 比如, 如下的代码:

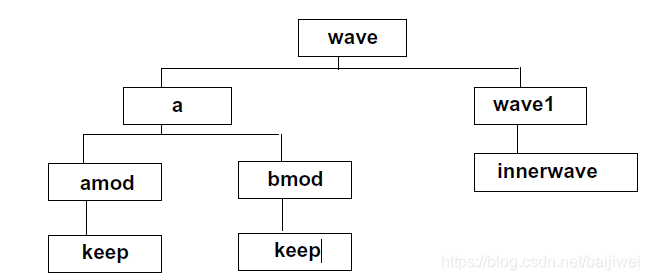

会产生如下的hierarchy结构:

目前在Verilog的LRM, 有如下几种scope类型:

- Module

- Task

- Funcion

- Named block

在IVerilog 里面, 定义了如下6中scope以及相关的定义如下:

-

vpiModule

-

vpiTask

-

vpiFunction

上述3中, 比较常见, 忽略例子; -

vpiNamedBegin

begin … end之间的语句是串行执行的;begin: scope_name declaration; state1 state2 ... stateN end -

vpiNamedFork

fork … join之间的语句是并行执行的;fork: scope_name declaration; state1 state2 ... stateN join -

vpiGenScope

1 、generate-for语句必需用genvar关键字定义for的索引变量;

2、 for的内容必须用begin…end块包起来,哪怕只有一句;

3、 begin…end块必须起个名字;module gray2bin1 (bin, gray); parameter SIZE = 8; // this module is parameterizable output [SIZE-1:0] bin; input [SIZE-1:0] gray; genvar i;generate for(i=0; i<SIZE; i=i+1) begin:bit assig

本文深入探讨了Verilog语言中scope的概念及其在IVerilog编译器中的实现方式,包括module、task、function等不同类型的scope,并详细介绍了这些scope在代码中的作用及其实现细节。

本文深入探讨了Verilog语言中scope的概念及其在IVerilog编译器中的实现方式,包括module、task、function等不同类型的scope,并详细介绍了这些scope在代码中的作用及其实现细节。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1420

1420

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?