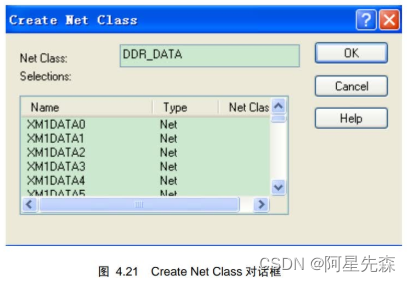

弹出Create Net Class对话框,如图4.21所示。输入名称DDR_DATA,点击OK关闭对话框。

建立DDR_ADDR的过程也一样,同时选中网络XM1ADDR0-XM1ADDR15,XM1CASN、XM1CKE0、XM1CSN0、XM1RASN、XM1WEN后右键Create->Net Class。其它就不重复了。

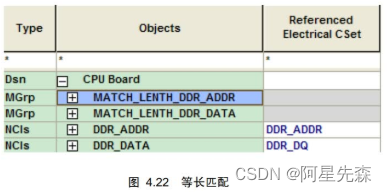

然后将上一步建立的两个电气规则DDR_DQ,DDR_ADDR分别应用到DDR_DATA,DDR_ADDR两个Net Class上。在右边的工作表区内,分别点击DDR_DATA,DDR_ADDRNCls的Referenced Electrical CSet编辑框,分别选择DDR_DQ,DDR_ADDR。这时候,约束管理器自动建立了两个Mach Group(MATCH_LENTH_DDR_ADDR,MATCH_LENTH_DDR_DATA),如图4.22所示。

由于CPU的地址线和其它的一些控制信号被两片DDR内存芯片共用,所以还需要建立一个管脚对(Pin Pair)匹配组来约束等长匹配。在右边工作表区内将DDR_ADDR Net Class展开,在XM1ADDR0网络上点击右键,弹出

本文详细介绍了使用Cadence进行PCB设计时的约束管理,包括设置物理线宽、过孔、间距规则以及布线策略。通过创建网络类、设置线宽、间距和过孔参数,确保信号完整性和制板工艺要求。接着讲解了手工布线、区域规则应用、扇出布线、差分布线和等长绕线的步骤。最后,阐述了输出底片文件前的Artwork参数设置、钻孔文件生成和底片文件输出流程,为PCB制造提供准确的输入文件。

本文详细介绍了使用Cadence进行PCB设计时的约束管理,包括设置物理线宽、过孔、间距规则以及布线策略。通过创建网络类、设置线宽、间距和过孔参数,确保信号完整性和制板工艺要求。接着讲解了手工布线、区域规则应用、扇出布线、差分布线和等长绕线的步骤。最后,阐述了输出底片文件前的Artwork参数设置、钻孔文件生成和底片文件输出流程,为PCB制造提供准确的输入文件。

订阅专栏 解锁全文

订阅专栏 解锁全文

820

820

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?