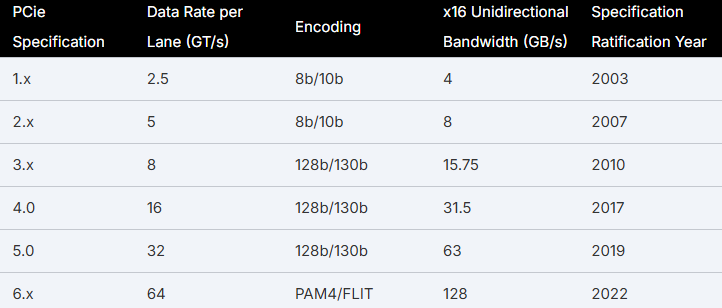

PCIe 的最新版本是第 6 代,即 PCIe 6.0。

通过在高速差分通道中采用 PAM-4作为信号传输方式,PCIe 6.0 实现了通道带宽的翻倍。

PCIe:全称为 Peripheral Component Interconnect Express,即 “高速外设组件互连标准”,是一种用于计算机内部组件(如显卡、固态硬盘、网卡等)之间数据传输的高速串行总线标准。

PCI-SIG:PCI-SIG(外围部件互连专业组)是成立于1992年的国际标准组织,由英特尔联合IBM、康柏等企业共同创立,负责制定并维护PCI系列总线规范,包括PCI、PCI-X及PCI Express(PCIe)等技术标准 。该组织通过发布设备兼容性规范、实施互操作性测试认证,确保计算机外围设备在电气特性、机械接口和协议层面的统一性。截至2025年,PCI-SIG已推动PCIe标准迭代至7.0版本,传输速率从初代2.5 GT/s提升至128 GT/s,支撑起显卡、存储设备等高速外设的技术演进。PCI-SIG计划在2025年内完成PCIe 7.0最终版本发布,但Live Compliance计划推迟至2028年。

PAM-4:全称为 Pulse Amplitude Modulation with 4 Levels,即 “4 电平脉冲幅度调制”,是一种信号编码技术,通过在单个信号周期内传输 4 种不同幅度的电平来携带更多数据,相比传统的 NRZ(不归零码)技术可在相同频率下实现翻倍的数据传输速率。

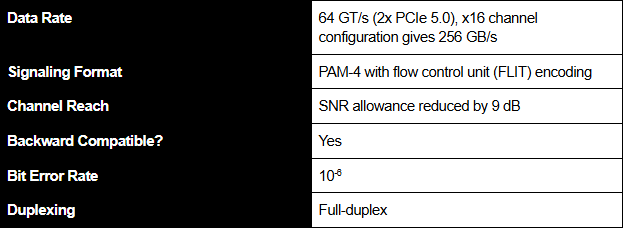

PCIe 6.0 通道的主要性能参数如下,基于 PCI-SIG 于 2022 年 1 月正式发布的 PCIe 6.0 标准版本

PAM-4 与互操作性

如上所述,PCIe 6.0 采用 PAM-4 链路,而 PCIe 5.0 及更早版本的规范则使用 NRZ(不归零码)。尽管信号传输标准仍存在差异,但 PCIe 6.0 设备可通过以两种有效信号电平运行 PAM-4 链路,确保向下兼容性。在 PAM-4 中引入带 4 抽头 FIR 滤波器(有限脉冲响应滤波器)的分布式反馈均衡技术,有助于接收器进行信号恢复,再配合可调节的直流增益,能够补偿高频损耗。

前向纠错(FEC)

与 NRZ 相比,转向 PAM-4 编码会导致误码率(BER)显著升高。因此,PCIe 6.0 中引入了 FEC 技术,以抵消布线通道中更高的误码率。在 PCIe 6.0 标准中,FEC 机制会与循环冗余校验(CRC)协同工作,目标延迟低于 2 纳秒(ns)。仅作对比参考:部分信号传输标准的 FEC 延迟超过 100 纳秒,无法满足 PCIe 技术对带宽和延迟的要求。

PAM-4 信号传输与 FEC 的结合,还助力延长了 PCIe 6.0 通道的传输距离,使其基本与 PCIe 5.0 通道的传输距离持平。这是因为通道中的数据速率虽有所提升,但信号带宽(奈奎斯特频率)并未增加。

流控制单元(FLIT)编码

PCIe 5.0 及更早版本采用嵌入式时钟方案,并搭配固定的 2 位编码。而 PCIe 6.0 通过取消 128B/130B 编码以及数据链路层数据包(DLLP)的额外开销,提升了数据包传输效率。由于 FEC 和 CRC 都需要固定的 FLIT 大小才能执行纠错操作,因此 PCIe 6.0 采用 FLIT 来简化数据管理与纠错流程。

PCIe 6.0 是在 PCIe 5.0 标准基础上的重大升级,但并非所有嵌入式设备都会搭载这一标准。仅每通道 64 吉比特 / 秒(GT/s)的数据传输速率,只有最先进的嵌入式系统才会产生需求。在我接触过的用于传感器融合的高带宽嵌入式设备中,最高也仅采用 28G 和 56G 通道,而这类系统除了军事航空(mil-aero)和数据中心领域外,在其他场景中并不常见。尽管这类高规格系统存在于部分高端应用中,但它们并非推动 PCIe 6.0 需求产生的主要市场因素。

那么,究竟是什么因素推动外设对更高带宽的需求呢?其中两个核心驱动因素与现代数据中心的计算环境相关,而这一环境的发展主要由大型云服务提供商推动。具体的核心应用场景包括:

数据中心人工智能(AI):这类 AI 系统可为嵌入式设备及应用提供支持,或作为服务供其调用

高带宽网络协议接入:如对 800G 以太网(800G Ethernet)的接入需求

固态硬盘(SSD)的技术演进:新一代 SSD 依赖更新版本的 PCIe 标准,以实现对数据中心及边缘服务器存储资源的高效访问

固态硬盘正是推动 PCIe 接口向更高带宽发展的市场驱动因素之一。一个 16 通道(16x)的 PCIe 6.0 接口可在整个接口范围内提供 128 吉字节 / 秒(GB/s)的数据传输速率;将其带宽聚合后与 800G 以太网对比可见,该 16 通道接口能够满足这一先进网络标准所需的 800 吉比特 / 秒(Gbps)吞吐量。得益于 PAM-4 信号传输带来的带宽翻倍机制,PCIe 6.0 的印制电路板(PCB)设计,将沿用许多与其他高速标准相同的高速 PCB 布局和布线技术。

参考:

https://resources.altium.com/p/overview-pcie-60-standard#pam-4-and-interoperability

https://www.rambus.com/blogs/pcie-6/#whatis

1579

1579

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?