3.电气规范

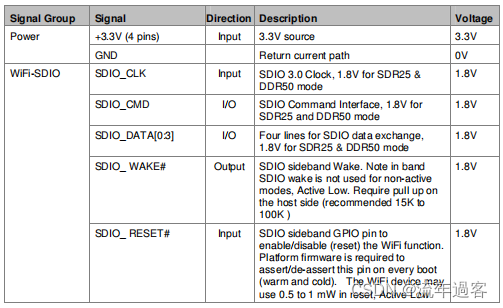

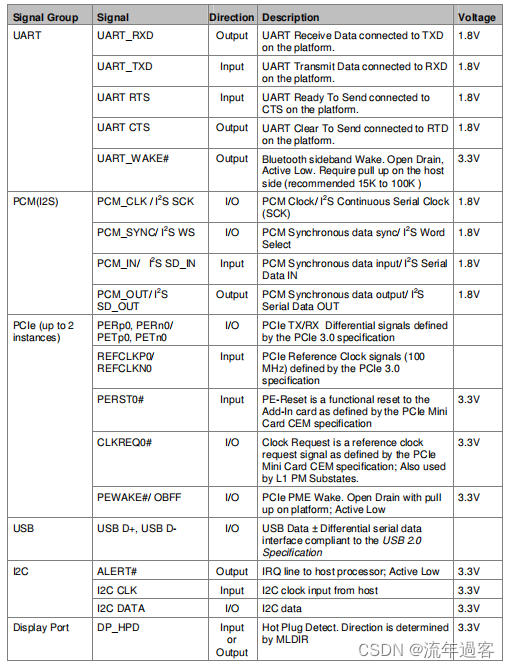

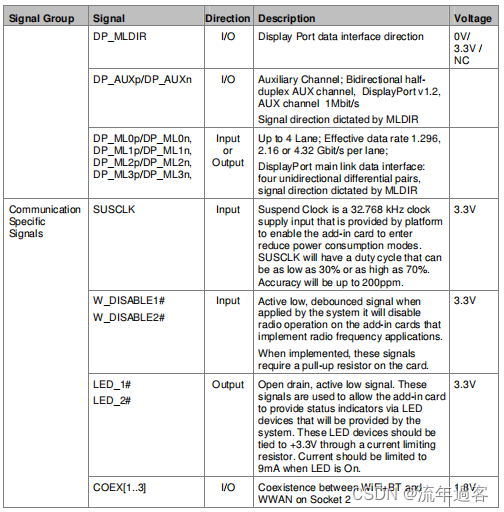

3.1 Connectivity Socket 1 系统接口信号

表15适用于Socket 1-SD和Socket 1-DP输出版本。

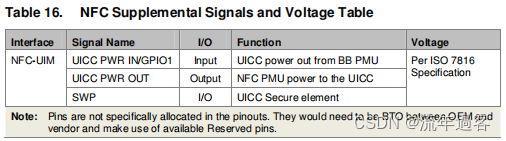

3.1.1.补充NFC信号

当一个SIM设备被用作安全元素时,NFC解决方案可以与表16中列出的附加信号相结合。

3.1.2.电源和地

PCI Express M.2 Socket 1使用一个3.3 V电源。电压源,+3.3 V,预计在系统的备用/暂停状态期间可用,以支持通信卡上的唤醒事件处理。

一些较高频率的信号需要与周围的信号进行额外的隔离,使用交错接地(GND)引脚的概念,分离连接器内的信号。这些引脚应视为普通地脚,在卡设计中立即连接到地平面。

3.1.3.PCIE接口

PCI Express接口支持x1 PCI Express接口(一车道)。一个车道由一个输入和一个输出的高速差分对组成。还支持一个PCI快速参考时钟。有关PCI Express接口信号的功能要求的更多细节,请参阅PCI Express基础规范。

注:车道极性:

- 默认情况下,PETp0和PETn0引脚(连接器的发射器差分对)应连接到系统板上的PCI Express发射器差分对和PCI Express M.2插卡附加卡上的PCI Express接收器差分对。同样,默认情况下,PERp0和PERn0引脚(连接器的接收器差分对)应连接到系统板上的PCI Express接收器差分对以及PCI Express M.2插卡附加卡上的PCI Express发射器差分对。

然而,p和n连接可以反向连接,以简化PCB跟踪路由,并在需要时最小化通孔。所有PCI Express接收器都将自动车道极性倒置作为链路初始化和训练的艺术,并将独立地纠正每个车道上的极性。有关链路初始化和培训的更多信息,请参考PCI快速基础规范的第4.2.4节。

请求说明:链接电源管理

- PCI Express基础规范要求使用实现基于PCI Express的应用程序的PCI Express M.2插件卡来实现链路电源管理状态,包括支持L0和L1(除了主L0和L3状态)。对于PCI Express M.2卡的实现,L0s和L1状态的活动状态PM也应默认启用。有关活动状态PM的更多信息,请参阅PCI快速基础规范的第5.4节。

Socket 1输出提供了一个额外的PCI快速通道。这些额外的PETx1和PERx1信号集可以作为原始PCI快速接口的第二通道,或者,它们可以使用第二组REFCLKx1和相邻保留针上的一组辅助信号来形成完整的第二个PCI快速x1接口。

3.1.4.PCIE辅助信号

辅助信号提供在系统连接器上,以协助实现某些系统级别的功能。PCI Express体系结构不需要这些信号,但诸如PCIExpressM.Card2等特定实现可能需要这些信号。高速信号电压水平与先进的硅工艺兼容。可选的低速信号被定义为使用+3.3V电源,因为它是可用的最低公共电压。大多数ASIC工艺具有与+3.3V兼容的高压(厚栅氧化物)I/O晶体管。+3.3V电源的使用允许PCI快速信号与现有的控制总线结构一起使用,避免了一组缓冲的信号和总线之间的桥梁。

PCI Express M.2卡插件卡和系统连接器支持以下章节中描述的辅助信号。

3.1.4.1.参考时钟

REFCLK+/REFCLK信号用于协助板卡的PCIE接口定时电路的同步。在卡接口处的参考时钟的可用性可以通过第3.1.4.2节中所述的CLKREQ#信号进行门控。当参考时钟不可用时,它将处于停放状态。停车状态是当时钟不是由时钟驱动器驱动,而REFCLK+和REFCLK-都被接地终端电阻拉到地面时。有关参考时钟信号的功能和公差要求的更多细节,请参阅PCIE卡机电规范。

3.1.4.2.CLKREQ#信号

CLKREQ#信号是一个开漏、主动低信号,由PCI快速M.2插I卡功能驱动低,请求PCI快速参考时钟可用(活动时钟状态),以允许PCI快速接口发送/接收数据。CLKREQ#信号的操作由链路控制寄存器中的启用时钟功率管理位的状态决定(偏移量为010h)。禁用时,在向卡施加电源时,应始终维护CLKREQ#信号,但在L1 PM子状态期间可能断言它除外。启用后,CLKREQ#信号可能会在L1链路状态下失效。

CLKREQ#信号也被L1 PM子状态机制所使用。在这种情况下,可以通过系统或插件卡断言CLKREQ#,以启动L1退出。有关实现L1 PM子状态时CLKREQ#信号的功能要求的详细信息,请参阅PCI快速基本规范。每当启用动态时钟管理,并且当一个卡停止驱动CLKREQ# low时,它表示设备已准备好让参考时钟从活动时钟状态转换为停放(不可用)时钟状态。当CLKREQ#被取消断言时,参考时钟不能保证被主机系统停放,并且即使当CLKREQ#被模块取消断言时,模块设计也应容忍一个有效的参考时钟。

在通电时,每当复位时,以及每当需要参考时钟处于活动时钟状态时,板卡必须驱动CLKREQ#信号过低。每当断言PERST#,包括当设备不在D0时,应断言CLKREQ#。需要注意的是,PCI快速设备必须延迟取消确认其CLKREQ#信号,直到它准备好停放其参考时钟。当设备需要将其链路放回L0链路状态时,设备必须能够断言其时钟请求信号,无论参考时钟是否活动或停放。最后,该设备必须能够感知其上游定向接收端口上的电空闲中断,并断言其时钟请求,无论参考时钟是活动的或停放的。

CLKREQ#的断言和取消断言与引用时钟相比是异步的。未实现PCI Express接口的插卡应在卡上不连接。CLKREQ#比标准的开放漏极信号有额外的电气要求,允许它在断电的设备和其他可能通电的设备之间共享。附加要求包括仔细的电路设计,以确保施加于CLKREQ#信号网络的电压不会造成组件损坏,即使没有施加特定组件的电源。此外,设备必须确保不会降低CLKREQ#,除非在所有情况下都有意断言CLKREQ#;包括当相关功能处于D3冷状态时。这意味着任何实现CLKREQ#的组件都必须被设计为:

无电源的CLKREQ#输出电路,如果对CLKREQ#的其他电源施加电压,则不会损坏。

当从其CLKREQ#生成逻辑卸下电源时,未供电输出不存在低接地或任何其他电压的阻抗路径。

这些额外的要求确保了当供电和非供电组件的CLKREQ#输出线结合在一起时,CLKREQ#信号网络继续正常工作。值得注意的是,最常用的开式漏极和三态缓冲电路设计并不满足CLKREQ#的额外电路设计要求。

3.1.4.2.1.通电要求

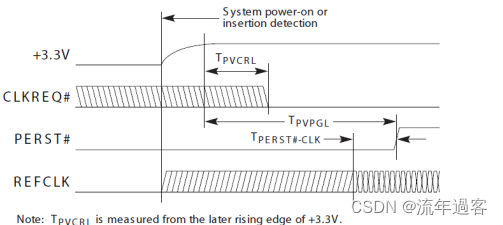

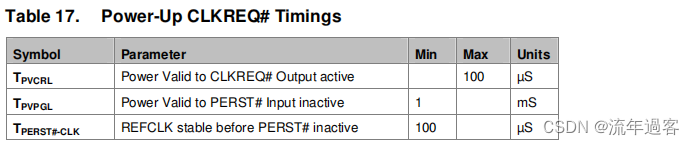

CLKREQ#是响应PERST#断言的断言。通电时,必须由PCI快速设备在延迟(TPVCRL)内确认CLKREQ#,以达到指定的操作限制和PERST#断言(参见图75)。这个延迟是为了让卡上的电源有足够的时间稳定,并在卡启动之前让某些系统功能启动。当断言PERST#时,CLKREQ#不能被取消断言。

在设备通电之前,系统需要让PCI Express设备处于停车时钟状态的参考时钟状态。在设备通电期间,参考时钟的状态未定义,但在PERST#取消断言之前,设置时间TPERST#-CLK必须处于活动时钟状态。表17列出了通电的CLKREQ#计时。

在设备通电之前,系统需要让PCI Express设备处于停车时钟状态的参考时钟状态。在设备通电期间,参考时钟的状态未定义,但在PERST#取消断言之前,设置时间TPERST#-CLK必须处于活动时钟状态。表17列出了通电的CLKREQ#计时。

3.1.4.2.2.动态时钟控制

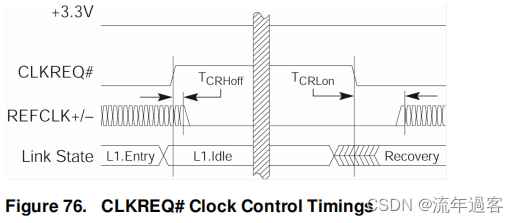

PCI Express设备通电后,当其上游链路进入L1链路状态时,应允许其参考时钟关闭(进入停车时钟状态)。为了实现这一点,设备取消了CLKREQ#(高),并且必须允许参考时钟在延迟内过渡到停车时钟状态(TCRHoff)。图76显示了CLKREQ#时钟控制时序图。要退出L1,设备必须断言CLKREQ#(low)才能重新启用参考时钟。在设备断言CLKREQ#(low)之后,它必须允许参考时钟在转换到活动时钟状态之前继续处于停放时钟的延迟(TCRLon)状态。设备断言CLKREQ#和系统将引用时钟返回到活动时钟状态所需的时间将根据L1恢复的其余部分进行序列化。当设备报告其L1退出延迟时,必须考虑到这个时间。

当PCI Express设备支持并启用延迟容差报告(LTR)时,设备必须允许参考时钟转换到活动时钟状态可能额外延迟到与LTR机制要求一致的最大值。在此延迟期间,参考时钟必须保持停车状态。当在延迟后退出停车状态时,时钟必须在400 ns内稳定且有效。

连接到PCI Express设备的所有链路都必须完成到L1的转换。在设备可以取消断言CLKREQ#之前的空闲状态。当该设备检测到任何接收器端口上的电气空闲中断时,该设备必须断言CLKREQ#。设备必须确认CL

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4130

4130

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?