内嵌函数

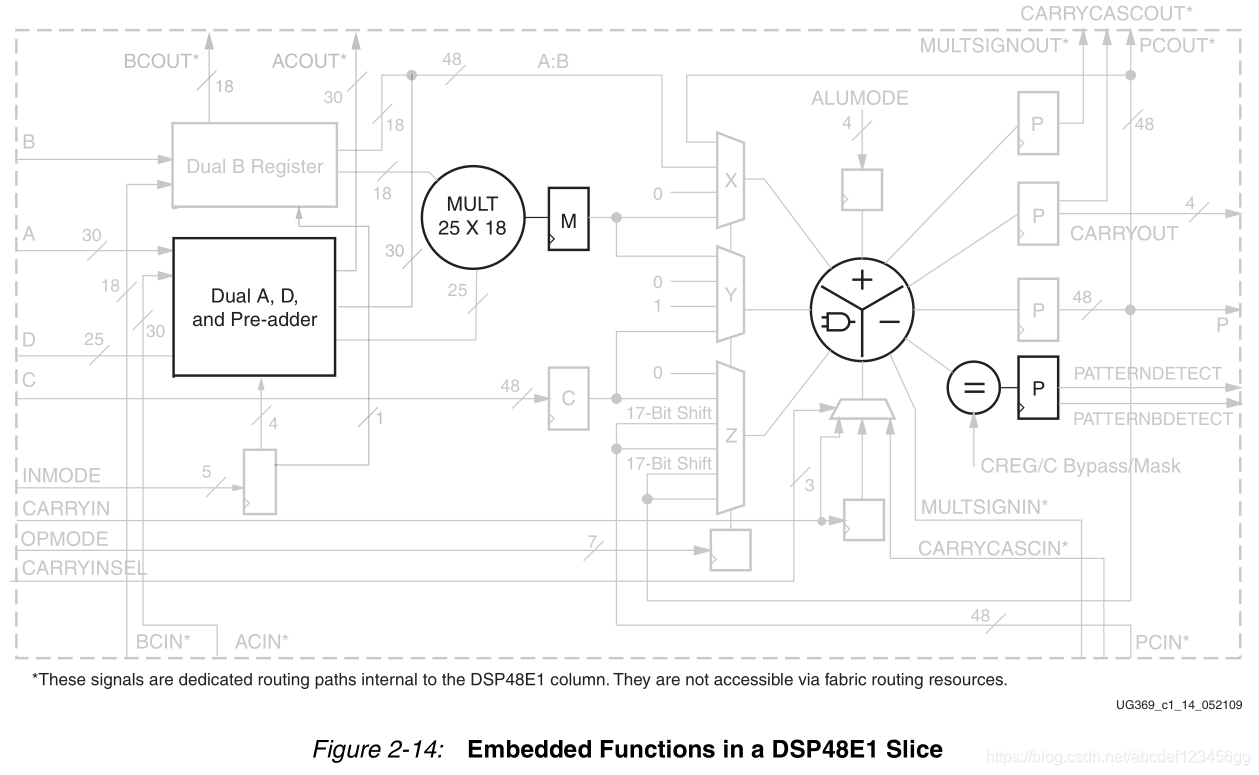

7系列器件的嵌入式功能包括25×18乘法器、加法器/减法器/逻辑单元和模式检测器逻辑.

预加

7系列FPGA DSP片有一个25位的预加法器,插入到A寄存器路径中(如图2-14所示,展开视图如图2-7所示,30页)。有了预加法器,可以在加法器之前进行预加或预减。由于预加法器不包含饱和逻辑,设计人员应该限制输入操作数为24位2的补码符号扩展数据,以避免算术运算期间溢出或下溢。可以选择绕过预加法器,使D成为乘数的新输入路径。当不使用D路径时,可以在驱动乘法器之前否定A pipeline的输出。有多达10种工作模式,使这个预加器块非常灵活。

在方程2-2中,A和D通过预加/减器初始相加。然后将预加法器的结果与B相乘,将相乘的结果添加到C输入中。这个方程有助于有效的对称滤波器。

Adder/Subtracter Output = C ± ( B x ( D ± A ) + Cin )

二进制补码乘数

图2-14中的DSP48E1片中的2的补数乘数接受25位2的补数输入和18位2的补数输入。该乘法器产生两个43位的部分乘积。这两个部分乘积在乘法器的输出处得到一个86位的结果,如图2-15所示。通过17位、右移位、级联输出总线支持乘法器级联以实现更大的结果。右移用于通过正确的位元数对部分乘积进行右对齐。该级联路径馈入Z多路

本文详细介绍了7系列FPGA DSP48E1中的预加法器功能,包括25位预加法器在加法器前的预加或预减操作,以及其灵活的工作模式。此外,还讨论了二进制补码乘法器、加法器/减法器/逻辑单元和单指令多数据模式的应用。

本文详细介绍了7系列FPGA DSP48E1中的预加法器功能,包括25位预加法器在加法器前的预加或预减操作,以及其灵活的工作模式。此外,还讨论了二进制补码乘法器、加法器/减法器/逻辑单元和单指令多数据模式的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4806

4806

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?