文章目录

前言

至于dsp别的使用方法,可以看别的博主:FPGA十年老鸟。这里只总结我用到的加法器和乘法器。

一、加法器,乘法器综合

怎么处理三输入的加法器呢

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

a <= 'b0;

else

a <= b+c+d;

end

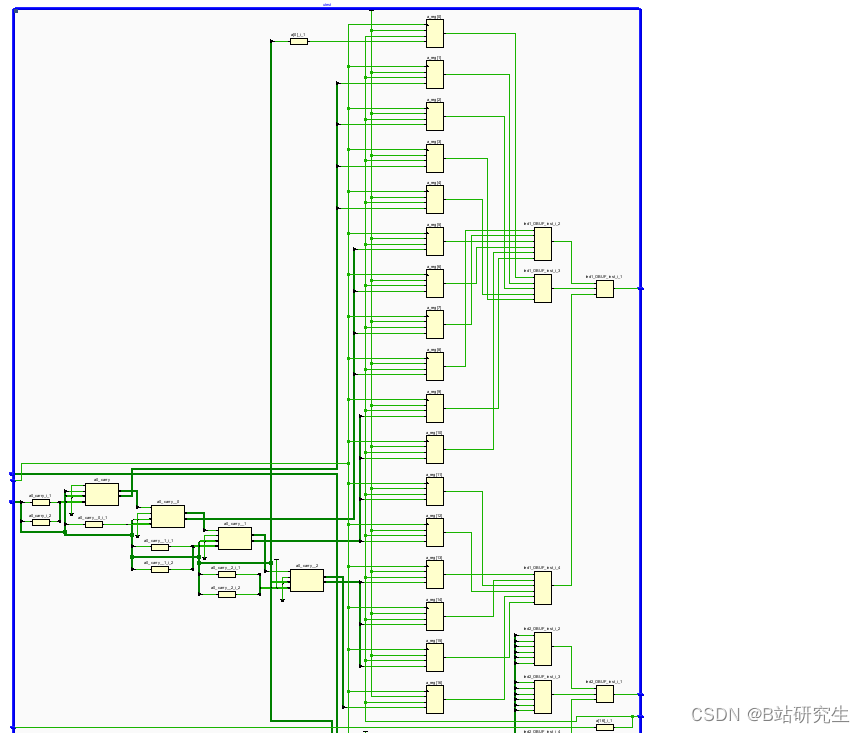

上面的代码综合结果如下图,使用寄存器搭建了两个加法器。

(*use_dsp = "yes"*)module test_adder(

input clk,

input rst_n,

input [15:0] b,

input [15:0] c,

input [15:0] d,

output reg [16:0] a

);

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

a <= 'b0;

else

a <= b+c+d;

end

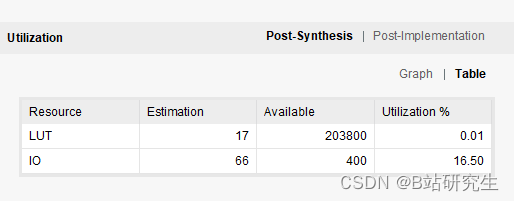

上面代码综合图如下图,注意添加了(use_dsp = “yes”),使用了2个dsp资源。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?