一.概述

关于keep = "true",don't touch = "true",max_fanout等命令,项目中只是去用,并没有去了解怎么正确的使用,在翻阅了一些资料以后,针对一些问题做了一些仿真,在这里做一下总结 。

二.介绍

1.keep,dont touch

在讲这两个综合属性的使用建议之前,先讲下他们的区别。

(1)mark_debug

保证信号综合不会被优化掉,在网表中能找到。

(2)keep

保证信号不会在布局布线之前被优化,keep不作为网表的属性进行传递,不强迫布局布线保持该信号。

(3)dont touch

防止信号在整个综合实现过程被优化。

综上:dontouch 最严格。

使用建议:

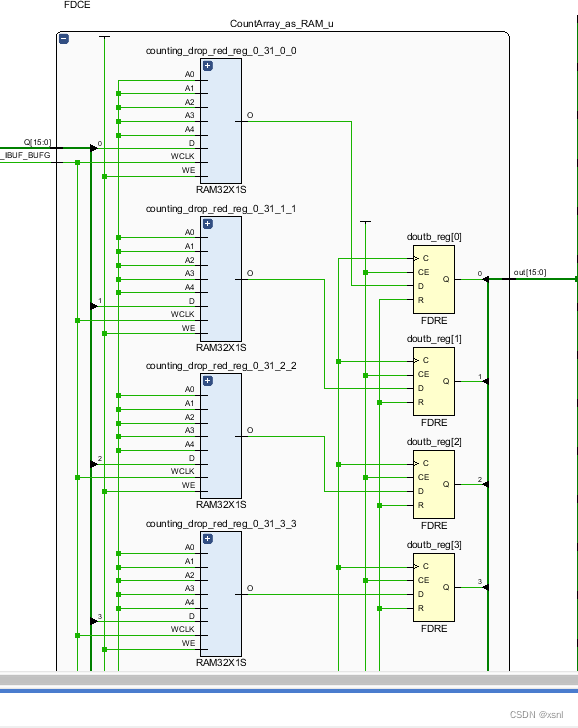

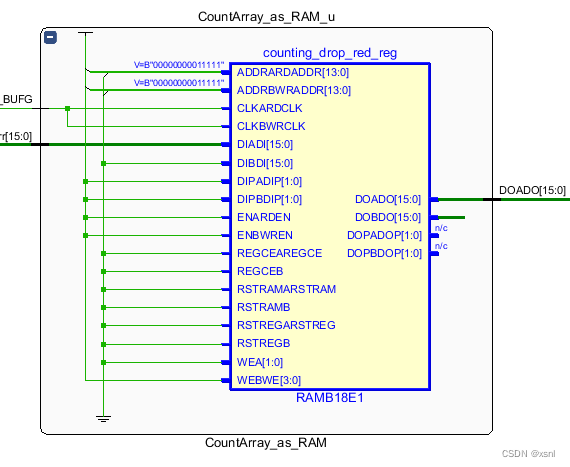

(1)自己写的RAM的输出端口寄存器如果使用了keep属性,将不能推断成RAM。如下图:图二的推断成功,推断成18kb的BRAM。如何写RAM可以看前面博客ram_style的使用。

(2) 有节制的使用这些语句,如不再需要,应将其移除。

(3)不能在inout寄存器上使用keep,dont touch这些属性。

(4)dont touch可以用在层级上,层级中最优化保留,层级边界不会被优化,而且层级中不会发生常数传输。

2.max_fanout

该属性是强制综合通过复制逻辑来满足扇出限制,但是直接输入的信号不能用max_fanout,工具无法处理。max_fanout和dont touch是矛盾的,不能一起使用。查看max_fanout复制的寄存器可以在网表中查看_rep_ _0,_rep_ _1结尾的寄存器。除了使用该属性复制寄存器减少扇出,也可以手动编码生成额外寄存器。

本文详细介绍了FPGA设计中keep、donttouch及max_fanout等综合属性的作用与使用技巧,对比了它们的区别,并给出了具体的应用建议。

本文详细介绍了FPGA设计中keep、donttouch及max_fanout等综合属性的作用与使用技巧,对比了它们的区别,并给出了具体的应用建议。

621

621