前言

最近刚刚开始学习vhdl,外教使用的是modelsim和notepad++的组合,可惜博主用的是vscode,于是尝试探索如何在vscode上写vhdl文件。发现配置相关资料很少,尝试缝合了两篇文章才得以成功,希望其他人少走弯路

配置modelsim

目的是把modelsim的默认编辑器切换为vscode

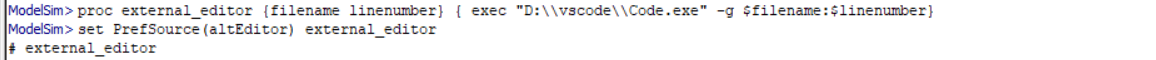

在modelsim-transcript中输入

proc external_editor {filename linenumber} { exec "D:\\vscode\\Code.exe" -g $filename:$linenumber}注意这里的路径要用\\分割,而非win系统常用的\

然后输入

set PrefSource(altEditor) external_editor

显示如上结果表示设置成功

配置成功后modelsim中的代码文件将会默认由第三方编辑器打开

设置编译器

需要把modelsim中的vlog文件夹加入系统的环境变量中以便编辑器随时调用

设置如图即可

文件名随安装的软件版本而不同,作者安装的是64位的版本,于是就是win64

扩展安装和配置

在商店中下载TerosHDL

本文介绍了如何在Visual Studio Code (VSCode) 上配置ModelSim,使其成为默认的VHDL代码编辑器。通过修改ModelSim设置,将模型仿真器与VSCode集成,实现代码的便捷编写。同时,文章提到了添加ModelSim编译器到系统环境变量的步骤,并推荐安装TerosHDL扩展,以获得语法高亮、自动补全和错误检查等功能。

本文介绍了如何在Visual Studio Code (VSCode) 上配置ModelSim,使其成为默认的VHDL代码编辑器。通过修改ModelSim设置,将模型仿真器与VSCode集成,实现代码的便捷编写。同时,文章提到了添加ModelSim编译器到系统环境变量的步骤,并推荐安装TerosHDL扩展,以获得语法高亮、自动补全和错误检查等功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

461

461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?