1 实验任务

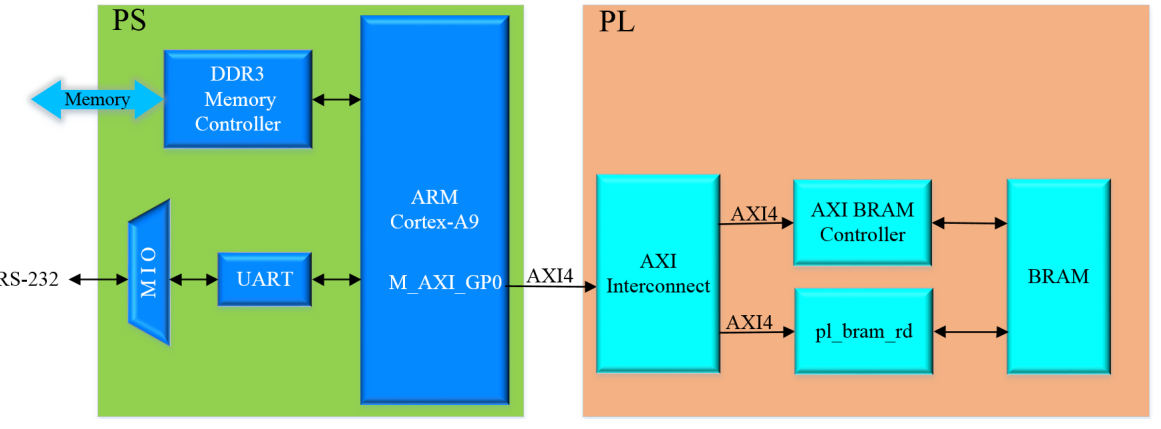

本实验任务是PS将数据写入BRAM,然后从BRAM中读出数据,并通过串口打印出来;与此同时,PS控制PL从BRAM中读出数据,并通过ILA来观察读出的数据与PS侧串口打印的数据是否一致。

2 系统框图

3 硬件设计

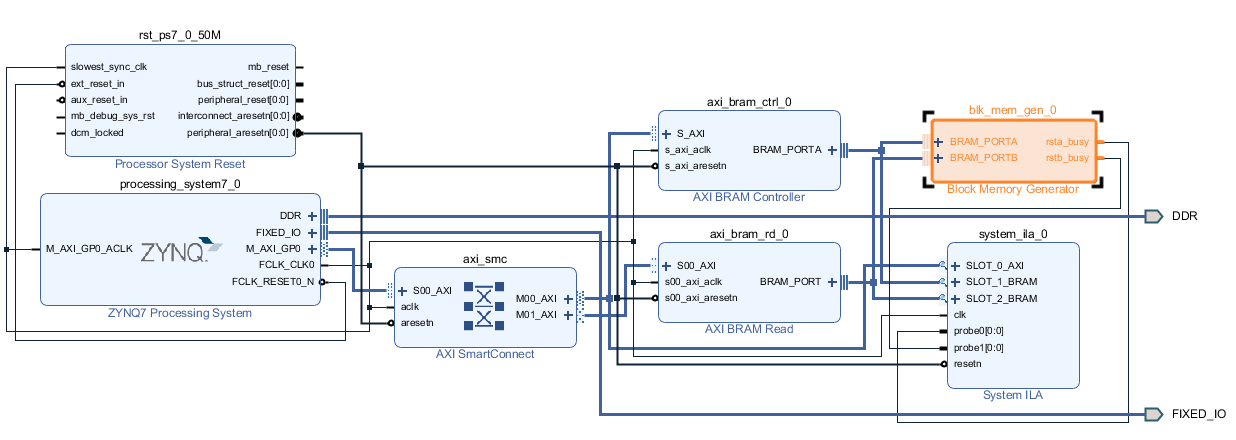

3.1 Block Design

- 添加ZYNQ7 Processing System IP核

- (1)在PS-PL Configuration页面

- 1)勾选FCLK_RESET0_N

- 2)勾选M AXI GP0 interface

- (2)在Peripheral I/O页面

- 1)勾选UART

- 2)正确选择Bank 0和Bank 1的电压

- (3)在Clock Configuration页面

- 1)勾选FCLK_CLK0

- (4)在DDR Configuration页面

- 1)DDR Controller Configuration下,合理配置Memory Type、Memory Part和Bus Width等参数

- (1)在PS-PL Configuration页面

- 添加AXI BRAM Controller IP核

- 添加Block Memory Generator IP核

- 添加带有AXI4-Lite Slave接口的自定义AXI BRAM Read IP核

- 添加System ILA IP核

- 自动连线

3.2 IP核配置

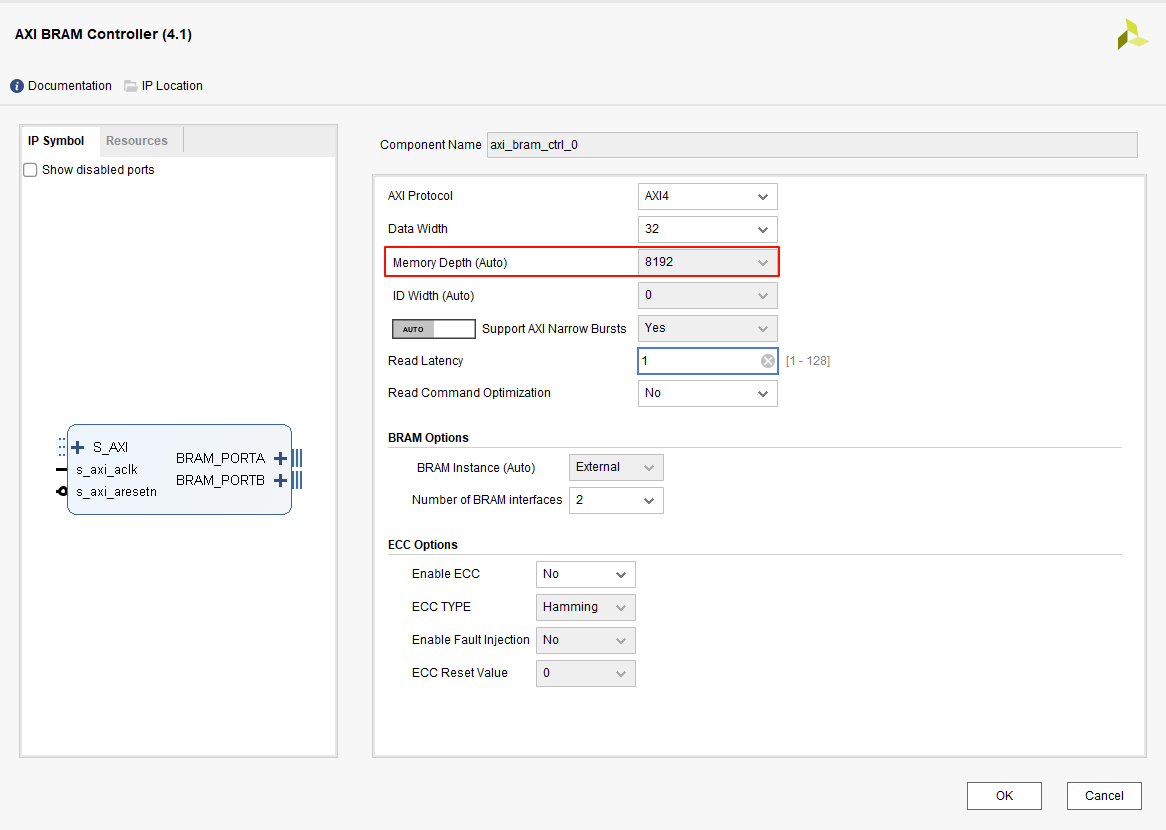

- AXI BRAM Controller IP和Block Memory Generator IP配置

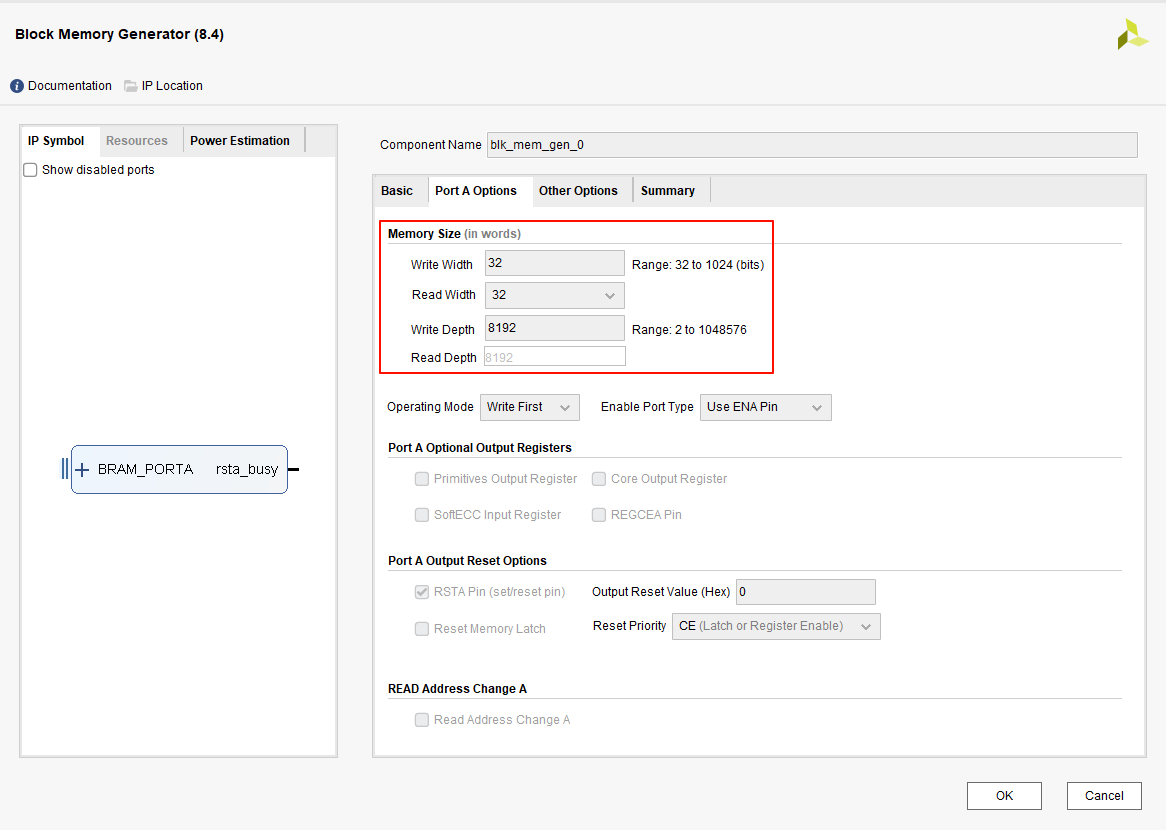

- (1)AXI BRAM Controller作为主设备

- 1)Data Width是可配置的

- 2)Memory Depth是Auto的,由Address Editor中指定的Address Range和Data Width共同决定

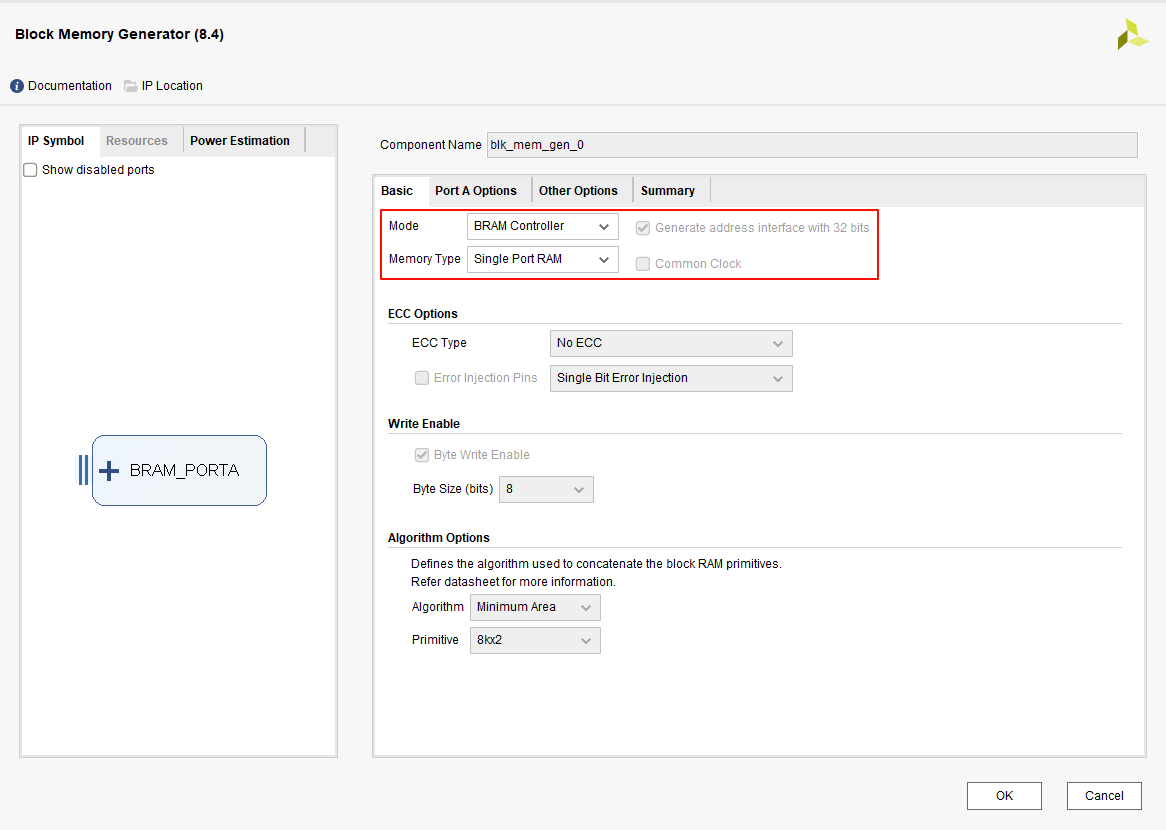

- (2)Block Memory Generator作为从设备

- 1)只有Mode和Memory Type可配置

- 2)其余参数都是在验证设计时通过参数传播自动设置的

- (1)AXI BRAM Controller作为主设备

3.3 注意事项

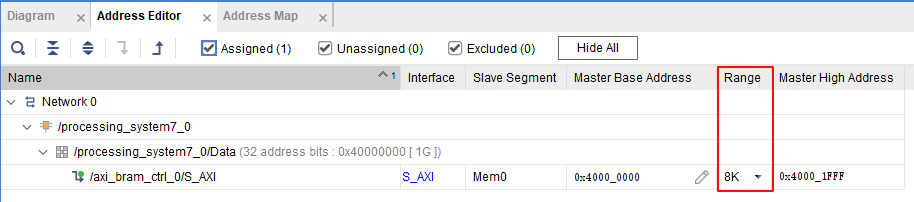

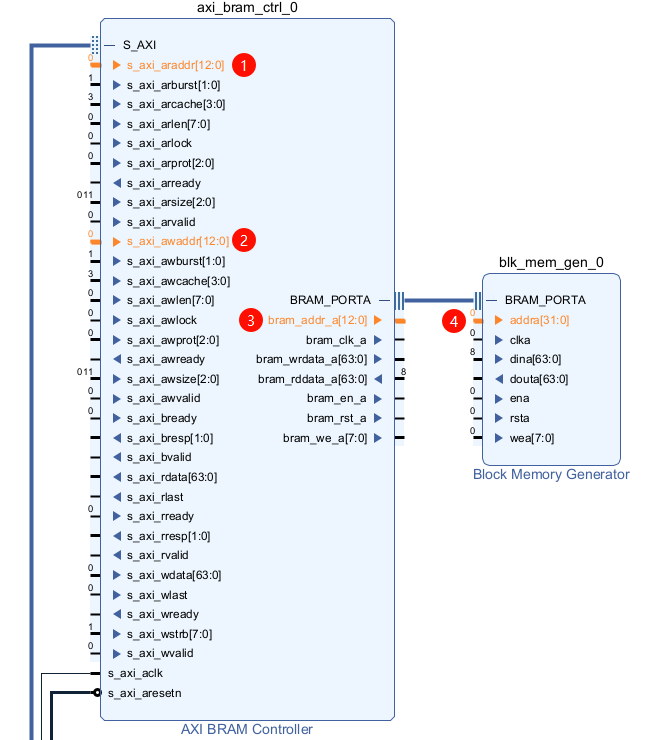

- AXI BRAM Controller和Block Memory Generator地址位宽

- (1)AXI BRAM Controller的S_AXI端口和BRAM_PORT A/B端口的地址位宽由Address Range决定(如下图所示,2^13=8KB)

- (2)Block Memory Generator的BRAM_PORT A/B端口的地址位宽固定为32-bit

3.4 自定义IP核源码

注意:Block Memory Generator在BRAM Controller模式下,其BRAM_PORT A/B端口的addra/addrb地址线上传输的是字节地址(所以,在bram_rd 模块中,数据位宽=32b=4B,地址以4为单位递增)。

`timescale 1ns/1ps

module bram_rd (

//

input wire i_clk,

input wire i_rst_n,

input wire i_bram_rd_ena,

input wire [31:0] i_bram_rd_adr,

input wire [31:0] i_bram_rd_len,

//

output wire o_bram_clk,

output wire o_bram_rst,

output wire o_bram_en,

output wire [ 3:0] o_bram_we,

output wire [31:0] o_bram_addr,

output wire [31:0] o_bram_din,

input wire [31:0] i_bram_dout

);

//***********************************************************************************************

// Constant Functions

//***********************************************************************************************

//***********************************************************************************************

// Parameter Definitions

//***********************************************************************************************

localparam BRAM_RD_IDL = 3'b001;

localparam BRAM_RD_JDG = 3'b010;

localparam BRAM_RD_ACT = 3'b100;

//***********************************************************************************************

// Signal Declarations

//***********************************************************************************************

reg bram_rd_ena_r1;

(* MARK_DEBUG = "TRUE" *) reg bram_rd_ena_r2;

(* MARK_DEBUG = "TRUE" *) reg bram_rd_ena_pos;

reg [31:0] bram_rd_adr_r1;

(* MARK_DEBUG = "TRUE" *) reg [31:0]

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?