1.数码管基础知识

LED数码管:它是由多个发光二极管封装在一起的组成的“8”字型器件。

分类:共阴极数码管、共阳极数码管(板载)

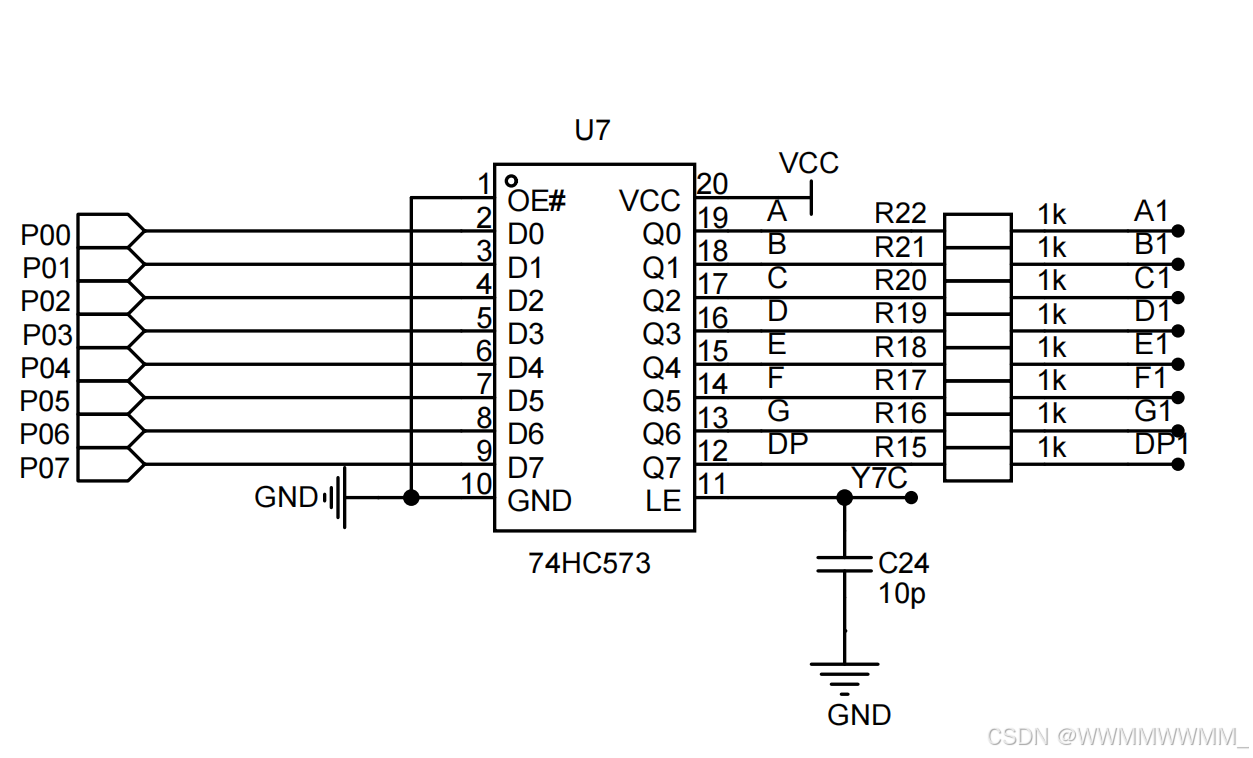

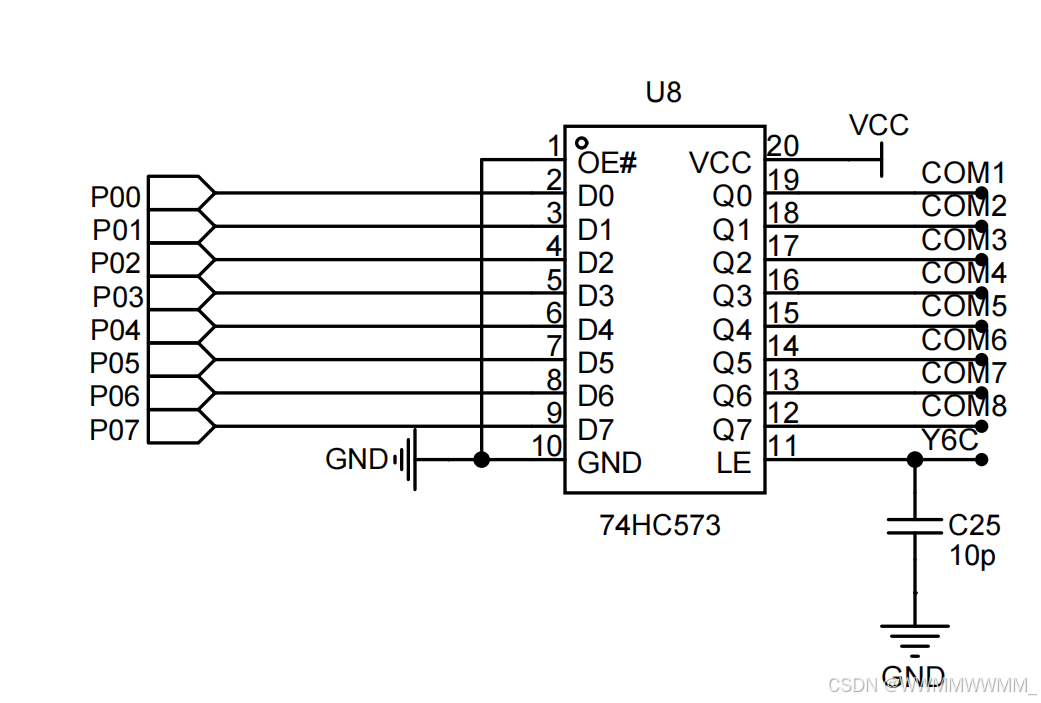

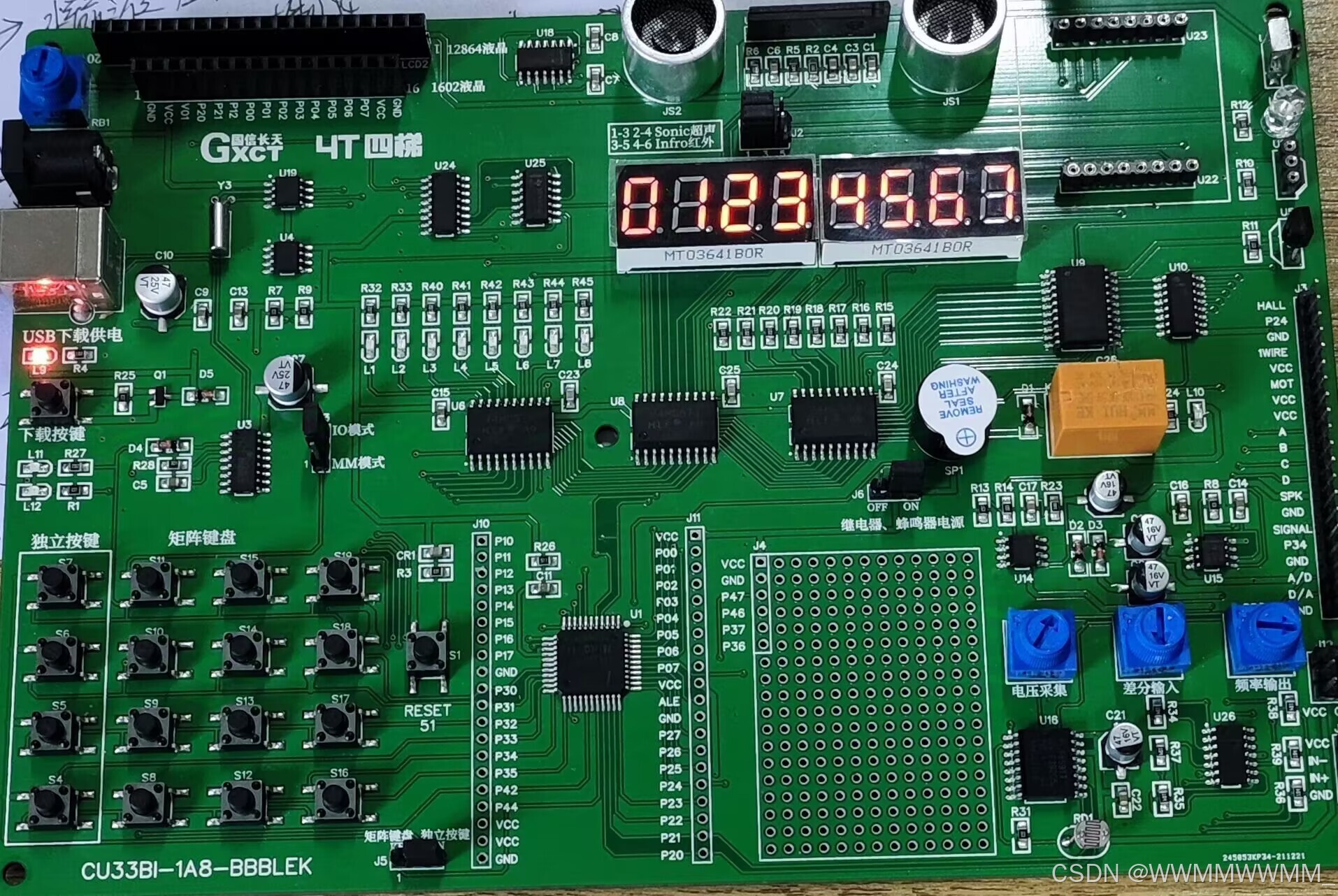

2.板载数码管电路分析

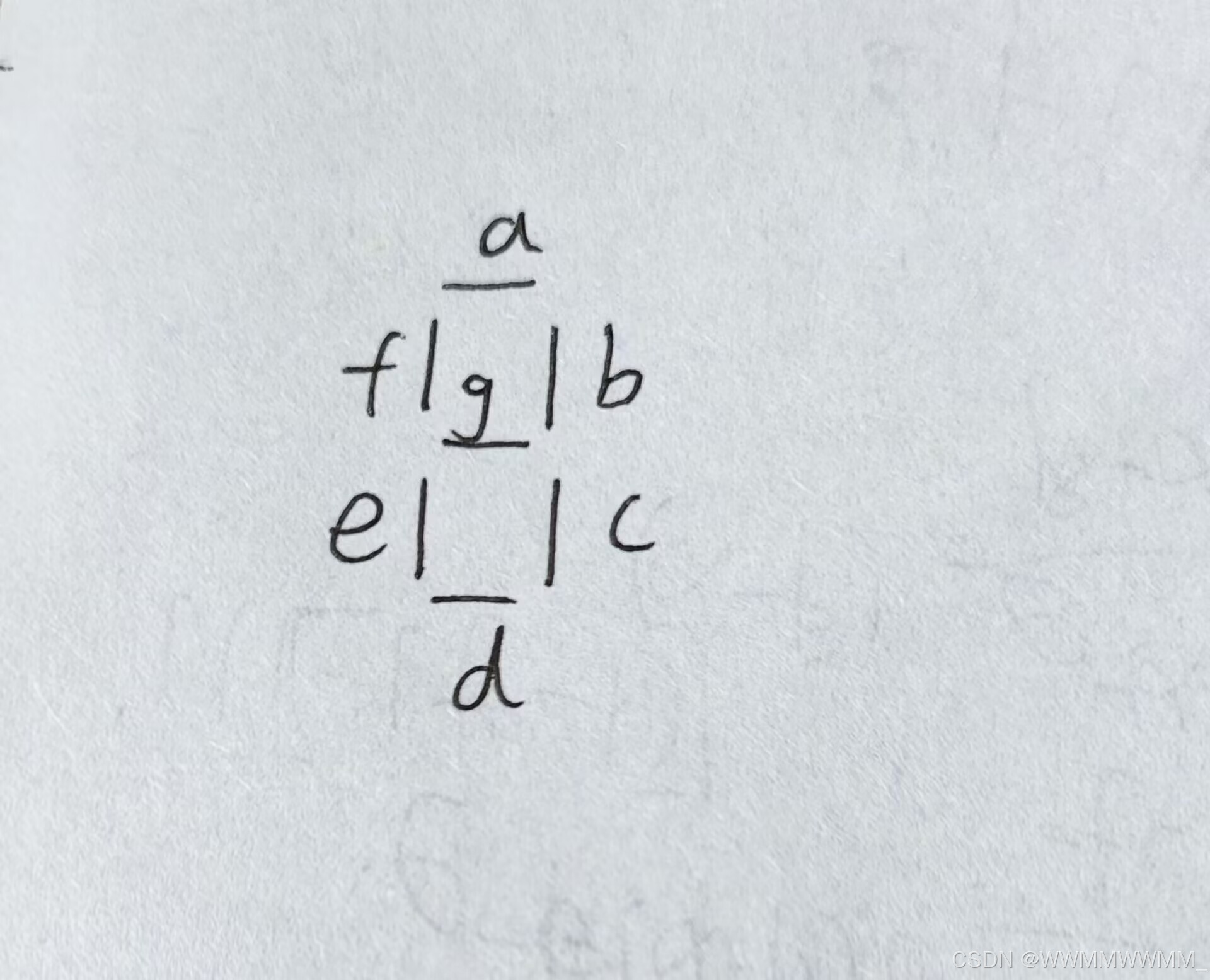

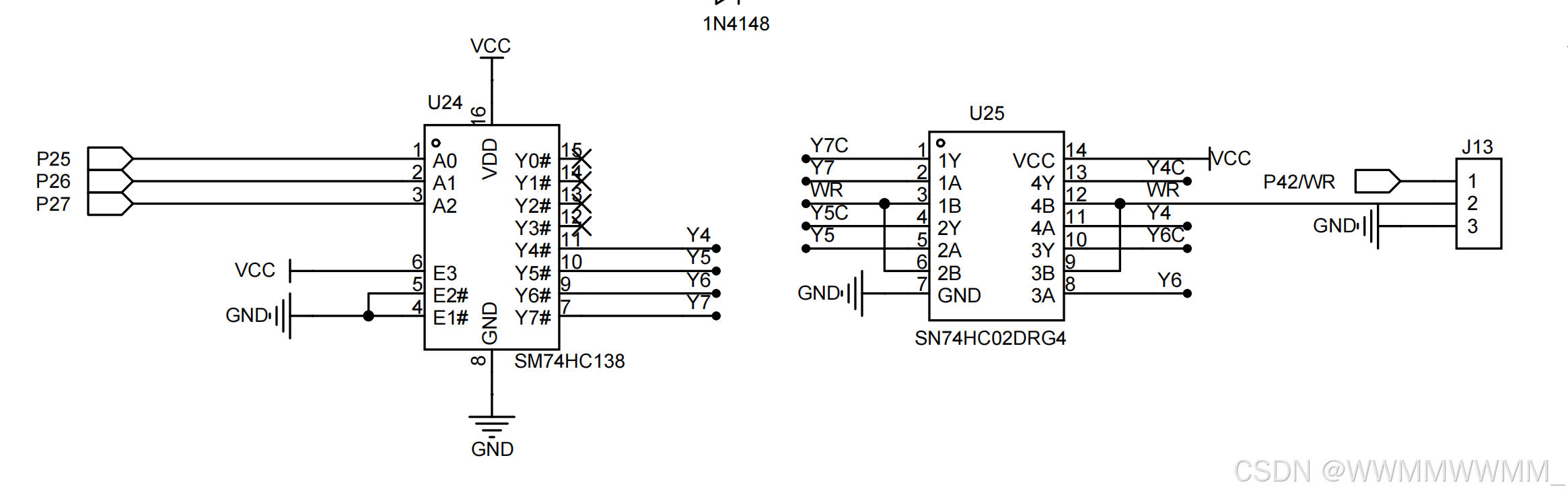

如图所示,板载数码管为共阳极数码管,其中U8锁存器控制COM端,决定了点亮哪一位,U7锁存器控制A、B、C、D、E、F、G、DP来控制所选择的位置显示的字符。

因此,可得到控制数码管的方法:①:P0输出数据(期望显示的数字/英文),选通Y7C段选,关闭锁存器。②:P0输出数据(期望点亮的位),选通Y6C位选,关闭锁存器。

动态显示数码管:利用“视觉残留”,依次点亮单个数码管,使人感觉8个同时点亮。(推荐:单个数码管显示时间为1ms或者2ms)

3.利用动态显示法实现显示“01234567”

#include <STC15F2K60S2.H>

#include <intrins.h>

#include "system.h"

#include "Delay.h"

#include "Device.h"

//定义数码管所显示的字符对应的数组

u8 smg_code[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x00,0x3e,0x73};

HexToBin led_ctrl,uln_ctrl;

//系统初始化函数:关闭蜂鸣器、继电器

void vSystem_Init(void)

{

vDevice_Ctrl(0xa0,0);

led_ctrl.hex=0xff;

vDevice_Ctrl(0x80,led_ctrl.hex);

}

void Timer2Init(void) //2ms@12.000MHz

{

AUXR &= 0xFB;

T2L = 0x18;

T2H = 0xFC;

AUXR |= 0x10;

IE2 |= 0x04; //打开定时器2中断

EA = 1; //打开总中断

}

void main()

{

vSystem_Init();

Timer2Init();

while(1)

{

}

}

//数码管显示函数

void vSmg_Display()

{

static u8 i=0;

vDevice_Ctrl(0xe0,~smg_code[i]);

vDevice_Ctrl(0xc0,0x01<<i);

i++;

if(i==8) i=0;

}

void Timer2_Routine(void) interrupt 12

{

vSmg_Display();

}

实际现象:

4.数码管的“鬼影“现象

出现“鬼影” 现象的原因:在操作段选时,上一个COM处于打开状态。

消除”鬼影“现象的方法:在操作段选前,先关闭所有位选。

//数码管操作函数

void vSmg_Display()

{

static u8 i=0;

vDevice_Ctrl(0xc0,0); //在进行段选前,关闭所有位选,以消除鬼影

vDevice_Ctrl(0xe0,~smg_code[i]);

vDevice_Ctrl(0xc0,0x01<<i);

i++;

if(i==8) i=0;

}

3848

3848

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?