前言

在前三期连载中,我们分析了DRV871x-Q1的产品架构、引脚配置和规格参数。本期我们将深入探讨SPI接口版本的寄存器映射和编程方法,这是充分发挥DRV871x-Q1智能化功能的关键。

SPI接口不仅提供了丰富的配置选项,还支持实时状态监测和故障诊断。通过合理的寄存器配置,可以实现精确的电机控制和可靠的系统保护。

SPI通信协议深度解析

通信时序与帧格式

DRV871x-Q1采用标准的SPI协议,具体参数:

-

时钟极性(CPOL):0(空闲时为低电平)

-

时钟相位(CPHA):0(第一个边沿采样)

-

数据位宽:16位

-

最大时钟频率:10MHz

-

字节序:MSB优先

SPI帧结构:

Bit 15: R/W位(0=写,1=读) Bit 14-8: 寄存器地址(7位) Bit 7-0: 数据字段(8位)

通信时序详解

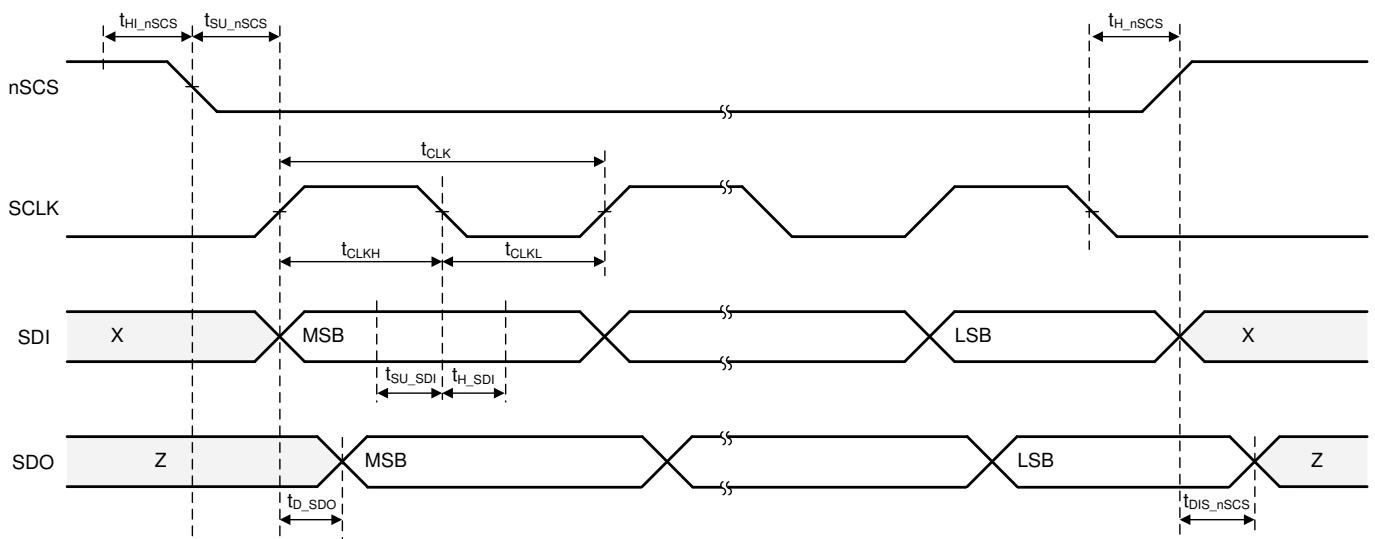

图1:SPI通信时序图

写操作时序:

1. nSCS拉低,开始通信 2. 发送16位命令帧:[0][地址7位][数据8位] 3. nSCS拉高,结束通信 4. 器件内部处理时间:<1μs

读操作时序:

1. nSCS拉低 2. 发送16位命令帧:[1][地址7位][0x00] 3. 接收16位响应帧:[状态位][地址7位][数据8位] 4. nSCS拉高

菊花链模式: DRV871x-Q1支持多器件菊花链连接:

器件数量:最多63个 帧长度:16位 × 器件数量 数据传输:同时写入所有器件

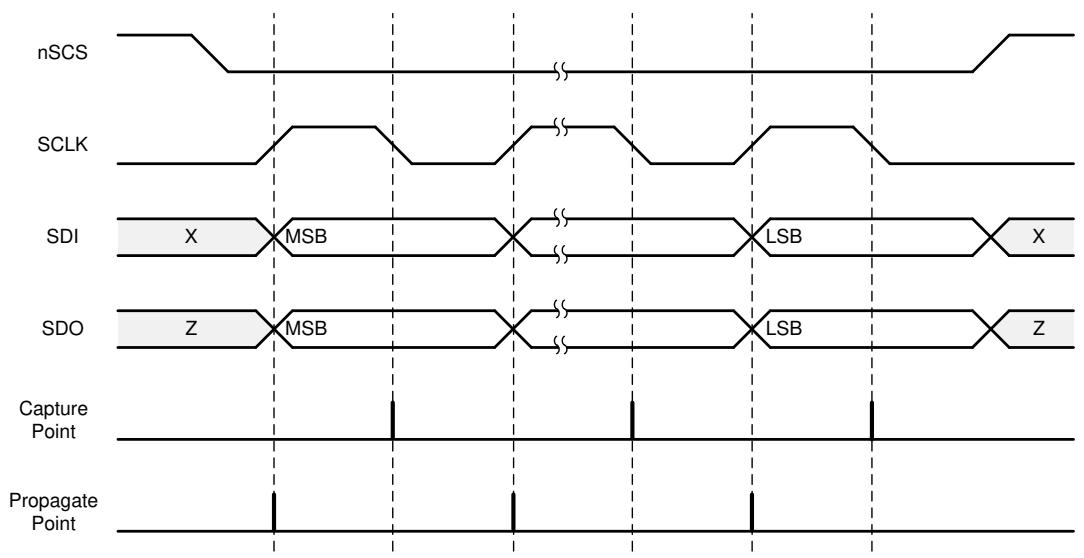

图2:SPI从机时序图

寄存器映射架构

寄存器地址分配

DRV871x-Q1的寄存器按功能分组:

| 地址范围 | 功能分组 | 主要用途 |

|---|---|---|

| 0x00-0x0F | 全局控制 | 器件使能、模式设置 |

| 0x10-0x1F | 驱动控制 | 栅极驱动参数 |

| 0x20-0x2F | 保护设置 | VDS/VGS监测配置 |

| 0x30-0x3F | 电流检测 | 放大器配置 |

| 0x40-0x4F | 状态寄存器 | 故障状态报告 |

| 0x50-0x5F | 诊断功能 | 离线诊断控制 |

寄存器访问权限

只读寄存器:

-

状态寄存器(0x40-0x4F)

-

器件ID寄存器(0x00)

读写寄存器:

-

配置寄存器(0x01-0x3F)

-

诊断控制寄存器(0x50-0x5F)

写保护机制: 某些关键寄存器需要解锁序列:

1. 写入0x5A到UNLOCK寄存器 2. 写入0xA5到UNLOCK寄存器 3. 在100ms内完成配置写入 4. 自动重新锁定

核心配置寄存器详解

器件控制寄存器(0x01 - DEVICE_CTRL)

Bit 7: EN_DRV - 驱动器总使能 0: 禁用所有

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

689

689

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?