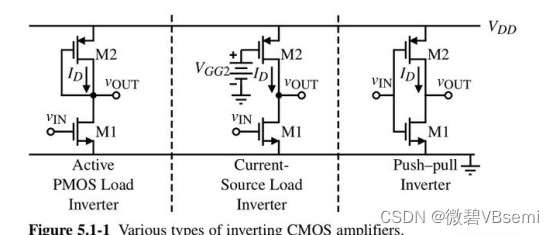

早期时候的工艺仅仅支持NMOS来实现逻辑功能。如今采用NMOS+PMOS,是因为MOS管的占据面积远远小于电阻的面积,并且具有更高的放大倍数。

1.

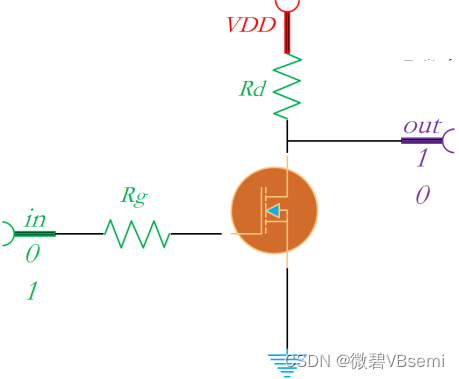

例如下面这个比较典型的非门电路:

当输入高电平时,流过导通NMOS管的电流会很大,这时就需要串入电阻,即Rd进行限流,不过此时消耗的功率已经很大了。

对于那些需要绝对低的漏电流以及一些低功耗电源的应用场景,实际是使用MOSFET来实现基本逻辑门会更好。

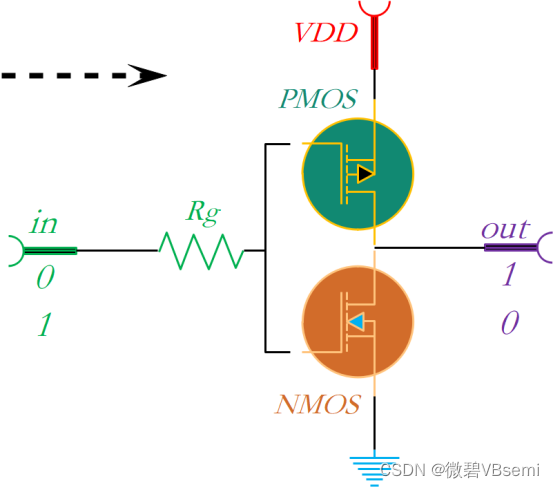

因此上述电路,我们选择用一个PMOS管来替代电阻,就构成了一个互补MOS非门,即CMOS反相器。

当输入高电平时,下管的NMOS导通,导通电阻为mΩ级别,上管PMOS截止,等效mΩ级别,非门输出为低电平,输出电压Vout≈0,而通过两端的电流接近于0,电路的功耗大大降低。

当输入低电平时,下管NMOS截止,上管PMOS导通,非门输出为高电平,输出电压Vout≈VDD,消耗电流取决于out的接收端。CMOS反向器接近于一个理想的逻辑单元,其输出电压接近0或者VDD。

2.

反相器在处理高频信号时一般有几个重要的指标,如果反相器在实现过渡时不够迅速,那么就会导致在处理高频信号时出现失真。

静态电流;电流会直接决定功耗,在单用NMOS/PMOS时,其中一个逻辑态电流一直是通的,而CMOS只有在过渡时会有短暂的大电流,在稳态时没有 显著电流;

VTC性能:即放大倍速、阈值电压,抗噪音能力、过渡区域坡度等等;

元件大小:在集成电路中,电阻相比之下会更占据空间,因此在考虑各方面性能时,CMOS反相器会是不二之选。

总的来说,当只用一个MOS管时,就需要上拉电阻,但这样会导致结构较大,静态功耗也大。而当把NMOS和PMOS放在一个基板成对,用CMOS规定PMOS上拉,NMOS下拉,反相器静态工作时总能输出高质量的高低电平,且不依赖于上拉/下拉电阻,并且获得了很低的静态功耗。

1915

1915

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?