Latency

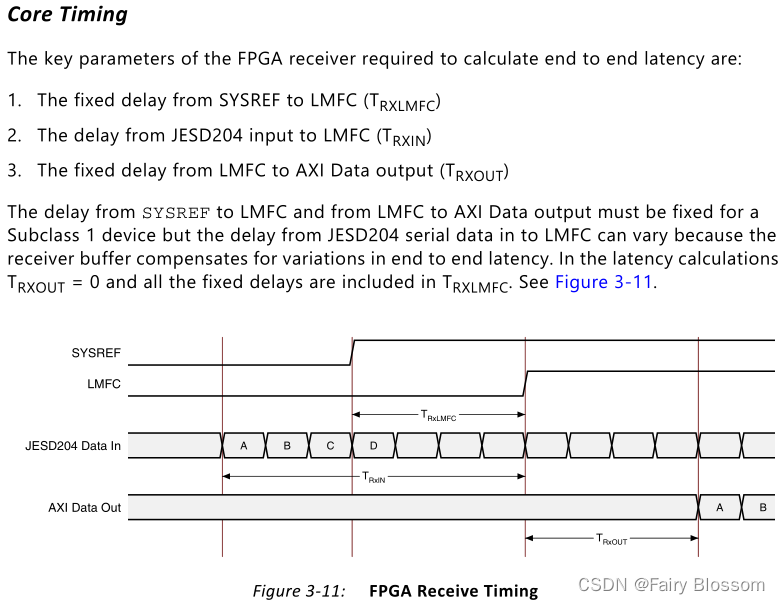

上面关于计算N的公式可不可以理解为:一个传输周期指的是接收方和检测到SYSREF信号到全部将数据接收完毕(N个LMFC后)。(是从接收方的角度来定义T)另一端是发送方输出数据延迟到线路延迟再到接收方接收数据延迟(这些延迟都是相对于SYSREF)外加发送方检测到SYSREF延迟(是从发送方角度来定义)。发送数据要比接收数据用的延迟少,这样才可以保证数据完整接收。大于N*LMFC且小于(N+1)*LMFC表示是在N个之后但是要在N+1个之前。

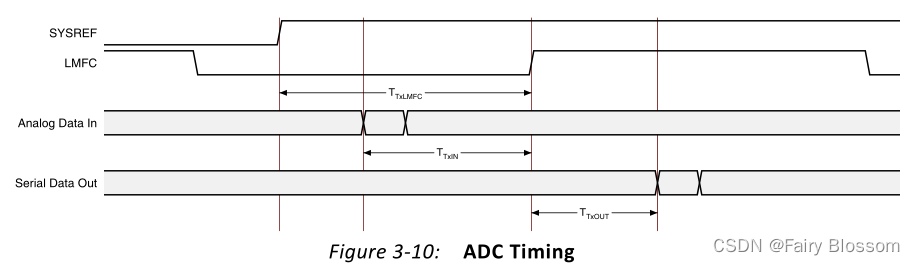

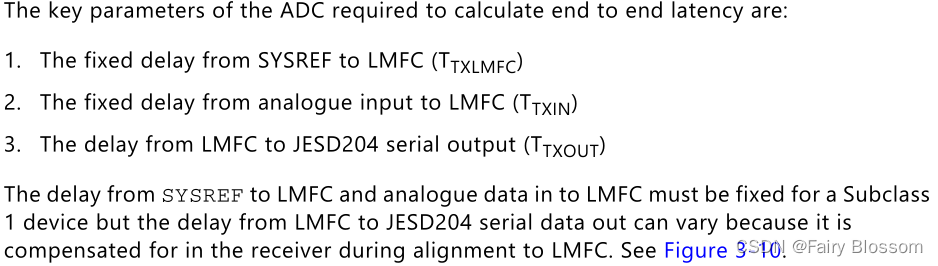

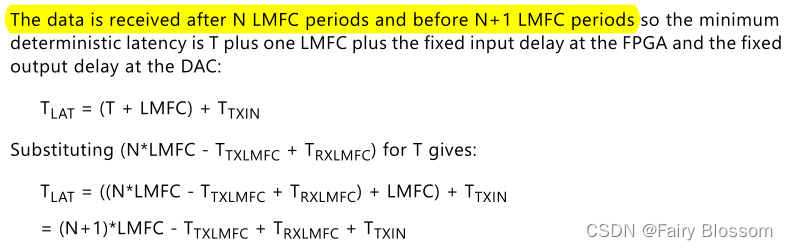

这里提到的是:当经过N个LMFC后在第N+1个LMFC前数据被接收。下面给出了确定性延迟的公式。

关于确定性延迟的确定个人理解是:这个延迟是说接收方检测到SYSREF到全部接收完数据

文章讨论了计算传输延迟的原理,重点在于SYSREF信号与LMFC(LineMaskingFrameCount)的关系。确定性延迟是指从接收方检测到SYSREF到接收完整数据的固定时间间隔。为了确保数据完整性,需要保证发送和接收之间的延迟在N和N+1个LMFC之间。建议通过调整TXLMFC或RXLMFC的延迟来增加余量,提高系统的可靠性。

文章讨论了计算传输延迟的原理,重点在于SYSREF信号与LMFC(LineMaskingFrameCount)的关系。确定性延迟是指从接收方检测到SYSREF到接收完整数据的固定时间间隔。为了确保数据完整性,需要保证发送和接收之间的延迟在N和N+1个LMFC之间。建议通过调整TXLMFC或RXLMFC的延迟来增加余量,提高系统的可靠性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?