知识来源于恩智浦手册——UM10204,文章中讲了I2C总线数据传输,握手以及总线的仲裁系统。

I2C-bus features—— a simple bidirectional 2-wire bus for efficient inter-IC control.

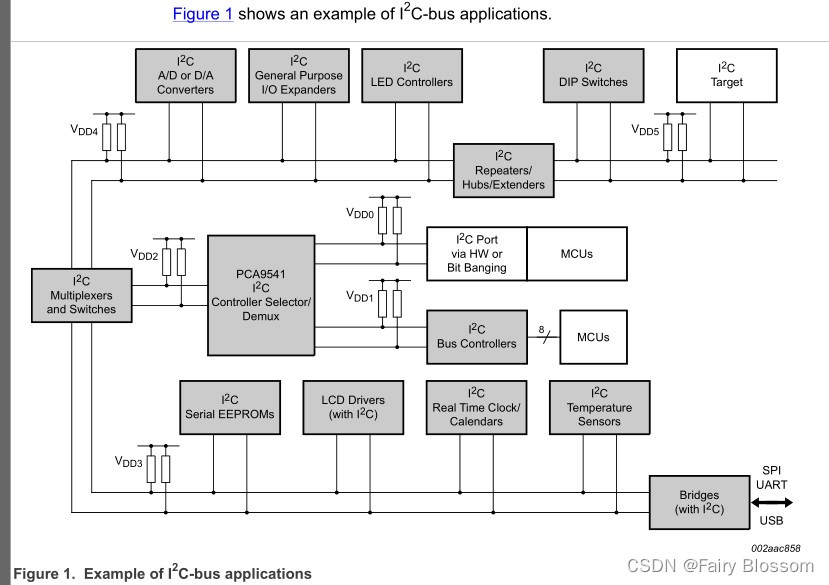

应用:智能控制,通用电路(LCD和LED驱动器,远程I/O端口,RAM, EEPROM,实时时钟或A/D和D/A转换器),面向应用的电路(用于无线电和视频系统、温度传感器和智能卡的数字调谐和信号处理电路)

特征:

- 只需要两条总线:数据总线SDA和时钟总线SCL;

- 连接到总线的设备可以通过唯一的地址进行软件寻址;

- 控制器可以作为控制发射器运行也可以作为控制接收器运行 ;

- 是一个含有碰撞检测和仲裁的多控制器总线;

- 传输模式:8bit,串行,双向;在标准模式下传输100kbit /s,在快速模式下高达400kbit /s,在快速模式Plus下高达1Mbit /s,或在高速模式下高达3.4 Mbit/s进行;

- 在8bit。串行,单向的超快速模式下可以达到 5 Mbit/s;

The I2C-bus protocol

- 手册中给出了几种术语的解释:如果一个微控制器A作为Ccontroller,由他来产生时序,对target进行寻址,不管A作为transmitter还是receiver都由A终止传输。

- 如果总线上有多个控制器,会有仲裁器的参与防止传输冲突。This procedure relies on the wired-AND connection of all I2C interfaces to the I2C-bus.

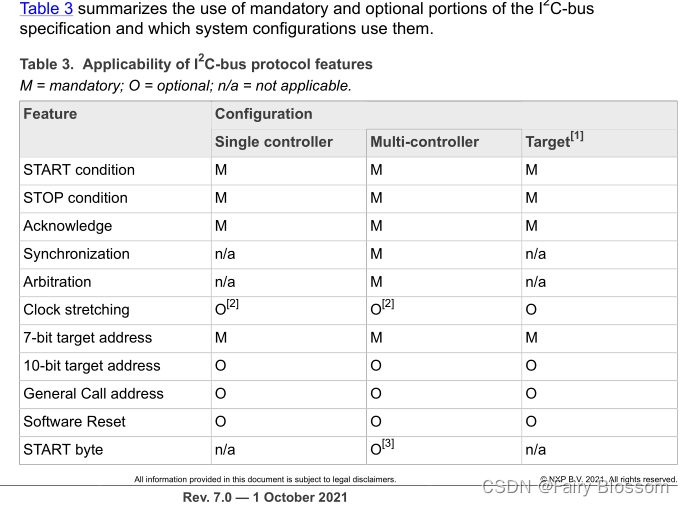

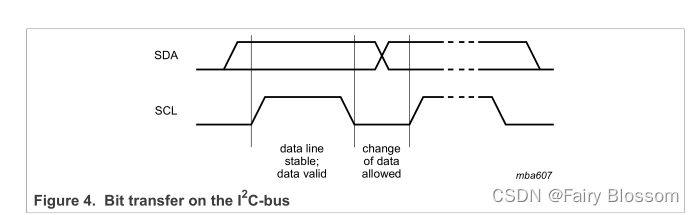

- 对上面的表格解释:Synchronization的作用是为了同步多个控制器的时序;Clock stretching是一些目标的特征(这里的特征相对于文中提到德控制器而言),如果系统中没有目标可以拉伸时钟(保持SCL LOW),控制器不需要设计来处理这个过程;

SDA and SCL signals——通过电流源或者上拉电阻连接至正电压;可实现双向传输

- free状态时。两条线都是高电平;

- 总线电容会限制连到总线的接口数量;

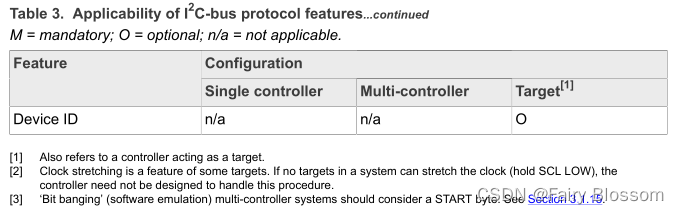

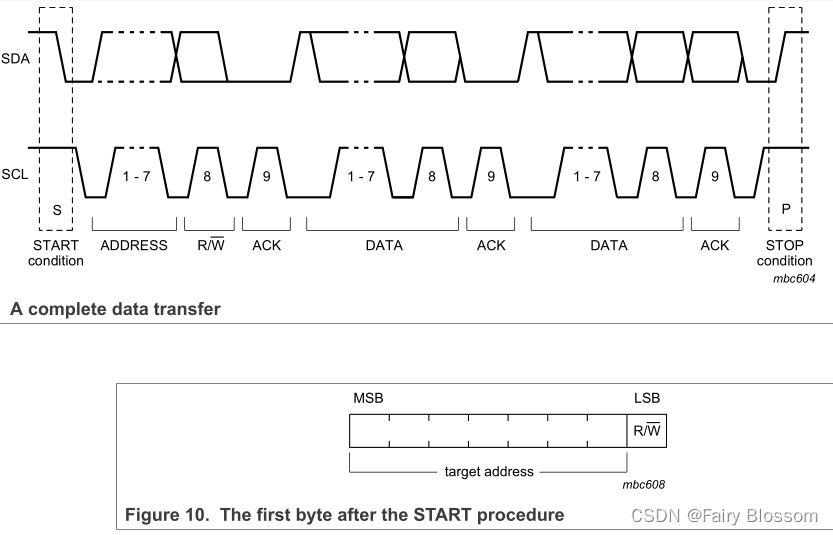

- 数据在SDA上传输时,SDA在SCL的低电平改变,SCL高电平保持;

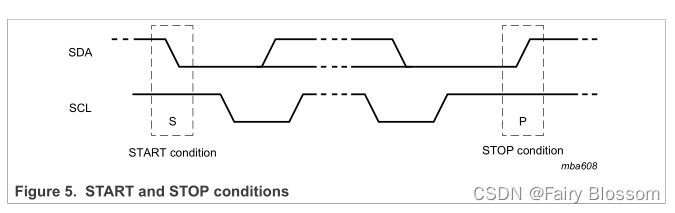

- START and STOP conditions——两个信号都是由控制器控制,START是总线busy,STOP状态总线free。当SCL的高电平SDA出现下降沿时——start,当SCL的高电平SDA出现上升沿——stop。

- Byte format——

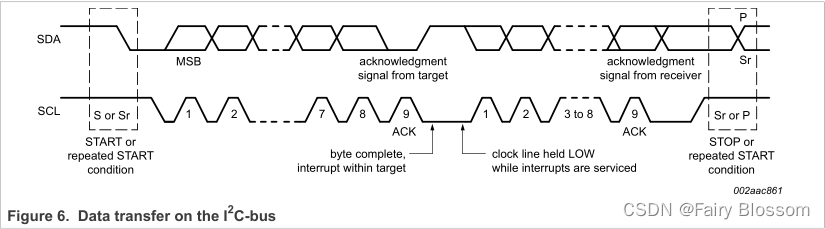

- 传输要求每个字节必须是8位,传输字节数没有限制,传输的每个字节后都跟着一个Acknowedge位

- 数据首先从MSB数据最高位开始传输

- 对上图的一点解释:当发送完一个字节时这里并没有接到STOP因此传输还没有结束,当target不能接收或者发送下一个完整的字节,并且要去执行其他功能,那么它可以保持时钟线SCL LOW以迫使控制器进入等待状态。这一点是上面讲的两条线都有控制器控制的特殊情况。 Data transfer then continues when the target is ready for another byte of data and releases clock line SCL.

- Acknowledge (ACK) and Not Acknowledge (NACK)——

- 意义是接收方向发送发送的信号,用来表示已经成功接收一个字节并等待下一个字节

- 当在上图中的第九个时钟周期SDA出现了高电平,控制器认为是一个不确定信号 NACK,控制器可以发送yigeSTOP或者再次发送START,发生这种情况:

- 总线上没有发送地址的接受者

- 接收器无法接收或者发送

- 接收器得到的数据或命令无法understand

- 控制器-接收器必须向目标发射机发出传输结束的信号。

- Clock synchronization——

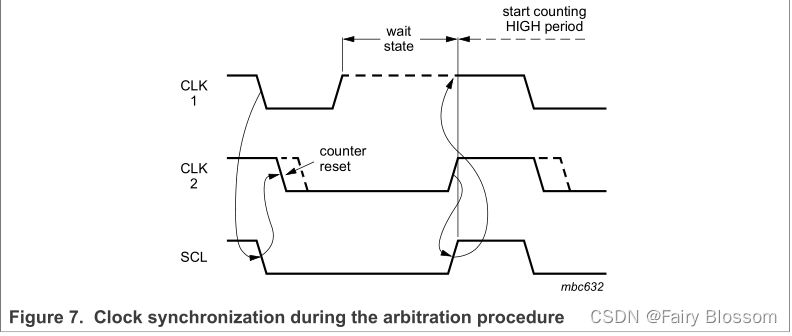

- The SCL line is therefore held LOW by the controller with the longest LOW period(每个控制前都会有个计数器计数低电平维持的时长). Controllers with shorter LOW periods enter a HIGH wait-state during this time.

- 当的所有的控制器都进入了低电平时钟线将会释放进入高电平,所有的控制器开始记录高电平的时长,第一个完成HIGH周期的控制器拉低SCL 。这样就生成了一个同步的SCL时钟,其LOW周期由时钟LOW周期最长的控制器决定,HIGH周期由时钟HIGH周期最短的控制器决定。

- Arbitration

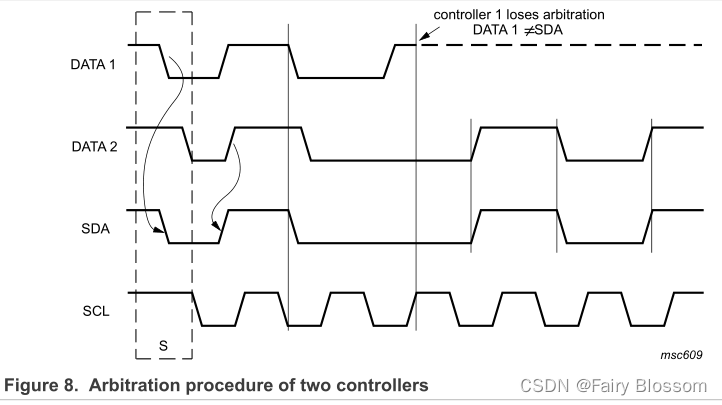

- 图8显示了两个控制器的仲裁过程。根据有多少控制器连接到总线,可能涉及更多的控制器。当产生DATA1的控制器的内部数据电平与SDA线上的实际电平之间存在差异时,DATA1输出将被关闭。这不会影响获胜控制器发起的数据传输。

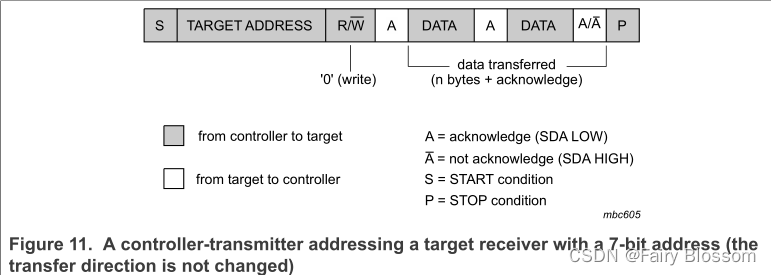

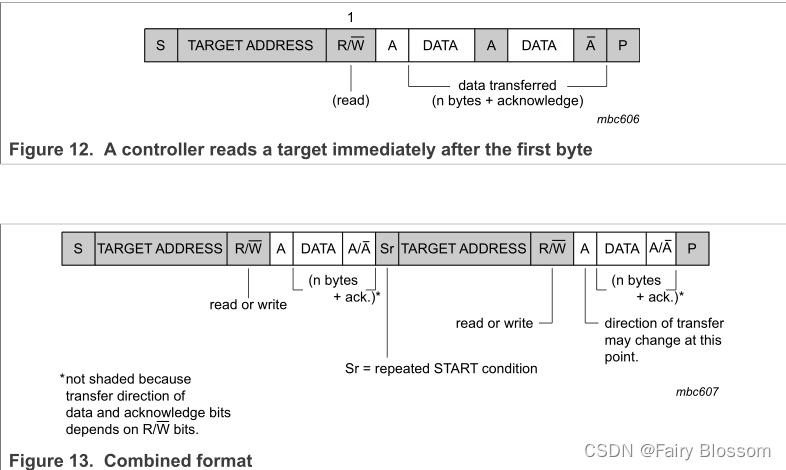

- The target address and R/W bit

- 在进入START状态以后,发送目标地址。

- 目标地址占7位,后面跟着的第9位表示R/W,0是W,1是R

- 对一上三幅图的一些解释:图12中注意当控制器作为接收器目标作为发射器时,第一个acknowledge是目标产生的,之后的acknowledge是控制器产生的。STOP是由控制器产生的,在产生前控制器的最后一个应答是not-acknowledge。图13在传输中的方向改变期间,START条件和目标地址都是重复的,但是R/W位反转。如果控制器-接收器发送了一个重复的START条件,它会在重复的START条件之前发送一个notacknowledge 。

- 总线兼容设备会在START或重复START条件时重置其总线逻辑。

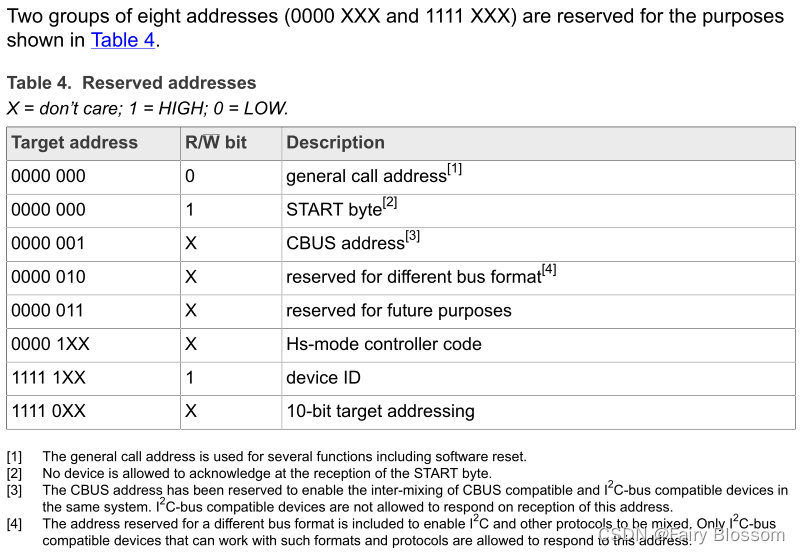

- Reserved addresses(除了厂商设置的地址外还有一些保留地址)——一般用于10bit地址

- Software reset——Following a General Call, (0000 0000), sending 0000 0110 (06h) as the second byte causes a software reset. This feature is optional and not all devices respond to this command.在接收到这个2字节序列后,所有设计用于响应一般调用的地址重置并接收其地址的可编程部分。

- Bus clear

- 如果您的I2C设备有HW复位输入,则优先程序是使用HW复位信号重置总线。

- 如果I2C设备没有HW复位输入,则循环上电以激活强制内部POR (power on reset)电路。

- 如果数据线(SDA)卡在LOW,控制器应该发送9个时钟脉冲。保持总线低电平的设备应该在这九个时钟内的某个时间释放它。如果没有,则使用HW复位或循环电源清除总线。

数据读写过程:

写:控制器发送START->控制器发送7位地址外加读写标志位->控制器释放SDA-匹配到控制器发出的地址的target发送应答->控制器获取SDA总线开始传输8bit数据->控制器释放SDAtarget发送应答确认接收成功->控制器再次获取SDA发送STOP信号

读:控制器发送START-> 控制器发送7位地址外加读写标志位->控制器释放SDA-匹配到控制器发出的地址的target发送应答->target继续占用SDA线向控制器发送8bit数据->target释放SDA控制器获取拉低SDA发送应答acknowledge->target继续占用SDA线向控制器发送8bit数据->target释放SDA控制器获取拉低SDA发送应答non--acknowledge>控制器发送STOP信号

本文详细介绍了I2C总线的特性,包括其作为双向2线制总线用于IC间通信的应用,如智能控制和各种电路。I2C协议涉及数据传输、同步、时钟拉伸、START/STOP条件、字节格式、应答机制和仲裁过程。控制器与目标设备之间的交互通过独有的地址进行,而总线的仲裁系统防止了多控制器冲突。

本文详细介绍了I2C总线的特性,包括其作为双向2线制总线用于IC间通信的应用,如智能控制和各种电路。I2C协议涉及数据传输、同步、时钟拉伸、START/STOP条件、字节格式、应答机制和仲裁过程。控制器与目标设备之间的交互通过独有的地址进行,而总线的仲裁系统防止了多控制器冲突。

5697

5697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?