1. 两个基本结构

entity 顶层名 is

...

end entity;

注:

- 顶层名要与工程名保持一致

- … 中有例:

port(a,b,c:in bit;x:out bit);其表示该实体有三个bit输入,一个bit输出

architecture 实体名 of 顶层名 is

begin

...

end architecture 实体名;

注:

- 实体名可以自己命名,但是顶层名要与上层的名字保持一致

- … 描述了这个器件的内部逻辑结构 有例:

x<=a and b and c;表示a 与b 与c的值赋给了x

2 . 结构描述

architecture 实体名 of 顶层名 is

//在这里添加结构

begin

...

end architecture 实体名;

如例:

entity and_or_logic is

port(in1,in2,in3,in4:in bit;out3:out bit);

end entity and_or_logic;

architecture logicoperation of and_or_logic is

component and_gate(实体名) is //组件1描述

port(A,B : in bit; x : out bit);//

end component and_gate(实体名); //

component or_gate(实体名) is //组件2描述

port(A,B : in bit; x : out bit);//

end component or_gate; //

signal out1,out2:bit; //组件输入信号描述

begin

G1:and_gate port map(A=>in1,b=>in2,x=>out1);//联系

G2:and_gate port map(A=>in3,b=>in4,x=>out2);

G3:or_gate port map(A=>out1,b=>out2,x=>out3);

end architecture logicorperation;

注:

- 其中and_gate和or_gate实体未定义须自己定义

- 在实体and_or_logic 中,我们只是在字面上讲两个基础组件结合起来但是其在文件上并未联系,直接编译会提示找不到实体and_gate or_gate,在此我们需要在project->add/remove files in project 中将前面的项目添加进来。

3.调用库

library ieee;//表示打开库ieee,IEEE库不属于VHDL的标准库

use ieee.std_logic_1164.all;//表示允许许使用IEEE库中STD_LOGIC_1164程序包中的所有内容

entity mux4 is

port(d0,d1,d2,d3,a,b:in std_logic ;q:out std_logic);//std_logic 是长度为bai1的逻辑 与bit 相似,只是bai bit 只能是'0 ’和'1‘ 而 std_logic有以下九种状态:U'——初始值,'X'——不定,'0'——0,'1'——1,'Z'——高阻,'W'——弱信号不定,'L'——弱信号0,'H'——弱信号1,'-'——不可能的情况

end entity mux4;

architecture rtl of mux4 is

signal sel:std_logic_vector(1 downto 0);//std_logic_vector 是标准逻辑矢量

begin

sel<=a & b;

q<=d0 when sel="00" else//选择语句,字面意思

d1 when sel="01" else

d2 when sel="10" else

d3 when sel="11" else

'Z';//高阻

end architecture rtl;

激励文件如下

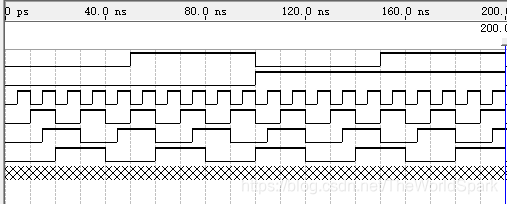

仿真结果:

与预期结果一致

4 .时序逻辑

-

时钟信号 clk

语句:

clk’event and clk='1’表示上升沿

clk’event and clk='0’表示下降沿 -

同步复位/置位信号

process(时钟信号名)

begin

if 时钟边沿表达式 and 复位/置位条件表达式 then

else

[其他执行语句]

end if;

end process;

例:

library ieee;

use ieee.std_logic_1164.all;

entity reg_8 is

port(d:in std_logic_vector(0 to 7);clk :in std_logic; q:out std_logic_vector(0 to 7));

end entity reg_8;

architecture behave_1 of reg_8 is

begin

process (clk)

begin

if(clk'event and clk ='1' ) then q<=d;

end if;

end process;

end architecture behave_1;

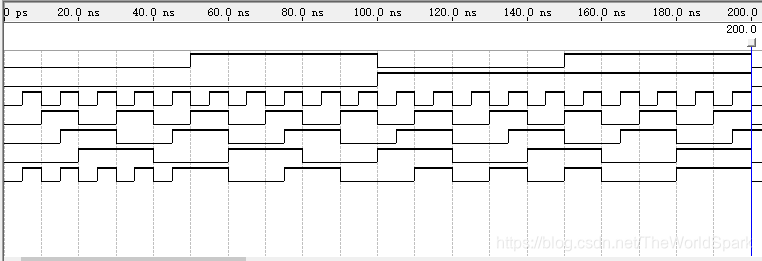

仿真结果如下:

//if语句

1. if (条件) then

执行

elsif (条件) then

执行

else

end if

执行

2. if (条件) then

执行

end if

//when 语句

3. 配合else 选择:

值1 when 条件 else

值2 when 条件 else

值3 when 条件 else

值4;

4.配合case 选择处理

case 条件表达式 is

when 条件表达式值1 => 顺序执行语句;

when 条件表达式值2 => 顺序执行语句;

when 条件表达式值3 => 顺序执行语句;

end case;

//type 自定义常量

4. ...

architecture 实体名 of 顶级实体名 is

type states is (s0,s1,s2);

signal next_state :states;

begin

...

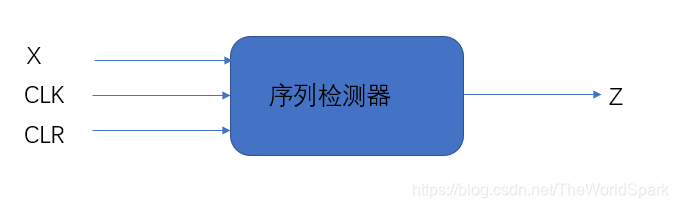

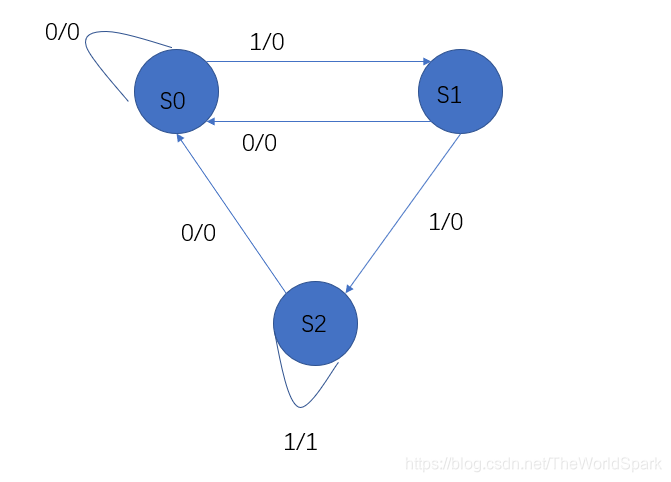

设计一个序列为111的检测器

状态转移表

代码如下

library ieee;

use ieee.std_logic_1164.all;

entity seq is

port(clk,clr,x:in std_logic;z:out std_logic);

end entity seq;

architecture seq_architecture of seq is

type states is (s0,s1,s2);

signal next_states:states;

begin

process(clk,clr)

begin

if clr='1' then next_states<=s0;

elsif clk'event and clk='1' then

case next_states is

when s0=> if x='0' then next_states<=s0;z<='0'; else next_states<=s1;z<='0';end if;

when s1=> if x='0' then next_states<=s0;z<='0'; else next_states<=s2;z<='0';end if;

when s2=> if x='0' then next_states<=s0;z<='0'; else next_states<=s2;z<='1';end if;

end case;

end if;

end process;

end architecture seq_architecture;

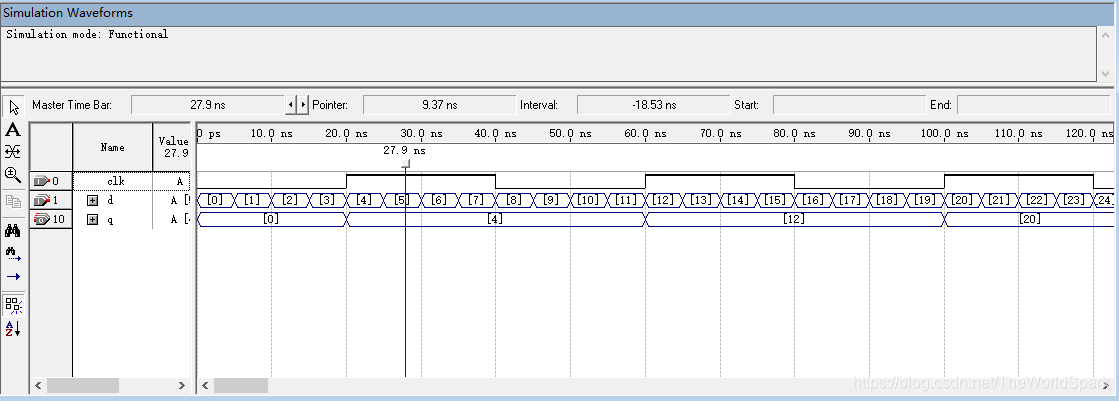

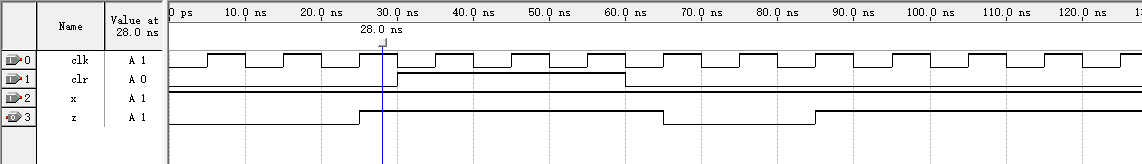

测试激励文件

符合代码设计的功能。

VHDL基础教程

VHDL基础教程

1414

1414

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?