点击此处获取源代码(一码通关)cpu24.circ

本代码为原创首发,创作不易,谢谢支持!

下载链接 https://afdian.com/a/fries

https://afdian.com/a/fries

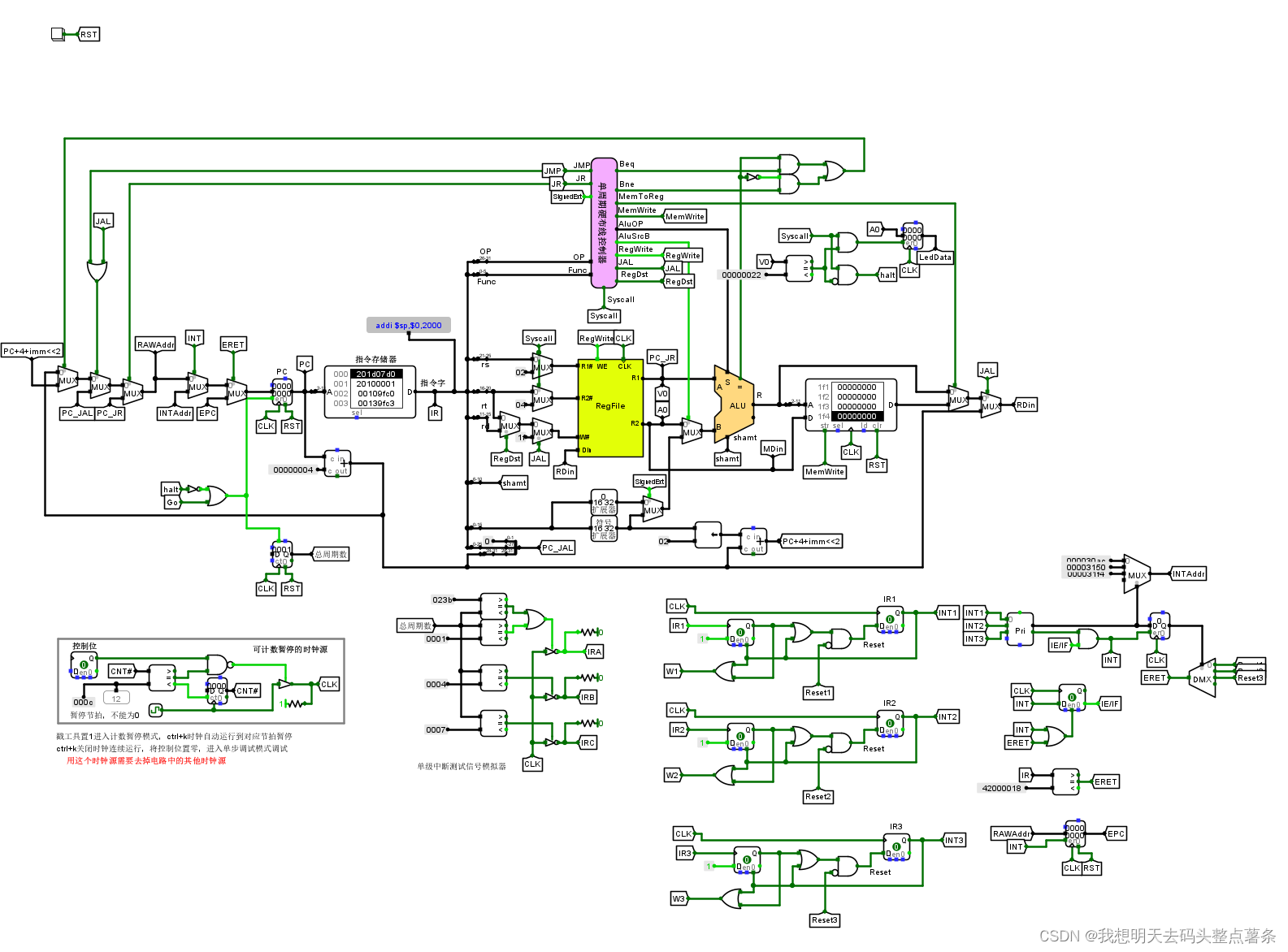

实验成品电路图

MIPS流水CPU设计所有实验见该博客:

目录

实验目的

让学生熟悉中断软硬协同的机制,能够设计支持单级中断的单周期 MIPS CPU。

实验内容

为单周期 MIPS 增加单级中断机制,可支持1、2、3共3个按键中断事件,中断优先级1 < 2 < 3,CPU 执行中断服务程序时不能被其他中断请求中断。

电路框架

cpu24.circ 对应子电路名必须修改为“◇单周期 MIPS+ 单级中断”。

为了方便测试中断,这里增加了三个引脚用于输入中断请求信号,请大家更新整个引脚框,包括按键部分。 注意:可以整体平移引脚框到电路任何位置,但由于电路封装与引脚位置和顺序有关系,所以框内引脚一律不许增删改,哪怕是移动位置调整顺序,改变引脚朝向,也不要在电路中增加额外的引脚,否则测试系统无法测试。

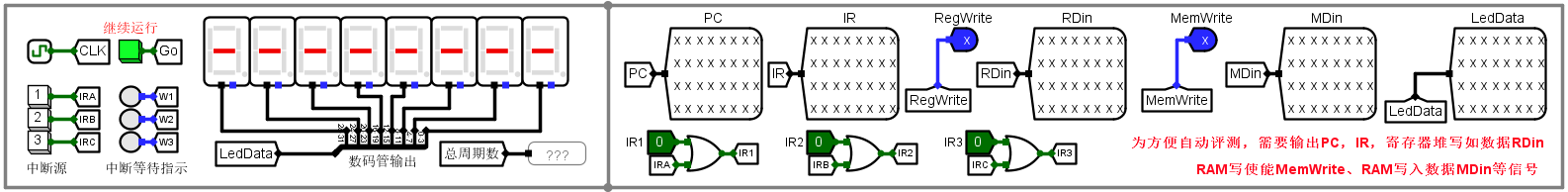

电路监控引脚

| 信号 | 位宽 | 功能描述 |

|---|---|---|

| IR1 | 1 | 输入测试程序的中断请求 IR1,第 3 条指令时中断寄存器 IR 对应位为 1,第 572 拍还会产生一次 |

| IR2 | 1 | 输入测试程序的中断请求 IR2,第 4 条指令时中断寄存器 IR 对应位为1 |

| IR3 | 1 | 输入测试程序的中断请求 IR3,第 5 条指令时中断寄存器 IR 对应位为 1 |

| PC | 32 | 当前节拍程序寄存器 PC |

| IR | 32 | 当前节拍指令字 IR |

| RegWrite | 1 | 寄存器写使能控制信号 |

| RDin | 32 | 寄存器文件写入端口的数据 |

| MemWrite | 1 | 存储器写使能控制信号 |

| MDin | 32 | 存储器写入端口的数据 |

| LedData | 32 | LED 显示输出值 |

待测电路默认封装如下,提交测试前请检查是否一致,如不一致,检查引脚是否修改过,另外可以通过恢复默认封装功能尝试修复。

电路测试

完成设计后,加载 单级中断测试程序.hex 程序,测试功能。确认实验完成正确后,可利用文本编辑工具打开 cpu24.circ,将所有文字信息复制粘贴到 Educoder 平台的 cpu24.circ 文件中,再点击评测按钮即可进行本关测试。平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装。

测试输出结果说明

| # | 信号 | 功能描述 |

|---|---|---|

| 1 | CLKs | 时钟 |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?