一、实验目的

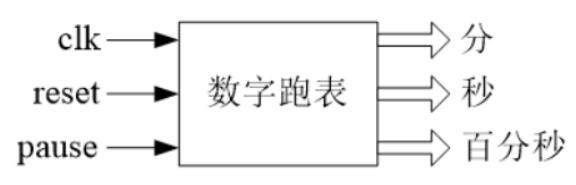

用Verilog HDL设计一个数字跑表,所需引脚和功能如下:

二、实验步骤

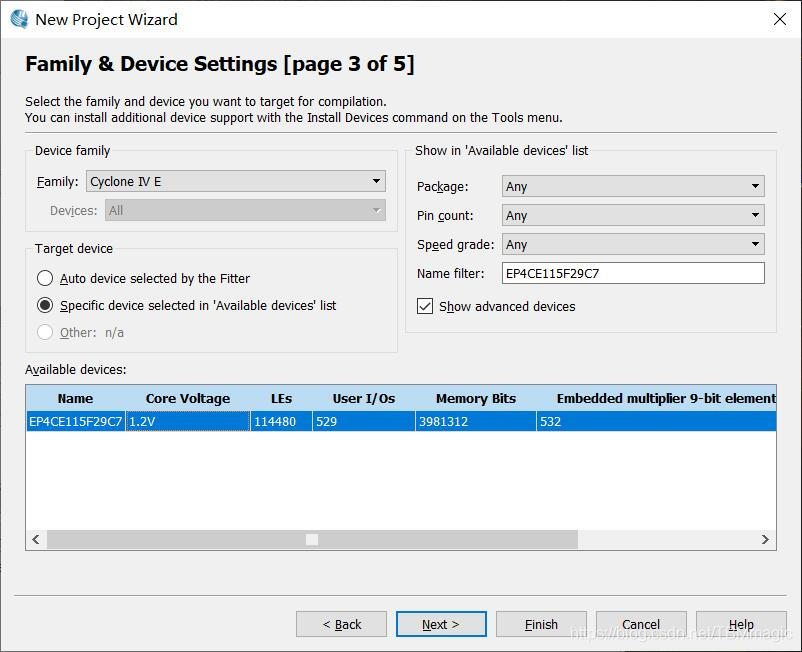

(一)新建工程

在创建好工程名称后,选定芯片类型

(二)添加设计文件

新建Verilog文件,键入代码如下

module n_clk_top(

input clk,

input reset,

input pause,

output reg [3:0] msh, //百秒十位

output reg [3:0] msl, //百秒个位

output reg [3:0] sh, //秒十位

output reg [3:0] sl, //秒个位

output reg [3:0] minh, //分十位

output reg [3:0] minl //分个位

);

reg count1,count2;

//百分秒计数

always @(posedge clk or posedge reset)

begin

if(reset)

本文档详细介绍了使用Quartus进行基于Verilog HDL的数字秒表设计实验,包括实验目的和步骤。实验步骤涵盖新建工程、添加设计文件以及综合分析和功能仿真两个阶段,其中功能仿真部分涉及设置仿真时间和编辑时钟。

本文档详细介绍了使用Quartus进行基于Verilog HDL的数字秒表设计实验,包括实验目的和步骤。实验步骤涵盖新建工程、添加设计文件以及综合分析和功能仿真两个阶段,其中功能仿真部分涉及设置仿真时间和编辑时钟。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5848

5848

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?