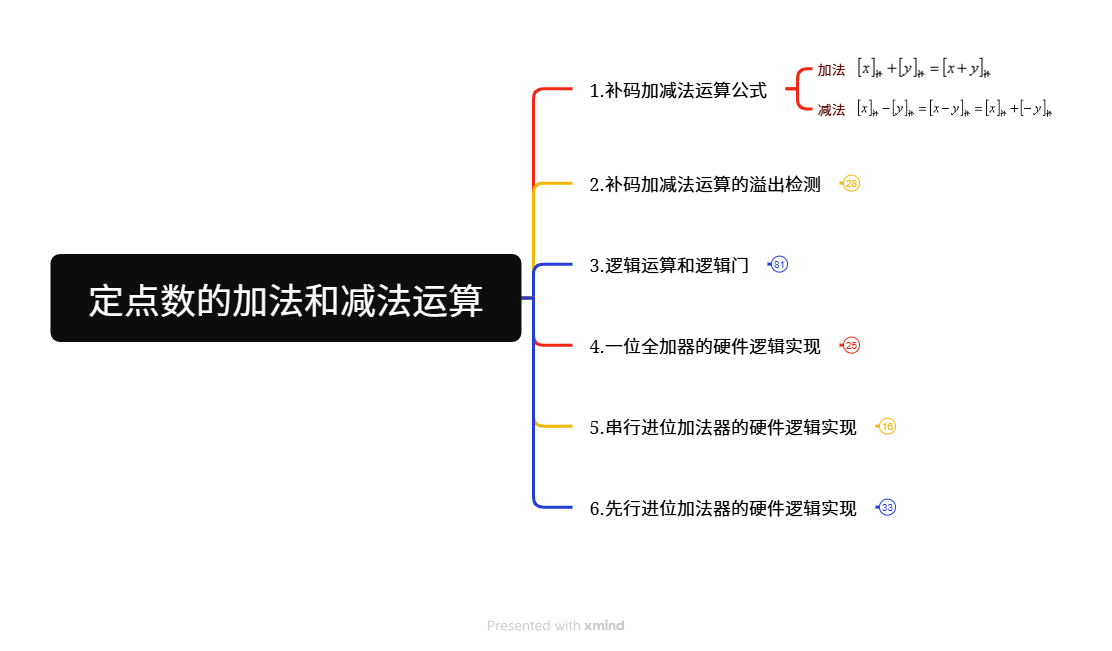

一、补码加减法运算规则

![]() ,

,![]()

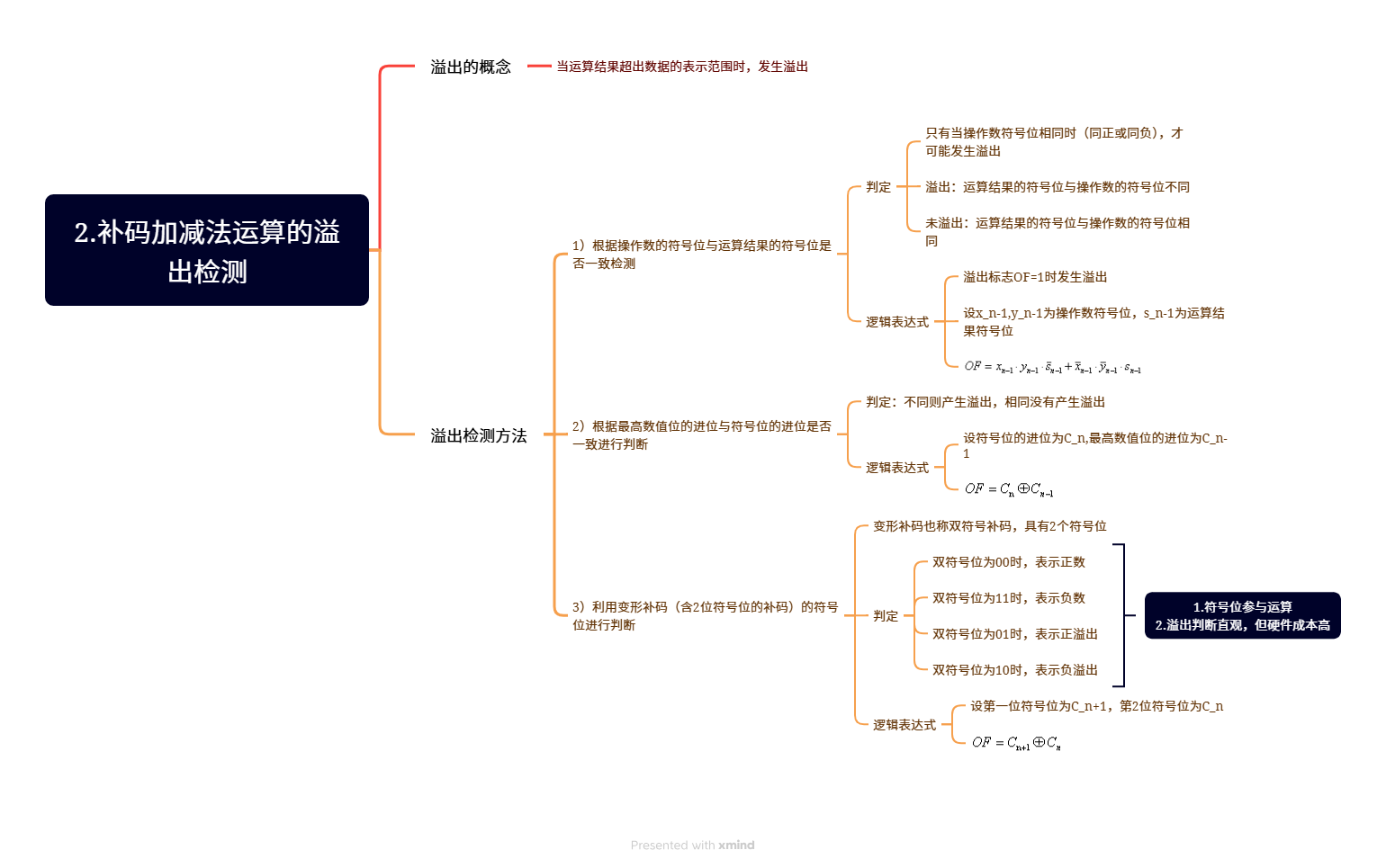

二、补码加减法运算的溢出检测

1.溢出的概念

当运算结果超出数据的表示范围时,发生溢出

2.有符号数溢出检测方法

1)根据操作数的符号位与运算结果的符号位是否一致检测

- 只有当操作数符号位相同时(同正或同负),才可能发生溢出

- 溢出:运算结果的符号位与操作数的符号位不同

- 未溢出:运算结果的符号位与操作数的符号位相同

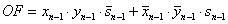

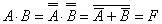

- 设x_n-1,y_n-1为操作数符号位,s_n-1为运算结果符号位:

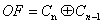

2)根据最高数值位的进位与符号位的进位是否一致进行判断

- 判定:不同则产生溢出,相同没有产生溢出

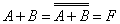

- 逻辑表达式:

3)利用变形补码(含2位符号位的补码)的符号位进行判断

- 变形补码也称双符号补码,具有2个符号位

- 判定:双符号位为00时,表示正数;为11时,表示负数;为01时,表示正溢出;为10时,表示负溢出。

- 逻辑表达式:

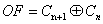

三、逻辑运算和逻辑门

1.基本逻辑电路与基本逻辑门

1)与运算和与门

-

与运算逻辑表达式

-

与门电路符号:

2)或运算和或门

-

或运算逻辑表达式

-

或门电路符号:

3)非运算和非门

-

非运算逻辑表达式

-

非门电路符号:

2.复合逻辑电路与复合逻辑门

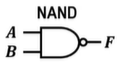

1)与非运算和与非门

-

与非运算逻辑表达式

-

与非门电路符号:

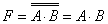

-

使用与非门构建基本逻辑门

-

与非门构建非门:

-

与非门构建与门:

-

与非门构建或门:

-

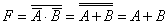

2)或非运算和或非门

- 或非运算逻辑表达式:

- 或非门逻辑电路:

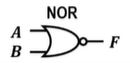

- 使用或非门构建基本逻辑门

- 或非门构建非门:

- 或非门构建与门:

- 或非门构建或门:

- 或非门构建非门:

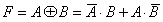

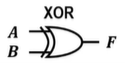

3)异或运算和异或门

- 异或运算逻辑表达式:

- 异或门逻辑电路:

4)同或运算和同或门

- 同或运算逻辑表达式:

- 同或门逻辑电路:

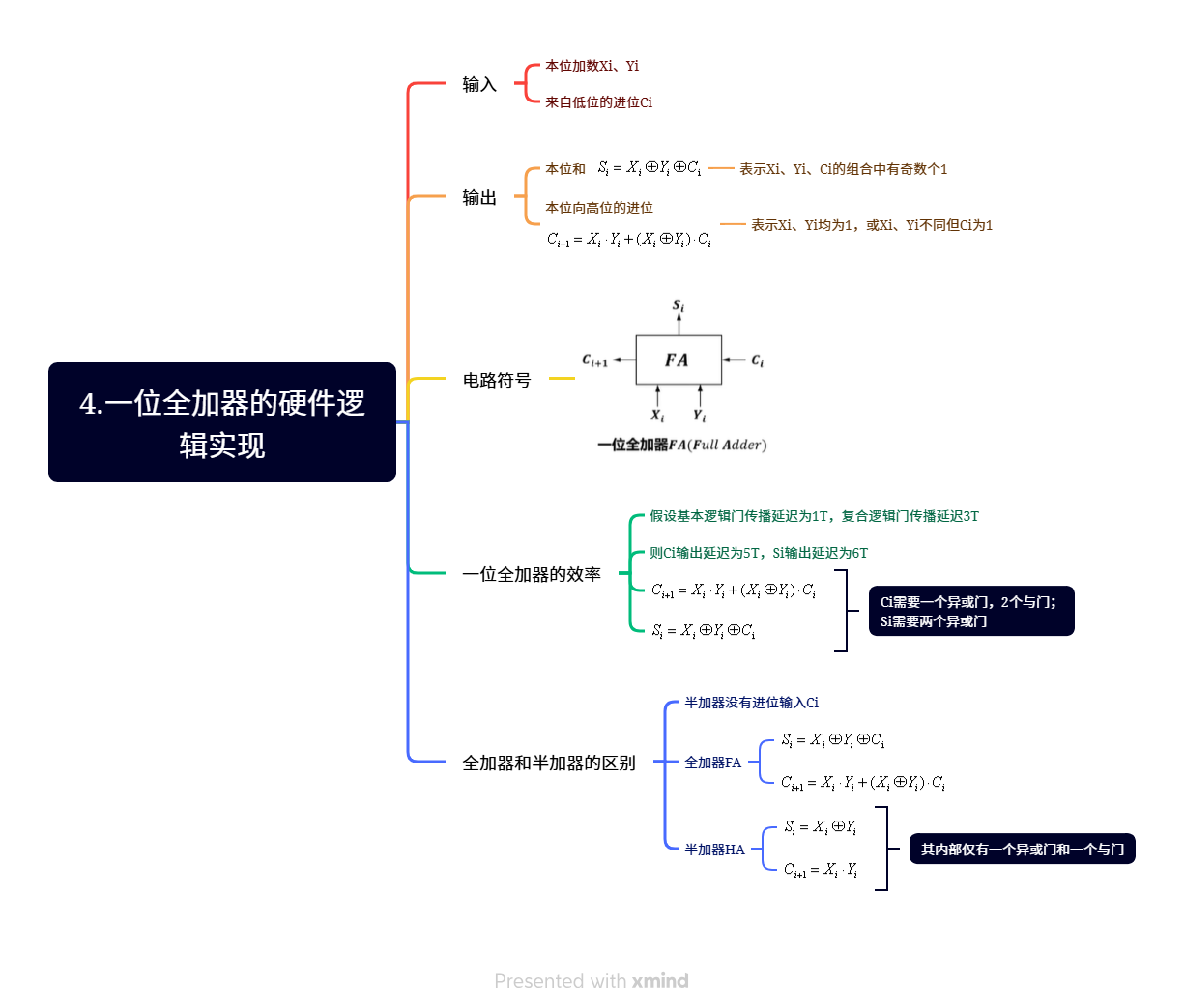

四、一位全加器的硬件逻辑实现

1.一位全加器的输入、输出和电路符号

1)输入

- 本位加数Xi、Yi

- 来自低位的进位Ci

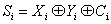

2)输出

- 本位和

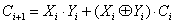

- 本位向高位的进位:

3)电路符号

2.一位全加器的效率

假设基本逻辑门传播延迟为1T,复合逻辑门传播延迟3T

则Ci输出延迟为5T,Si输出延迟为6T

- 由

,Ci需要一个异或门,2个与门;

,Ci需要一个异或门,2个与门; - 由

,Si需要两个异或门

,Si需要两个异或门

3.全加器和半加器的区别

- 半加器没有进位输入Ci

- 其内部仅有一个异或门和一个与门

,

,

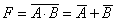

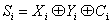

五、串行进位加法器的硬件逻辑实现

1.核心

使用多个一位全加器串行得到串行进位加法器

2.溢出检测方法

1)无符号数

最高位的进位Cn就是是否溢出的标志:![]()

2)带符号数

最高数值位的进位与符号位的进位不同溢出:![]()

3.传输延迟(性能)

假设基本逻辑门传播延迟为1T,复合逻辑门传播延迟3T

传输延迟:![]()

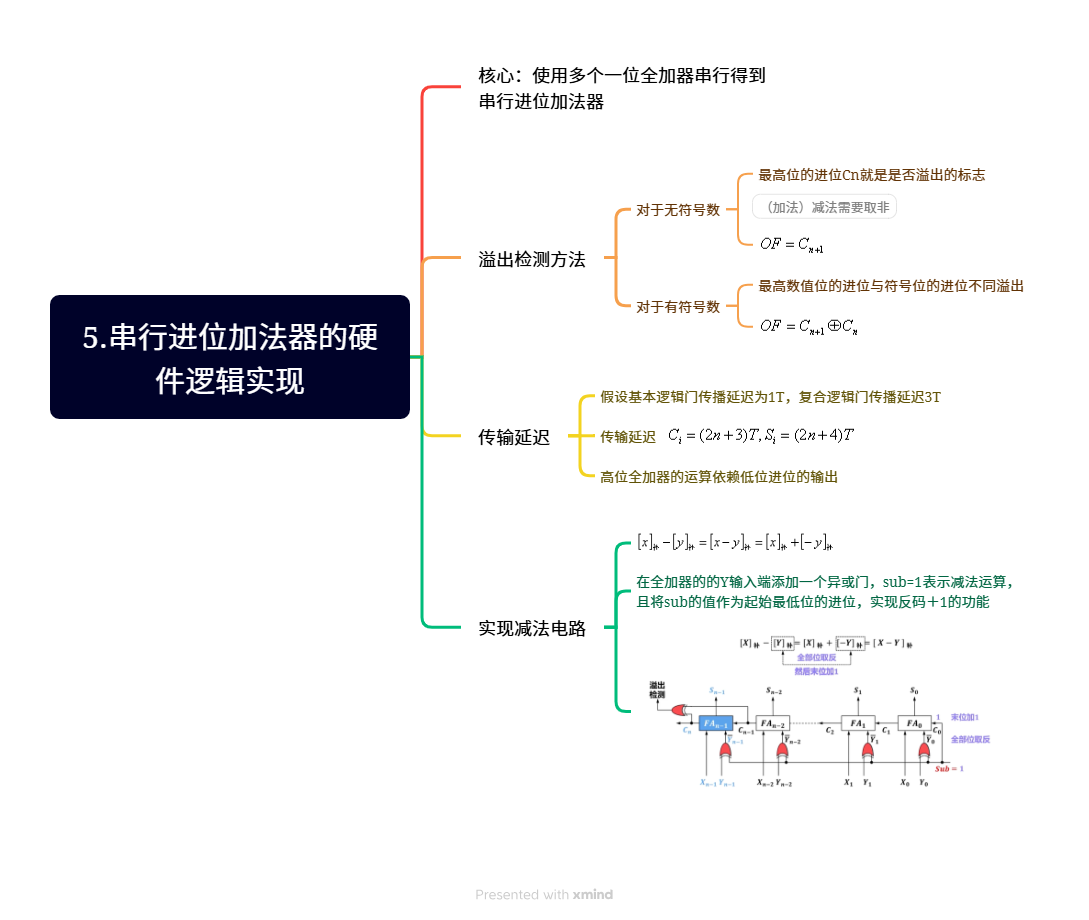

4.加法电路实现减法电路

1)原理

![]()

2)实现

在全加器的的Y输入端添加一个异或门,sub=1表示减法运算,且将sub的值作为起始最低位的进位,实现反码+1的功能。

六、先行进位加法器的硬件逻辑实现

1.优化关键

打破高位进位输入对低位进位输出的依赖

2.构建4位先行进位电路

1)进位生成函数和进位传递函数

- 进位生成函数:

- 进位传递函数:

2)核心

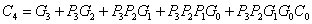

![]()

向高位的进位Cn可由Gi、Pi及C0经过逻辑运算得到,不再依赖低位进位

3)构建

先行进位电路通常采用4位一组,因为位数越多,逻辑门扇入系数越大,制造难度越大

4)性能

4位先行进位电路时间延迟为2T(与门和或门)

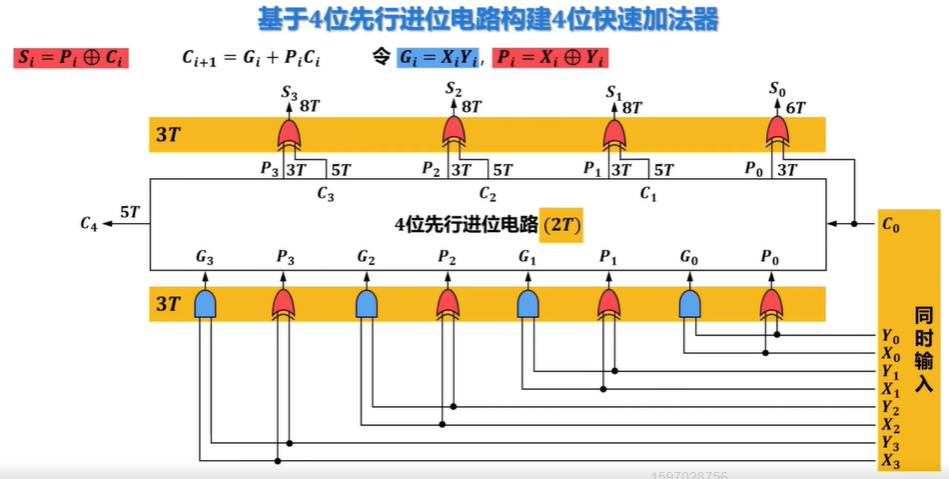

3.基于4位先行进位器构建4位快速加法器

1)构建

2)性能

4位快速加法器比4位串行加法器性能提高了1.5倍

- 4位串行加法器:(2×4+4)=12T

- 4位快速加法器:8T

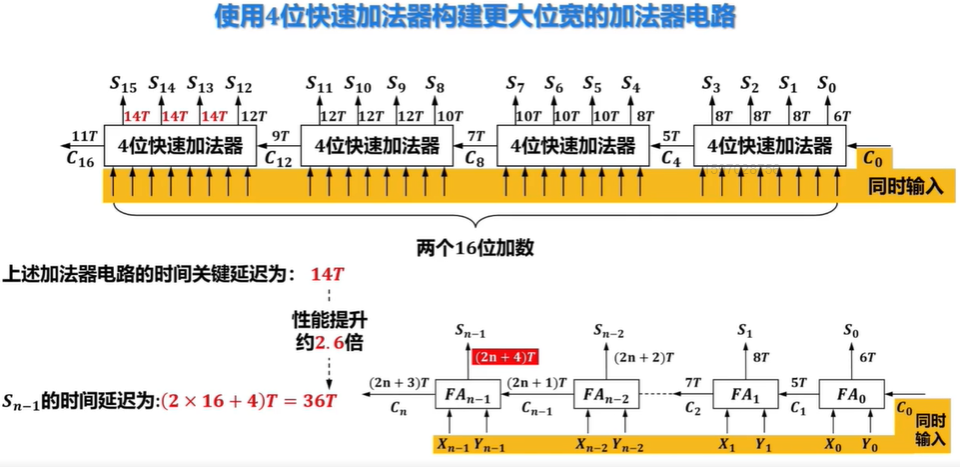

4.基于4位快速加法器构建组内并行,组间串行16位加法器

![]()

核心:向高位的进位Cn可由Gi、Pi及C0经过逻辑运算得到,不再依赖低位进位

5.基于4位快速加法器构建组内并行,组间并行16位加法器

1)核心

利用先行进位电路提前产生C4,C8,C12,C16信号

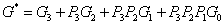

2)构建可级联的4位先行进位电路

- 由

- 组进位生成函数:令

- 组进位传递函数:令

3)4位可级联快速加法器

4)构建16位可级联快速加法器

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?