下载安装

下载

- 比较Quartus Prime软件的专业版、标准版和精简版的功能

- quartus-prime 18 download

- quartus-lite 18 download

- 官网下载以及申请license: https://www.intel.com/content/www/us/en/software-kit/711791/intel-quartus-ii-web-edition-design-software-version-13-0sp1-for-windows.html

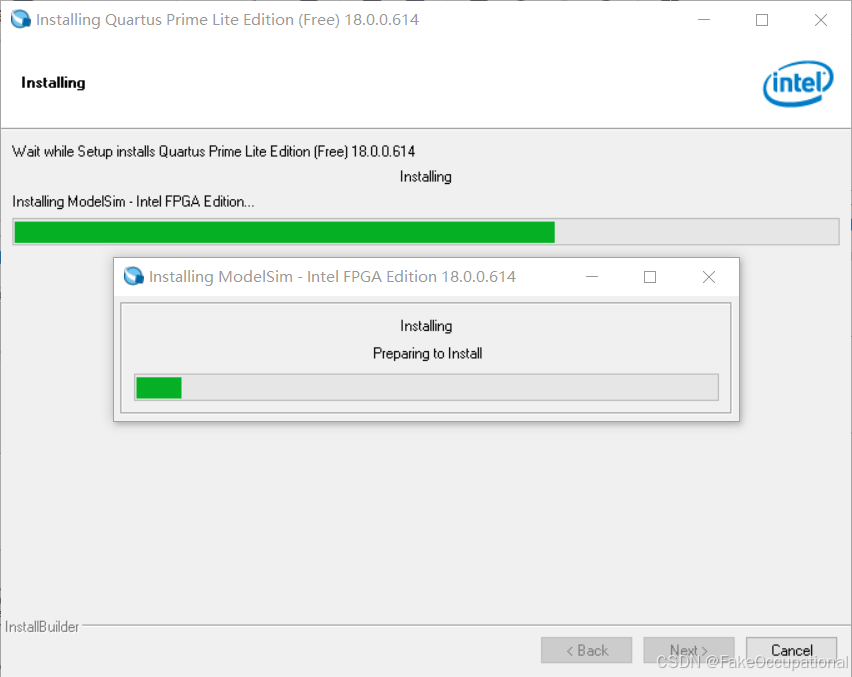

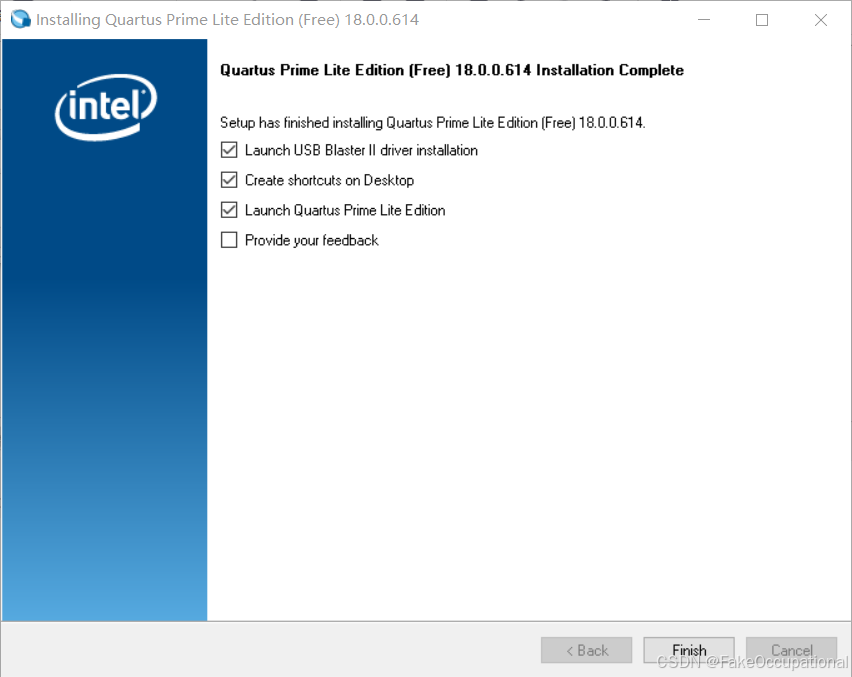

安装

- 解压后运行setup.bat

新建项目与简单使用

- 新建项目与简单使用参考:Quartus II 简明教程

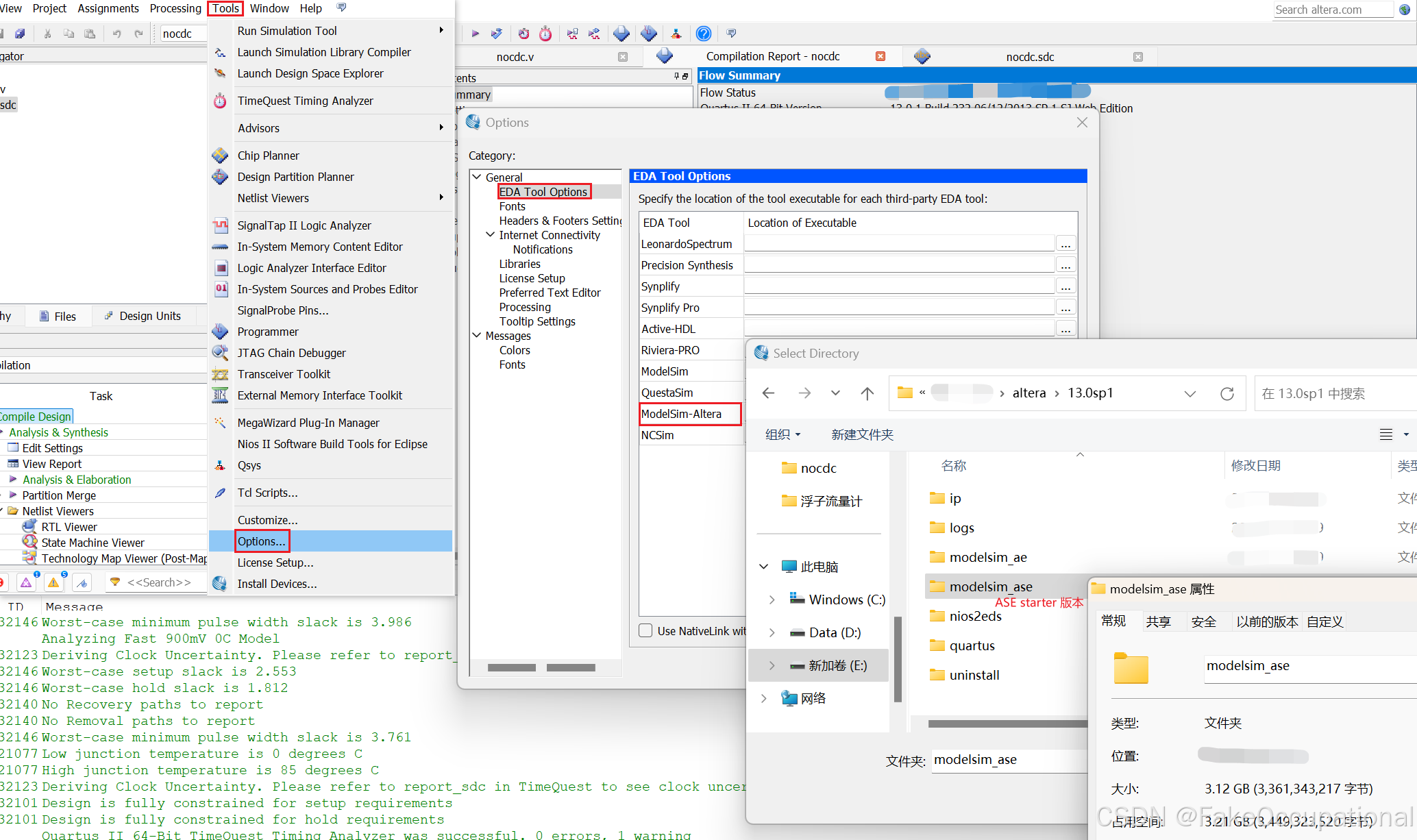

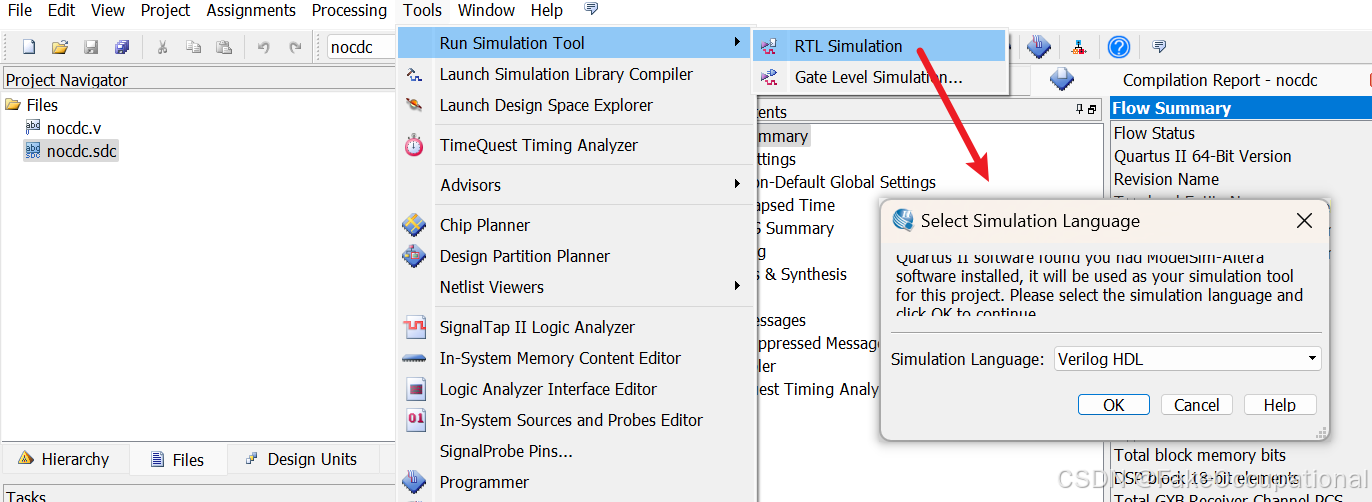

modelsim_ase仿真

- 选择

\altera\13.0sp1\modelsim_ase\win32aloem或C:\altera\13.1\modelsim_ase\win32aloem\

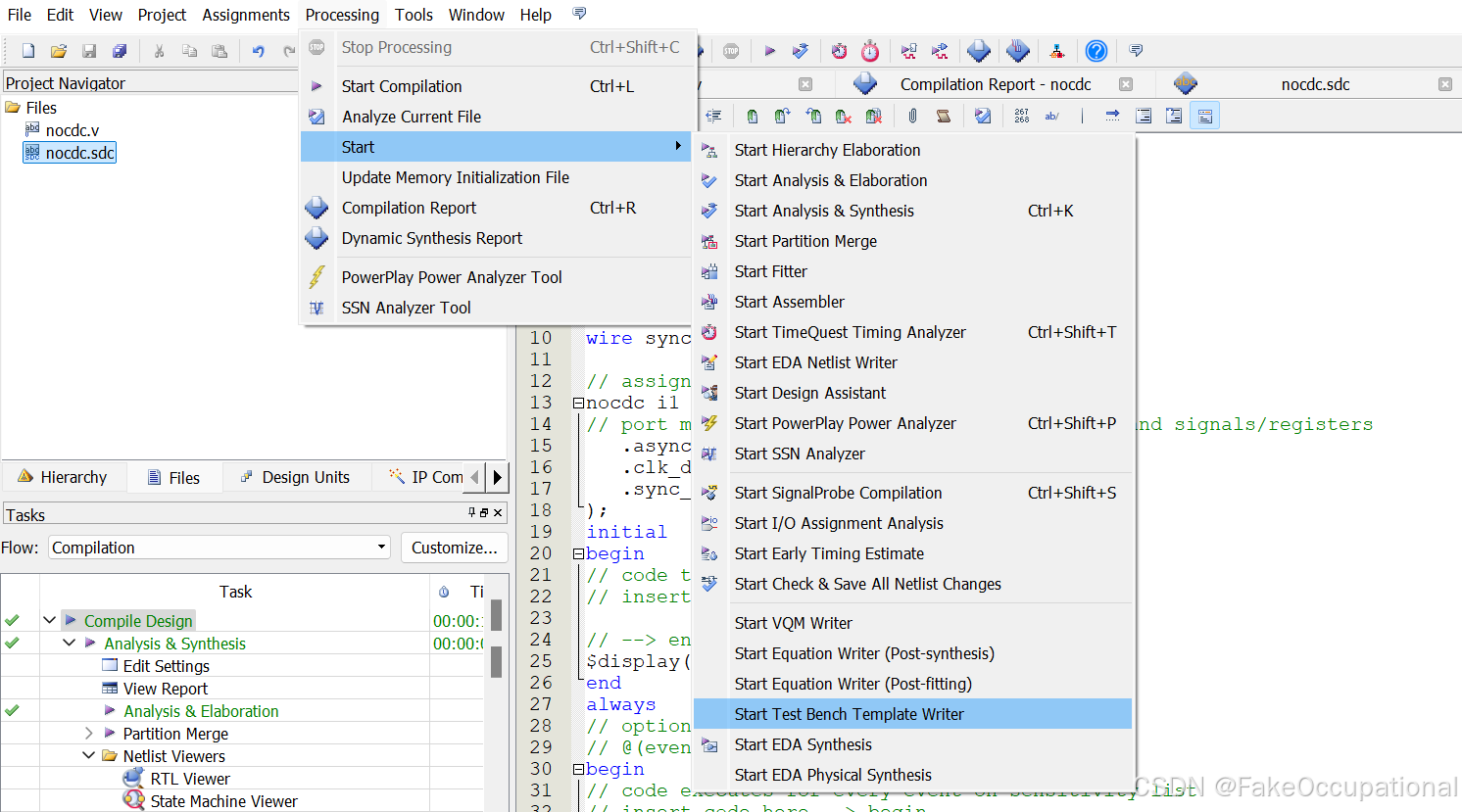

可选(生成vt模板)

修改.vt文件

- 修改.vt文件,以下为IDE自动根据.v文件生成的

`timescale 1 ps/ 1 ps

module nocdc_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg async_signal;

reg clk_dst;

// wires

wire sync_signal;

// assign statements (if any)

nocdc i1 (

// port map - connection between master ports and signals/registers

.async_signal(async_signal),

.clk_dst(clk_dst),

.sync_signal(sync_signal)

);

initial

begin

// code that executes only once

// insert code here --> begin

// --> end

$display("Running testbench");

end

always

// optional sensitivity list

// @(event1 or event2 or .... eventn)

begin

// code executes for every event on sensitivity list

// insert code here --> begin

@eachvec;

// --> end

end

endmodule

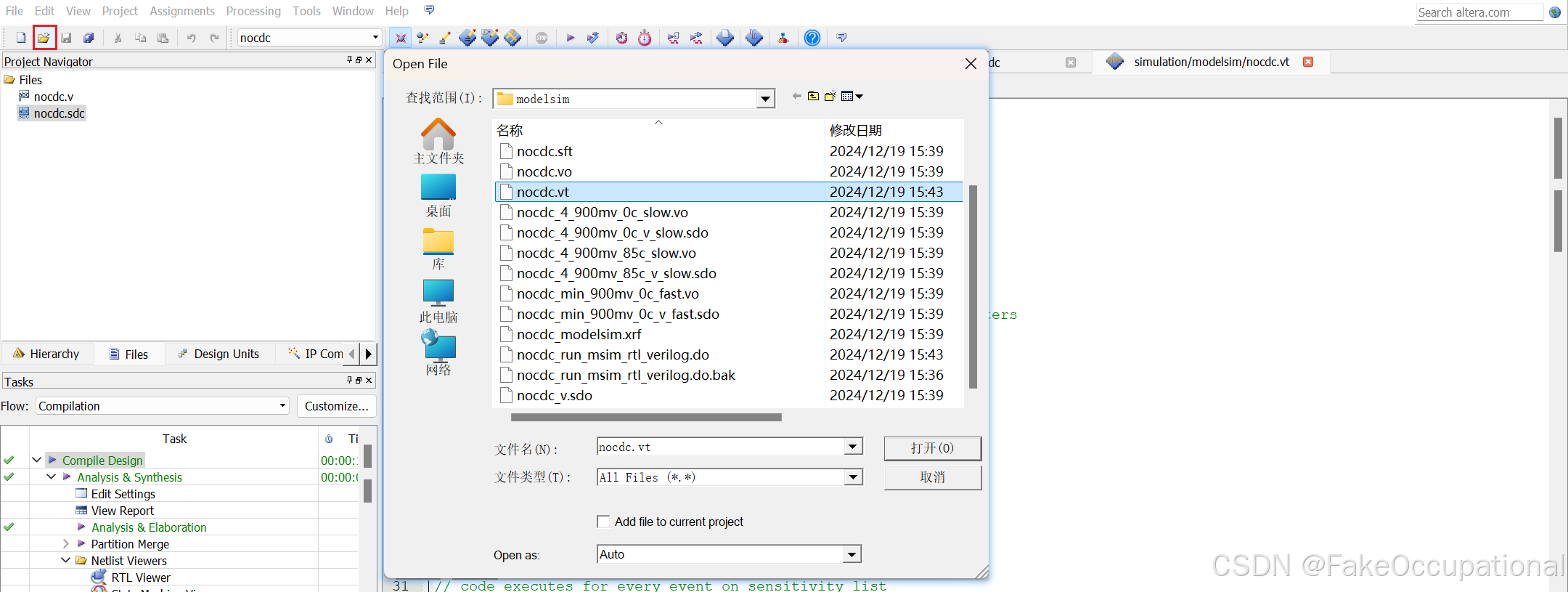

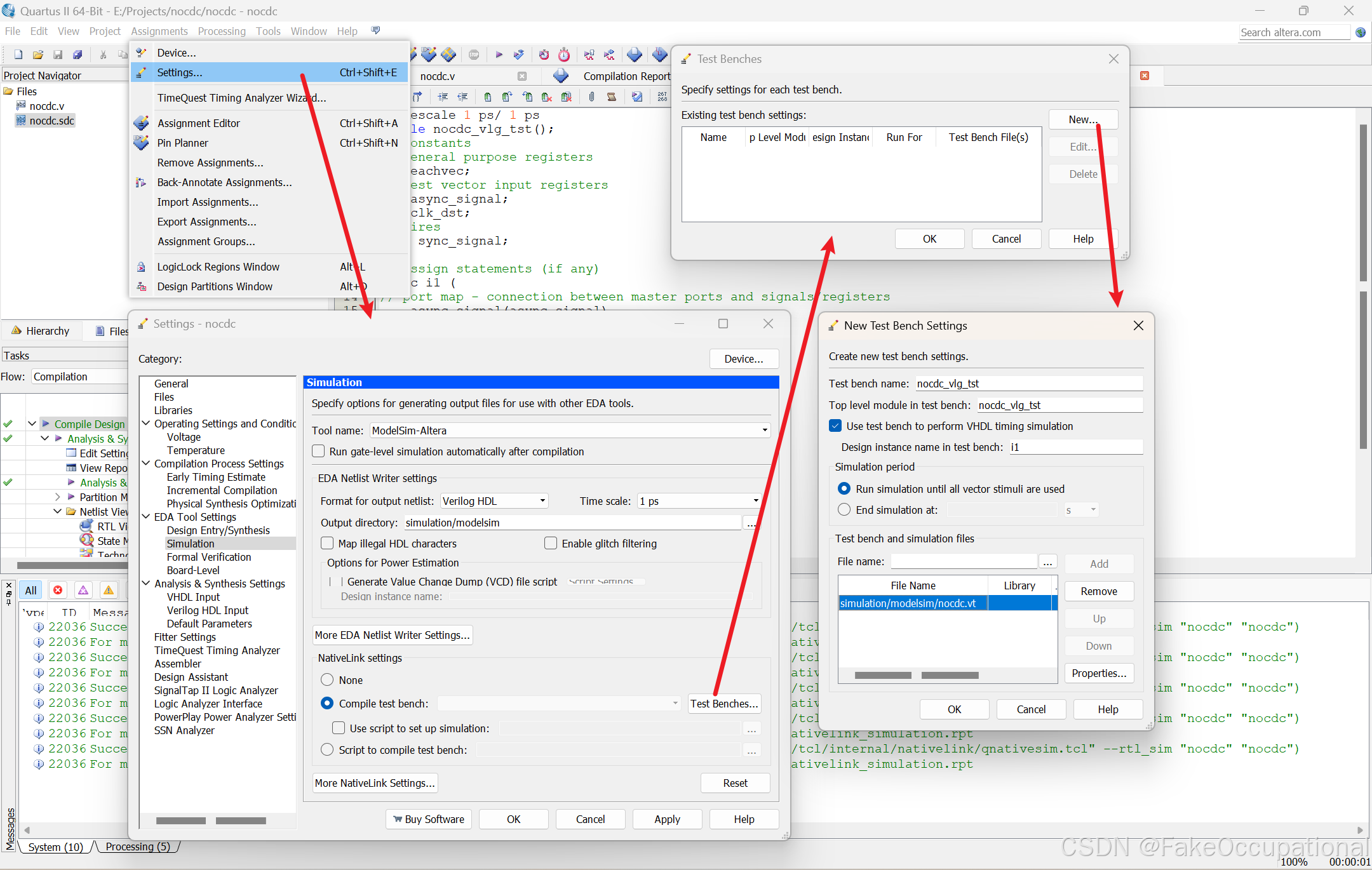

- 设置vt激励文件

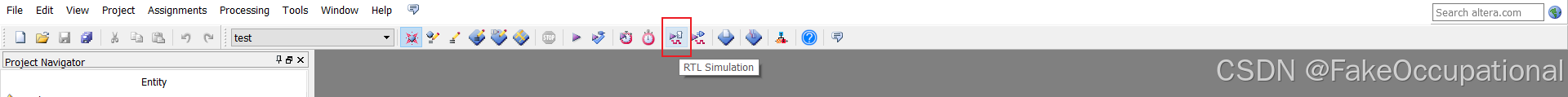

- 点击进行仿真

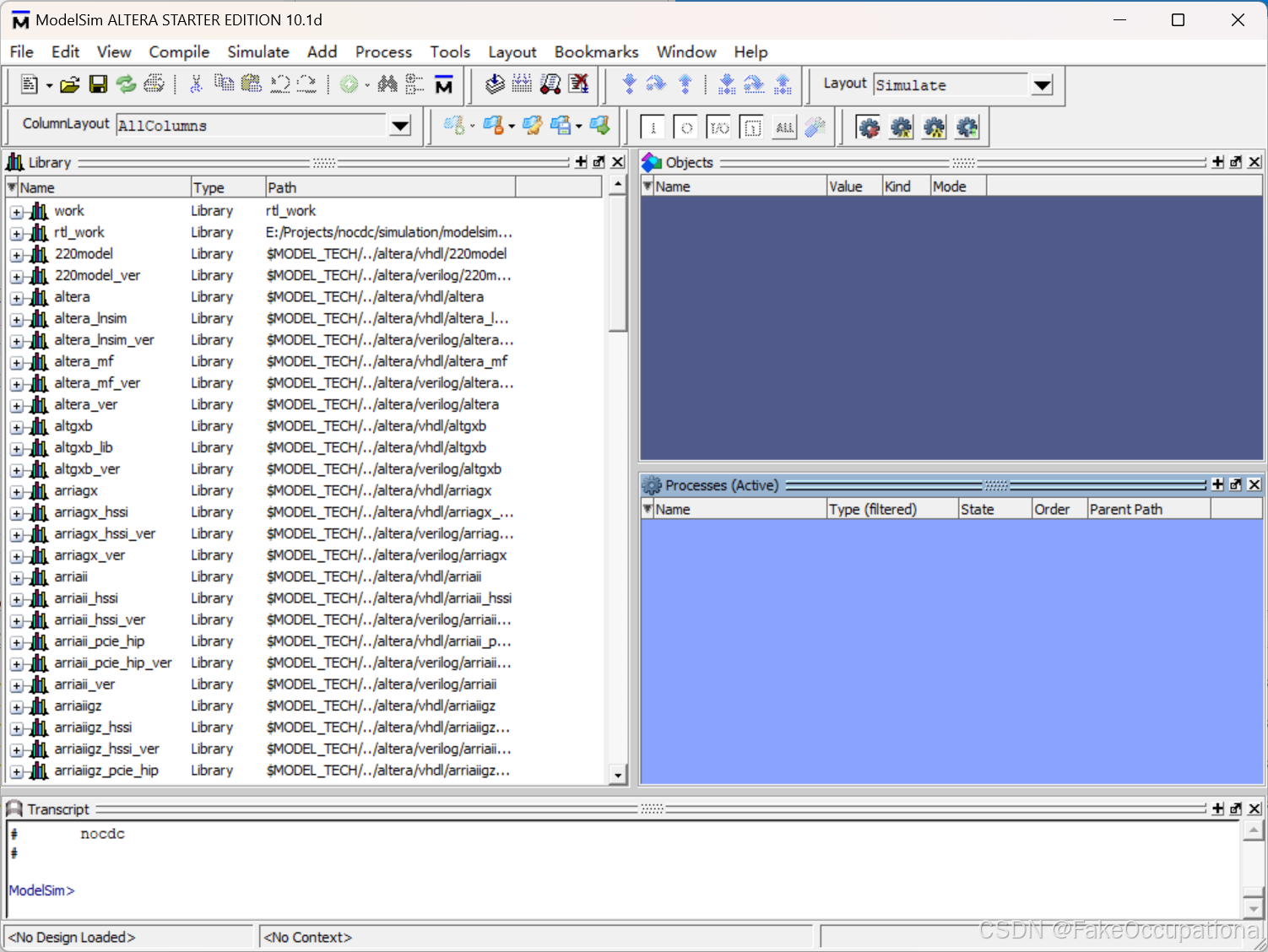

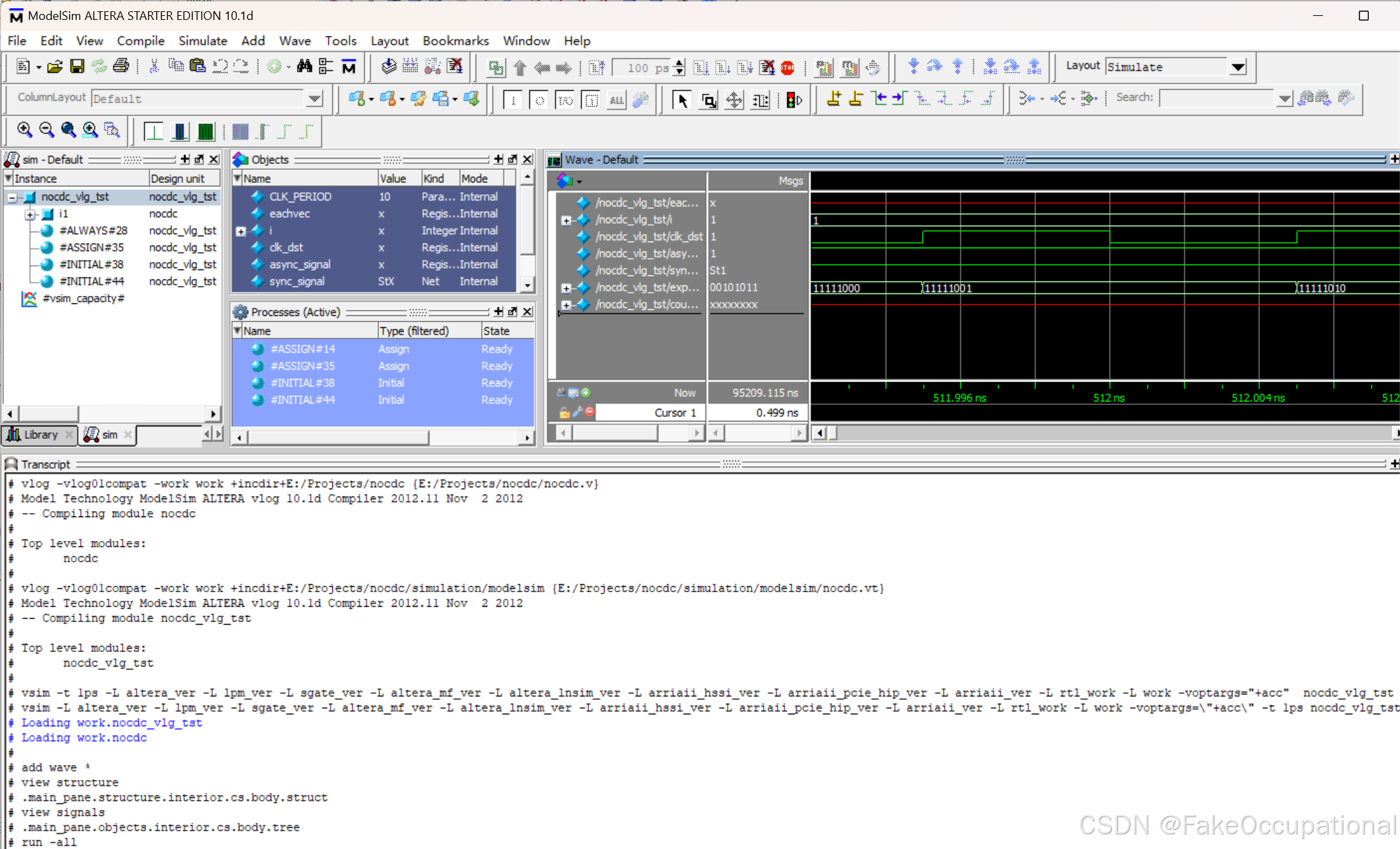

- 打开仿真界面,进行查看(一般需要先点击“-”放大镜找到时间起始点)

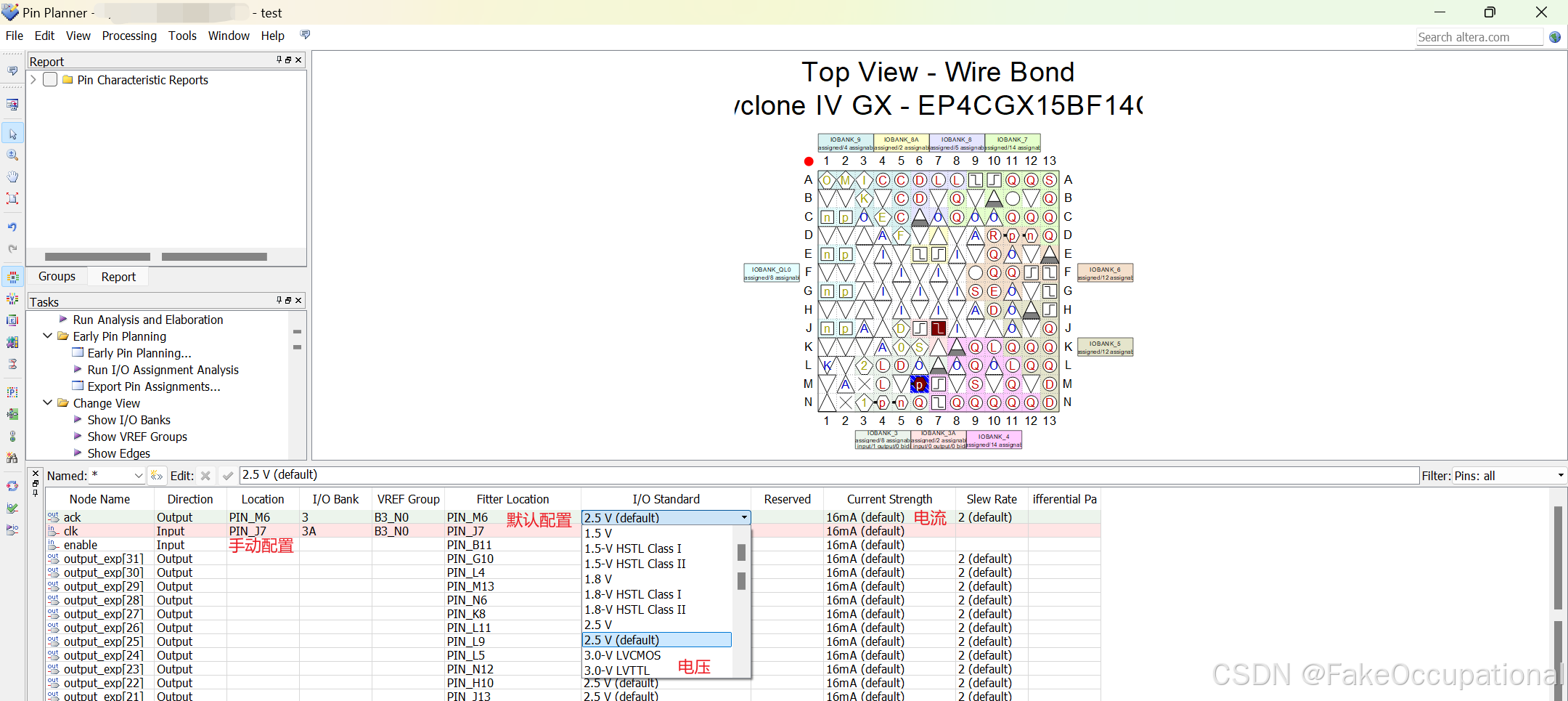

Pin Planner 分配I/O管脚

-

Assignments > Pin Planner:

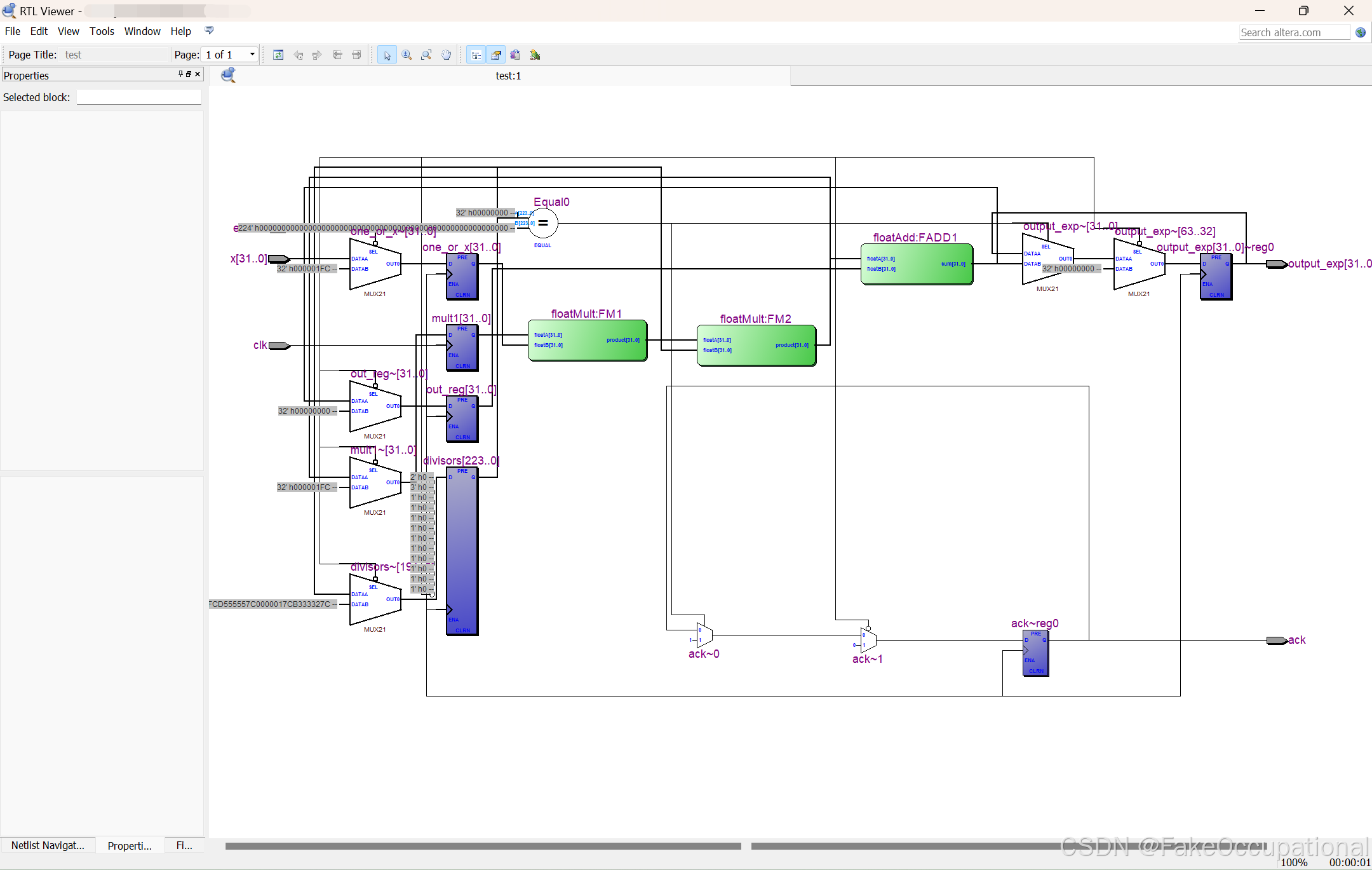

RTL-Viewer

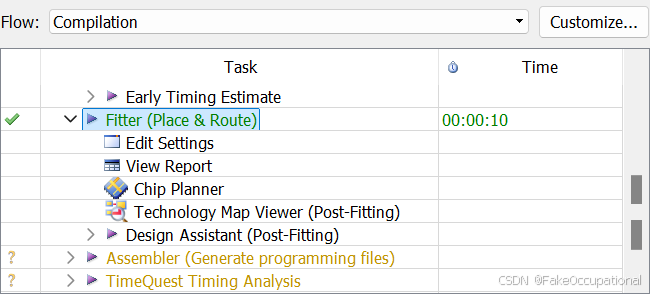

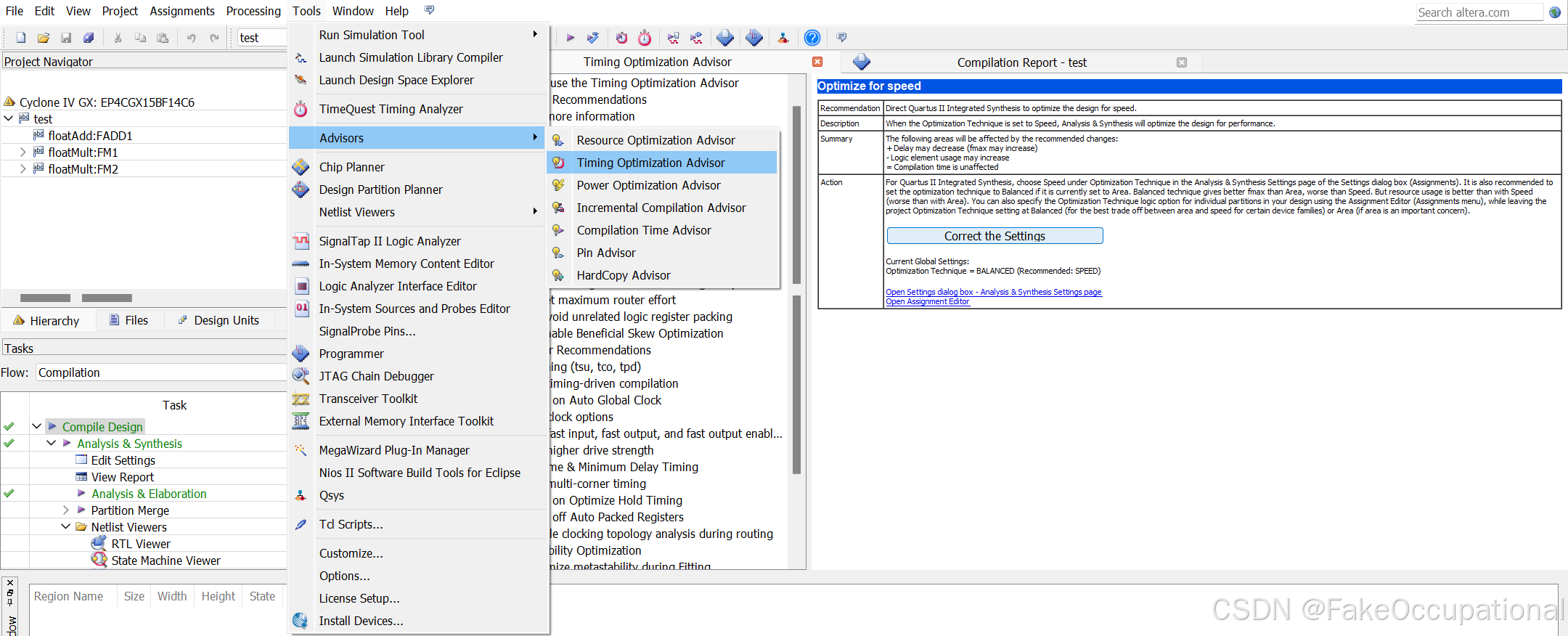

Optimization Advisor

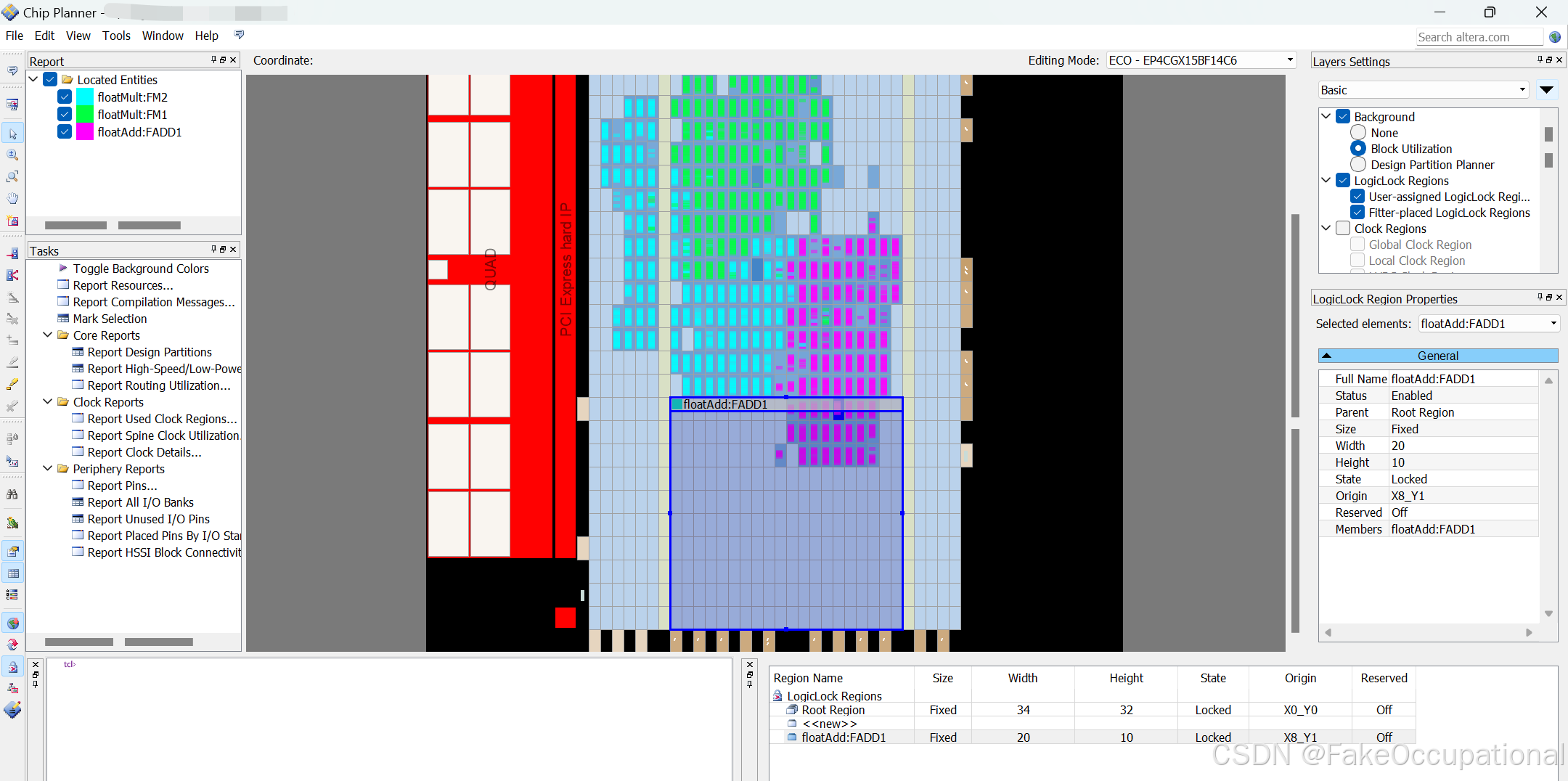

逻辑锁定

- 下图中用不同颜色显示了不同module,logiclock 可以规定哪个module在芯片中的位置,放置自动布线与综合工具修改。

SignalTap II

- Modelsim 仿真的硬件版本,SignalTap II 通过JTAG与FPGA连接,程序在真实硬件中运行。

设置

- SignalTap II设置完成之后再次进行综合。

- Filter 选择 SignalTap II: pre-synthessis 项(否则可能找不到网络标识)

抓取

- 保存stp后,下载程序,进行波形分析

3716

3716

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?