一、时钟

1.时钟是具有周期的脉冲信号,通常是占空比为50%的方波

2.时钟是单片机的脉搏,搞懂时钟走向和关系,对单片机的使用至关重要

二、时钟树

在复杂的数字芯片(如CPU、SoC)内部,有数以亿计的晶体管需要协同工作,它们必须由一个统一的“心跳”——时钟信号来驱动。时钟树就是将这些时钟信号从源头(如晶振或PLL输出端)有效、稳定地传递到每一个时序元件(如触发器)的物理布线网络。

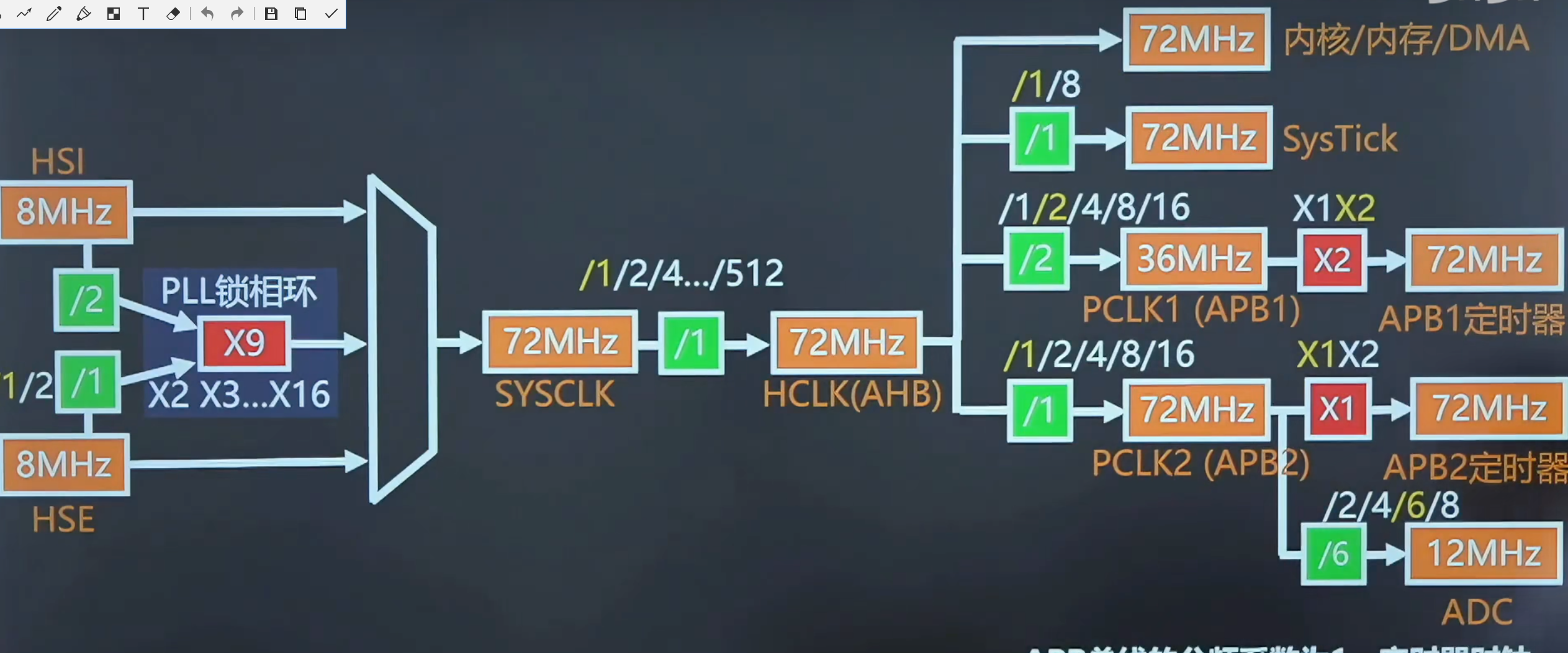

2.1 高速简化时钟线

注释:

我们从左往右看,如果信号从HSI(高速内部振荡器)他只能2分频,如果PLL锁相环最大是

9无法达到SYSCLK(系统时钟或者主时钟)需要的72MHz,所以HSI不用,则使用HSE(高速外部振荡器),他可以1分频也可以2分频,这里用1分频。

ADC的频率要小于14HMz

ADC(模数转换器)的时钟频率要小于某个特定值(如14MHz),本质上是为了保证其内部模拟和数字电路在每一步都有足够的时间(建立时间)来稳定和做出正确操作,从而确保ADC能达到其标称的精度、线性和信噪比等关键性能指标。

2.1.1 PLL锁相环是什么?

锁相环是一个反馈控制系统,它使其输出时钟信号的相位和频率与一个输入参考时钟信号保持完全一致。简单说,它是一个“时钟复制、提纯和变速”的核心芯片。

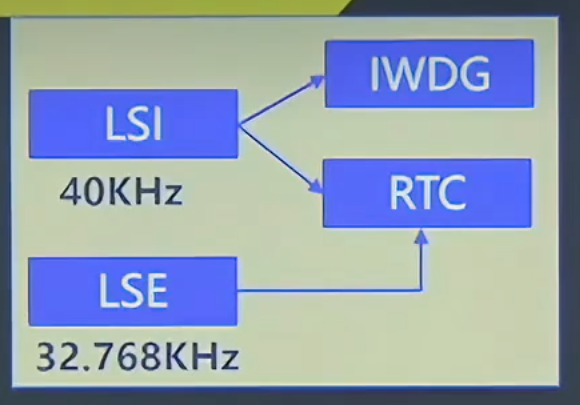

2.2 低速简化时钟线

IWDG(独立看门狗)是一个完全独立于主系统运行的硬件计时器。它的时钟来源于芯片内部专用的低速RC振荡器,这个时钟源不受主时钟控制,即使主CPU时钟停止,IWDG依然能继续工作。

2.2.1 IWDG(独立看门狗)为什么使用低速内部振荡

1. 绝对独立,不受主系统影响(核心原因)

这是IWDG设计的首要目标。

-

故障隔离:如果IWDG的时钟源和主CPU使用同一个时钟(如外部高速晶振HSE或内部主时钟HSI),那么一旦这个公共时钟源因干扰、故障或软件配置错误而失效,整个系统(包括看门狗)将一同“死亡”,监督机制形同虚设。

-

终极守护:IWDG的职责是在主系统完全失控时进行干预。使用独立的低速内部RC振荡器,确保了即使:

-

外部晶振(HSE)停振。

-

主PLL锁相环失效。

-

软件错误地修改了时钟配置寄存器。

-

系统进入意外的低功耗状态。

IWDG的“心跳”依然能够持续,并在超时后果断触发复位,成为系统恢复的最后希望。

-

2. 更高的可靠性与鲁棒性

-

物理特性:低速内部RC振荡器电路简单,集成在芯片内部。与需要外部晶体和负载电容的高速晶振相比,它更不容易受到电磁干扰、电源噪声和PCB布局的影响。

-

环境适应性:虽然其频率精度不高(可能有±%的偏差),并且受温度和电压影响,但对于看门狗“粗略计时”的任务来说完全足够。它的核心价值是“始终在工作”,而不是“走得绝对精准”。

3. 低功耗运行,适用于所有模式

-

常驻运行:IWDG需要在所有低功耗模式下继续工作(如STM32的Stop、Standby模式)。LSI本身功耗极低,使得IWDG可以以微小的能耗代价持续提供保护。

-

自给自足:系统进入深度睡眠时,主时钟可能被关闭以省电。IWDG依靠自己低功耗的内部时钟源,无需依赖任何可能被关闭的外部资源。

4. 上电即用,启动迅速

-

无初始化依赖:在系统上电或复位后,外部晶振可能需要较长的起振稳定时间(几毫秒),而复杂的时钟树配置也需要软件干预。LSI在上电后极短时间内(通常几微秒) 即可稳定运行。

-

即时保护:这使得IWDG可以在系统启动的最早期阶段就被激活,为后续的软件初始化(包括配置更精确的时钟)过程提供即时保护。

2.2.2 RTC实时时钟为什么同时使用LSI和LSE

RTC(实时时钟)模块同时支持LSI(低速内部振荡器)和LSE(低速外部振荡器) 作为时钟源,是设计者在精度、成本、可靠性和灵活性之间做的平衡。下面详细解释为什么需要这种双时钟支持:

主要区别对比

|

特性 |

LSI(内部RC振荡器) |

LSE(外部32.768kHz晶振) |

|---|---|---|

|

精度 |

低(通常±1%~±5%) |

高(±20ppm,约每月±52秒) |

|

温度稳定性 |

差(随温度漂移大) |

好(温度补偿晶振更优) |

|

功耗 |

较低 |

极低(特别是低功耗晶振) |

|

成本 |

零(集成在芯片内) |

需要外部晶振+负载电容 |

|

启动速度 |

快(微秒级) |

慢(需起振时间,毫秒级) |

|

占用引脚 |

无 |

需要2个专用引脚 |

|

可靠性 |

高(不受外部影响) |

依赖外部元件质量 |

为什么需要双时钟支持?

1. 精度与成本的权衡

-

需要高精度的应用(如数据记录器、智能电表、医疗设备):必须使用LSE

-

LSE使用32768Hz晶振,频率精确稳定

-

一天误差可小于1秒,年误差仅几分钟

-

适合需要长时间准确计时的场合

-

-

成本敏感的应用(如简单定时器、低端消费品):可使用LSI

-

无需外部元件,降低BOM成本

-

精度要求不高时完全可用(如简单的定时开关)

-

2. 系统可靠性的冗余设计

-

故障切换机制:高端系统可配置时钟监测

-

主时钟用LSE,备份时钟用LSI

-

当检测到LSE故障(晶振停振)时,自动切换到LSI

-

确保RTC永不停止,尽管精度下降

-

-

启动阶段的保障:系统上电时,LSE需要起振时间

-

可先用LSI让RTC快速启动

-

待LSE稳定后再切换,减少时间损失

-

3. 不同工作模式的需求

-

运行模式:使用LSE保证计时精度

-

低功耗模式:某些深度睡眠状态可能需要关闭LSE以进一步省电

-

切换到LSI维持基本计时

-

或完全依赖LSI进行唤醒

-

4. 校准与补偿的灵活性

-

LSI的校准:STM32等MCU支持LSI校准

-

可通过LSE或外部精确时钟来校准LSI

-

校准后LSI精度可大幅提升(达到±0.5%以内)

-

在LSE失效时,校准过的LSI可作为可接受替代

-

5. 应用场景多样性

// 实际配置示例(STM32)

void RTC_ClockConfig(void) {

// 情况1:高精度应用,使用LSE

__HAL_RCC_LSE_CONFIG(RCC_LSE_ON); // 开启外部晶振

__HAL_RCC_RTC_CONFIG(RCC_RTCCLKSOURCE_LSE); // RTC选择LSE

// 情况2:低成本应用,使用LSI

__HAL_RCC_LSI_ENABLE(); // 开启内部振荡器

__HAL_RCC_RTC_CONFIG(RCC_RTCCLKSOURCE_LSI); // RTC选择LSI

// 情况3:自动备份切换(高级用法)

// 配置时钟安全系统(CSS),LSE失效时自动切换到LSI

}

典型应用策略

策略A:精度优先(工业级产品)

-

始终使用LSE作为主时钟源

-

定期通过GPS或网络时间协议(NTP)同步校准

-

LSI仅作为备份或在LSE起振期间的临时时钟

策略B:成本优先(消费级产品)

-

仅使用LSI,通过软件补偿

-

出厂时校准并存储补偿值到Flash

-

定期软件修正(如每天±N个滴答)

策略C:可靠性优先(医疗/汽车)

-

同时使用LSE和LSI

-

硬件监控LSE状态

-

故障时无缝切换,记录切换事件供诊断

实际工程考虑

PCB布局影响

-

LSE:需要精细的PCB布局,晶振靠近MCU,避免干扰

-

LSI:完全不受PCB布局影响

温度范围

-

工业温度范围(-40℃~85℃):LSE表现更稳定

-

消费级温度(0℃~70℃):LSI可接受

长期漂移

-

LSE:老化率约±5ppm/年

-

LSI:无老化概念,但整体精度差

总结

RTC同时支持LSI和LSE的设计哲学:

-

提供选择权:让开发者根据应用需求(精度 vs 成本)选择

-

实现冗余备份:提高系统可靠性,避免单点故障

-

覆盖全场景:从几美元的简单设备到高可靠工业设备都能支持

-

平衡性能:在精度、功耗、成本、可靠性之间取得最佳平衡

这种双时钟设计体现了嵌入式系统的典型思维:不提供单一"最优"方案,而是提供可配置的选项,让工程师针对具体应用做出最合适的选择。对于需要准确日历时间的应用,LSE是必须的;对于只需相对计时或简单定时的应用,LSI是经济高效的解决方案。

2694

2694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?