近期学习使用Verilog编写DDR3接口读写测试,在编写过程中遇到许多问题,最终功夫不负有心人,实现了DDR3数据写入和数据读取功能。同时在问题排查过程中,也学习到了很多新的东西。

现将我实现DDR3读写测试功能过程与大家一起分享,在此感谢我的朋友们对我的指点和帮助。在本例中只讲解如何添加IP核,实现DDR3数据的读写功能。因作者水平有限,文档中难免会有疏漏之处,欢迎读者批评指正。

目录

1:使用器件

2:开发环境

3:IP核添加

4:实例工程生成

5:实例工程讲解

6:参考代码

7:仿真测试

1:使用器件

a):FPGA器件型号:xc7vx485tffg1761-2;

b):DDR3器件型号:MT41K256M16XX-125;

2:开发环境

a):开发环境:Vivado 2017.2

b):开发语言:Verilog

3:IP核添加

在新建工程中添加IP核,添加步骤如下所示:

a):点击project manager 菜单下IP Catalog选项,打开IP界面;

b):在IP核界面搜索栏输入mig ,会自动出现Memory Interface Generator选项,双击该选项进入到DDR配置界面;

c):等待Vivado运行完成,会出现Memory Interface Generator配置界面,检查器件型号等信息无误后,点击next,(左下角选项 User Guide可以点击下载官方资料文件);

d):选择Create Design,Component Name选项可以修改名称,Number of Controllers选项可以选择DDR的片数,本例中只选择一片,配置完成后点击next;

e):此处不选择其他型号,点击next;

f): 本例器件类型为DDR3,选择DDR3 SDRAM,点击next;

g): clock period选项选择1250ps,800MHz时钟,Memory Type选项中选择Components(贴片式组件),Memory Part选择:MT41K256M16XX-125,点击Create Custom Part,在出现的对话框Enter New Memory Part Name选项中输入MT41K512M16XX-125,Row Address下拉选项中选择16位宽(这里设置按照我的硬件资源环境设置的,可以根据个人硬件环境进行调整,在后面代码中修改位宽即可),设置完成后点击next;

h):在Input Clock Period选项中选择5000ps,200MHz,完成后点击next;

i):System Clock选项选择No Buffer,Reference Clock选择Use System Clock,设置完成后点击next;

j):默认设置,点击next;

k):选择New Deign,本例不提供引脚配置文件,点击next;

l):采用默认分配,点击next;

m):采用默认分配,点击next;

n):在界面中检查配置选项是否存在错误,确认无误后点击next;

o):点击选择Accept,点击next,接下来几个页面都可以直接点击next;

p):等待vivado运行完成,出现生成界面,点击Generate;

q):等待vivado完成IP核生成;

r):继续等待vivado运行完成,运行完成后IP核就添加完成;

4:实例工程生成

a):添加IP核完成后,在sources管理界面下方选择IP sources界面,选中IP核。

b):点击右键,选择Open IP Example Design打开实例工程;

c):选择实例工程保存位置,点击ok后vivado会自动运行生成一个实例工程文件;

d):运行完成后打开工程文件,生成的实例工程文件是可以直接进行仿真的,点击project manager 管理栏中的run simulation即可进行仿真。我们的重点不是查看官方的仿真实例,我们要自己编写一个读写实例,现在可以关掉IP核的工程文件,重点放在实例工程上;

5:实例工程讲解

a):双击打开example_top文件,里面有很多描述和参数定义,输入输出端口定义,这些都不用修改,了解一下就好。往下翻到第412行Application interface ports,重点关注第413行到423行,这些端口都是数据的读写需要用到的端口 。可以在文件中查看端口的定义,有助于后面写代码端口的定义。第450行以后的代码都可以删掉,不用生成的实例文件,注意不要把endmodule删除了;

b):在工程中添加一个新的文件,用于编写我们自己的DDR3读写模块;

c):在编写代码前我们还是要分析一下DDR3的读写时序要求,下图为写数据时的时序要求,内容来源于前面Use rGuide下载问文档里面。

d):从上面写数据时序图可以看出,写数据需要10个输入输出信号来实现。我们来一一讲解信号的作用:

clk:系统时钟;

app\_cmd:读写操作命令,3'b000为写操作,3'b001为读操作;

app\_addr:地址线,写数据地址和读数据地址都走这条线;

app\_en:地址线有效使能信号,高有效;

app\_rdy:DDR3给你的信号,为高时表明UI已准备好接受命令;

app\_wdf\_mask:app\_wdf\_data 的掩码;

app\_wdf\_rdy:DDR3给你的信号,为高时表明写入数据FIFO已准备好接收数据;

app\_wdf\_data:写入的数据;

app\_wdf\_wren:数据有效使能信号,高有效;

app\_wdf\_end:高电平有效输入,表明当前时钟周期是app\_wdf\_data 上输入数据的最后一个周期,一般情况下可让app\_wdf\_end == app\_wdf\_wren;

e):对于这10个信号又可分为2个系统,地址系统和数据系统,clk为系统时钟。

地址系统:app\_cmd,app\_addr,app\_en,app\_rdy;

数据系统:app\_wdf\_mask,app\_wdf\_rdy,app\_wdf\_data,app\_wdf\_wren,app\_wdf\_end;

地址系统只关联地址有关的信号,数据系统就关联数据有关的信号,两者之间不应纠缠在一起,不然容易造成一些bug出现。从写数据时序图还可以看出,地址系统与数据系统之间的时序关系有三种:

第一种:地址与数据严格对其;

第二种:数据比地址先给一个周期;

第三种:数据比地址最多延迟2个周期;

地址系统有关信号严格按照时序要求对齐,数据系统有关信号严格按照时序要求对齐,地址系统与数据系统之间选择哪种关系,根据个人需求进行选择。

f):地址系统信号之间的关系:

当DDR3发出app\_rdy信号时表明已经准备好接收命令,可以发送app\_cmd命令和app\_addr地址,同时标志地址有效app\_en信号也要同时发出,只有app\_en为高时写入的地址才是有效的。

数据系统信号之间关系:

当DDR3发出app\_wdf\_rdy信号时,表明写入数据FIFO准备好接收数据,这时就要将要写入的数据发送给app\_wdf\_data,写入多少个地址就只能写入多少个数据,多给的数据会丢失。在写入app\_wdf\_data同时拉高app\_wdf\_wren信号,只有app\_wdf\_wren为高时写入的数据才是有效的。前面文章中讲过app\_wdf\_end == app\_wdf\_wren,所以可以将app\_wdf\_end进行app\_wdf\_wren同样的处理。app\_wdf\_mask信号为app\_wdf\_data数据的掩码,app\_wdf\_mask为1的位对应的数据将被屏蔽掉,本例中不使用掩码,可以赋值为全0(要注意app\_wdf\_mask信号的位宽);

g):读数据时序要求,下图为读数据时序图。

通过上图可以看出,读数据也需要用到地址系统,但是读数据只需要你给出地址和读出的数据个数就可以,数据个数可以理解为给了多少个地址,这个可以自由决定。发送地址后不是马上读出数据,从上图也可以看出发送完addr0之后时钟信号用双波浪符号表示中间省略多少个周期,毕竟DDR3也需要反应时间。DDR3准备好数据后,就会通过app\_rd\_data端口发出数据,同时给出app\_rd\_data\_valid信号,只有 app\_rd\_data\_valid为高时读出的数据才是有效数据;

h):读写时序要求就分析这么多,分析的比较简单,重在理解。需要详细分析,请在CSND里面搜索其他作者写的时序分析文章,这里就不在过多赘述。到此IP核、DDR3实例工程、时序分析都已完成,剩下的就是编写代码实现功能了,这个就交给天赋异禀的读者了,后面我会提供我的实例代码,供读者参考。

6:参考代码

以下代码可实现DDR3读写数据功能。

`timescale 1ns / 1ps

module ddr_app_module (

input i_sys_clk, //时钟

input i_sys_rst, //复位

input init_calib_complete, //DDR3初始完成

input app_rdy, //app_rdy

output reg [ 2 : 0 ] app_cmd, //读写命令

output reg app_en, //地址en

output reg [ 29 : 0 ] app_addr, //操作地址

input app_wdf_rdy, //app_wdf_rdy

output reg app_wdf_end, //app_wdf_end

output reg app_wdf_wren, //写数据有效en

output reg [ 127 : 0 ] app_wdf_data, //写数据

input [ 127 : 0 ] app_rd_data, //读数据

input app_rd_data_valid //读数据有效

);

localparam TEST_LEN = 8'd99;

reg [ 29 : 0 ] write_addr;

reg [ 29 : 0 ] read_addr;

reg app_write_req;

reg app_write_req_r0;

reg app_write_req_r1;

reg write_data_en;

reg app_read_req;

reg app_read_req_r0;

reg app_read_req_r1;

reg read_data_en;

reg [ 7 : 0 ] write_addr_cnt;

reg [ 7 : 0 ] write_data_cnt;

reg [ 7 : 0 ] read_addr_cnt;

reg [ 7 : 0 ] read_data_cnt;

always @ ( posedge i_sys_clk ) begin //写数据请求

if ( init_calib_complete == 1'b0 ) begin

app_write_req <= 1'b0;

app_write_req_r0 <= 1'b0;

app_write_req_r1 <= 1'b0;

end else begin

app_write_req_r0 <= init_calib_complete;

app_write_req_r1 <= app_write_req_r0;

app_write_req <= app_write_req_r0 & ( ~app_write_req_r1 );

end

end

always @ ( posedge i_sys_clk ) begin //写数据en

if ( init_calib_complete == 1'b0 ) begin

write_data_en <= 1'b0;

end else begin

if ( app_write_req == 1'b1 ) begin

write_data_en <= 1'b1;

end else begin

if ( write_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

write_data_en <= 1'b0;

end else begin

write_data_en <= write_data_en;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //读数据请求

if ( init_calib_complete == 1'b0 ) begin

app_read_req <= 1'b0;

app_read_req_r0 <= 1'b0;

app_read_req_r1 <= 1'b0;

end else begin

app_read_req_r0 <= write_data_en;

app_read_req_r1 <= app_read_req_r0;

app_read_req <= app_read_req_r1 & ( ~app_read_req_r0 );

end

end

always @ ( posedge i_sys_clk ) begin //读数据en

if ( init_calib_complete == 1'b0 ) begin

read_data_en <= 1'b0;

end else begin

if ( app_read_req == 1'b1 ) begin

read_data_en <= 1'b1;

end else begin

if ( read_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

read_data_en <= 1'b0;

end else begin

read_data_en <= read_data_en;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //app_en信号产生

if ( init_calib_complete == 1'b0 ) begin

app_en <= 1'b0;

end else begin

if ( app_write_req == 1'b1 || app_read_req == 1'b1 ) begin

app_en <= 1'b1;

end else begin

if ( ( write_addr_cnt == TEST_LEN || read_addr_cnt == TEST_LEN ) && app_rdy == 1'b1 ) begin

app_en <= 1'b0;

end else begin

app_en <= app_en;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //app_amd命令产生

if ( init_calib_complete == 1'b0 ) begin

app_cmd <= 3'b000;

end else begin

if ( read_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

app_cmd <= 3'b000;

end else begin

if ( app_read_req == 1'b1 ) begin

app_cmd <= 3'b001;

end else begin

app_cmd <= app_cmd;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //写数据地址

if ( init_calib_complete == 1'b0 ) begin

write_addr <= 30'h0;

end else begin

if ( write_data_en == 1'b1 && app_rdy == 1'b1 ) begin

write_addr <= write_addr + 4'h8;

end else begin

if ( write_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

write_addr <= write_addr + 4'h8;

end else begin

write_addr <= write_addr;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //读数据地址

if ( init_calib_complete == 1'b0 ) begin

read_addr <= 30'h0;

end else begin

if ( read_data_en == 1'b1 && app_rdy == 1'b1 ) begin

read_addr <= read_addr + 4'h8;

end else begin

if ( read_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

read_addr <= read_addr + 4'h8;

end else begin

read_addr <= read_addr;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //app_addr数据地址

if ( init_calib_complete == 1'b0 ) begin

app_addr <= 30'h0;

end else begin

if ( app_write_req == 1'b1 ) begin

app_addr <= write_addr;

end else begin

if ( app_read_req == 1'b1 ) begin

app_addr <= read_addr;

end else begin

if ( write_data_en == 1'b1 && app_rdy == 1'b1 ) begin

app_addr <= write_addr + 4'h8;

end else begin

if ( read_data_en == 1'b1 && app_rdy == 1'b1 ) begin

app_addr <= read_addr + 4'h8;

end else begin

app_addr <= app_addr;

end

end

end

end

end

end

always @ ( posedge i_sys_clk ) begin //写地址计数器

if ( init_calib_complete == 1'b0 ) begin

write_addr_cnt <= 8'd0;

end else begin

if( write_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

write_addr_cnt <= 8'd0;

end else begin

if ( write_data_en == 1'b1 && app_rdy == 1'b1 ) begin

write_addr_cnt <= write_addr_cnt + 1'b1;

end else begin

write_addr_cnt <= write_addr_cnt;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //读地址计数器

if ( init_calib_complete == 1'b0 ) begin

read_addr_cnt <= 8'd0;

end else begin

if( read_addr_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

read_addr_cnt <= 8'd0;

end else begin

if ( read_data_en == 1'b1 && app_rdy == 1'b1 ) begin

read_addr_cnt <= read_addr_cnt + 1'b1;

end else begin

read_addr_cnt <= read_addr_cnt;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //写数据有效

if ( init_calib_complete == 1'b0 ) begin

app_wdf_wren <= 1'b0;

end else begin

if ( write_addr_cnt == TEST_LEN && app_wdf_rdy == 1'b1 ) begin

app_wdf_wren <= 1'b0;

end else begin

if ( app_write_req == 1'b1 ) begin

app_wdf_wren <= 1'b1;

end else begin

app_wdf_wren <= app_wdf_wren;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //app_wdf_end == app_wdf_wren

if ( init_calib_complete == 1'b0 ) begin

app_wdf_end <= 1'b0;

end else begin

if ( write_addr_cnt == TEST_LEN && app_wdf_rdy == 1'b1 ) begin

app_wdf_end <= 1'b0;

end else begin

if ( app_write_req == 1'b1 ) begin

app_wdf_end <= 1'b1;

end else begin

app_wdf_end <= app_wdf_end;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //产生写入的数据

if ( i_sys_rst == 1'b0 ) begin

app_wdf_data <= 128'h0;

end else begin

if ( app_wdf_rdy == 1'b1 && app_wdf_wren == 1'b1 ) begin

app_wdf_data <= app_wdf_data + 1'b1;

end else begin

app_wdf_data <= app_wdf_data;

end

end

end

always @ ( posedge i_sys_clk ) begin //写数据计数器

if ( i_sys_rst == 1'b0 ) begin

write_data_cnt <= 8'd0;

end else begin

if ( write_data_cnt == TEST_LEN && app_wdf_rdy == 1'b1 ) begin

write_data_cnt <= 8'd0;

end else begin

if ( app_wdf_wren == 1'b1 && app_wdf_rdy == 1'b1 ) begin

write_data_cnt <= write_data_cnt + 1'b1;

end else begin

write_data_cnt <= write_data_cnt;

end

end

end

end

always @ ( posedge i_sys_clk ) begin //读数据计数器

if ( i_sys_rst == 1'b0 ) begin

read_data_cnt <= 8'd0;

end else begin

if ( read_data_cnt == TEST_LEN && app_rdy == 1'b1 ) begin

read_data_cnt <= 8'd0;

end else begin

if ( app_rd_data_valid == 1'b1 ) begin

read_data_cnt <= read_data_cnt + 1'b1;

end else begin

read_data_cnt <= read_data_cnt;

end

end

end

end

endmodule

7:仿真测试

本例中测试数据长度为100,写入0~99,读出0~99即为读写数据正确,仿真结果如下,供参考。DDR3数据读写测试讲解到此结束,感谢各位读者阅读,希望对你有所帮助。后附工程文件下载链接,欢迎下载测试。

工程文件下载链接:

https://download.youkuaiyun.com/download/ForeveryMissYou/21358108

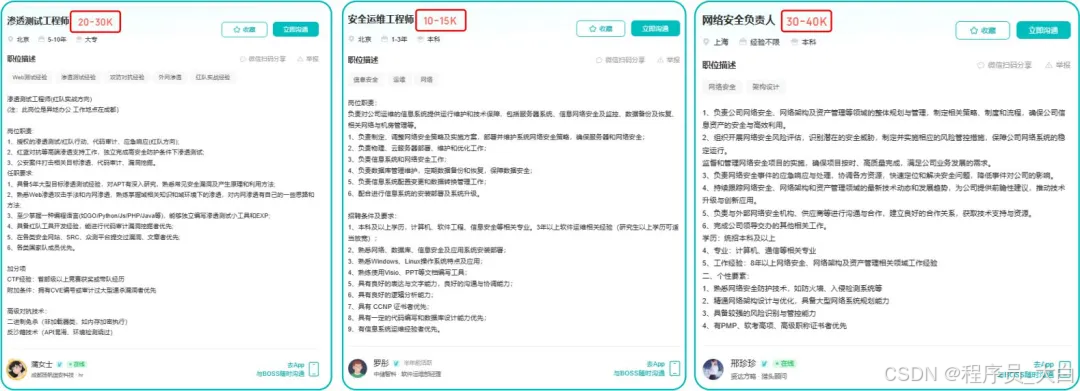

这两年,IT行业面临经济周期波动与AI产业结构调整的双重压力,确实有很多运维与网络工程师因企业缩编或技术迭代而暂时失业。

很多人都在提运维网工失业后就只能去跑滴滴送外卖了,但我想分享的是,对于运维人员来说,即便失业以后仍然有很多副业可以尝试。

网工/运维/测试副业方向

运维网工,千万不要再错过这些副业机会!

第一个是知识付费类副业:输出经验打造个人IP

在线教育平台讲师

操作路径:在慕课网、极客时间等平台开设《CCNA实战》《Linux运维从入门到精通》等课程,或与培训机构合作录制专题课。

收益模式:课程销售分成、企业内训。

技术博客与公众号运营

操作路径:撰写网络协议解析、故障排查案例、设备评测等深度文章,通过公众号广告、付费专栏及企业合作变现。

收益关键:每周更新2-3篇原创,结合SEO优化与社群运营。

第二个是技术类副业:深耕专业领域变现

企业网络设备配置与优化服务

操作路径:为中小型企业提供路由器、交换机、防火墙等设备的配置调试、性能优化及故障排查服务。可通过本地IT服务公司合作或自建线上接单平台获客。

收益模式:按项目收费或签订年度维护合同。

远程IT基础设施代维

操作路径:通过承接服务器监控、日志分析、备份恢复等远程代维任务。适合熟悉Zabbix、ELK等技术栈的工程师。

收益模式:按工时计费或包月服务。

网络安全顾问与渗透测试

操作路径:利用OWASP Top 10漏洞分析、Nmap/BurpSuite等工具,为企业提供漏洞扫描、渗透测试及安全加固方案。需考取CISP等认证提升资质。

收益模式:单次渗透测试报告收费;长期安全顾问年费。

比如不久前跟我一起聊天的一个粉丝,他自己之前是大四实习的时候做的运维,发现运维7*24小时待命受不了,就准备转网安,学了差不多2个月,然后开始挖漏洞,光是补天的漏洞奖励也有个四五千,他说自己每个月的房租和饭钱就够了。

为什么我会推荐你网安是运维和网工测试人员的绝佳副业&转型方向?

1.你的经验是巨大优势: 你比任何人都懂系统、网络和架构。漏洞挖掘、内网渗透、应急响应,这些核心安全能力本质上是“攻击视角下的运维”。你的运维背景不是从零开始,而是降维打击。

2.越老越吃香,规避年龄危机: 安全行业极度依赖经验。你的排查思路、风险意识和对复杂系统的理解能力,会随着项目积累而愈发珍贵,真正做到“姜还是老的辣”。

3.职业选择极其灵活: 你可以加入企业成为安全专家,可以兼职“挖洞“获取丰厚奖金,甚至可以成为自由顾问。这种多样性为你提供了前所未有的抗风险能力。

4.市场需求爆发,前景广阔: 在国家级政策的推动下,从一线城市到二三线地区,安全人才缺口正在急剧扩大。现在布局,正是抢占未来先机的黄金时刻。

网工运维测试转行学习网络安全路线

(一)第一阶段:网络安全筑基

1. 阶段目标

你已经有运维经验了,所以操作系统、网络协议这些你不是零基础。但要学安全,得重新过一遍——只不过这次我们是带着“安全视角”去学。

2. 学习内容

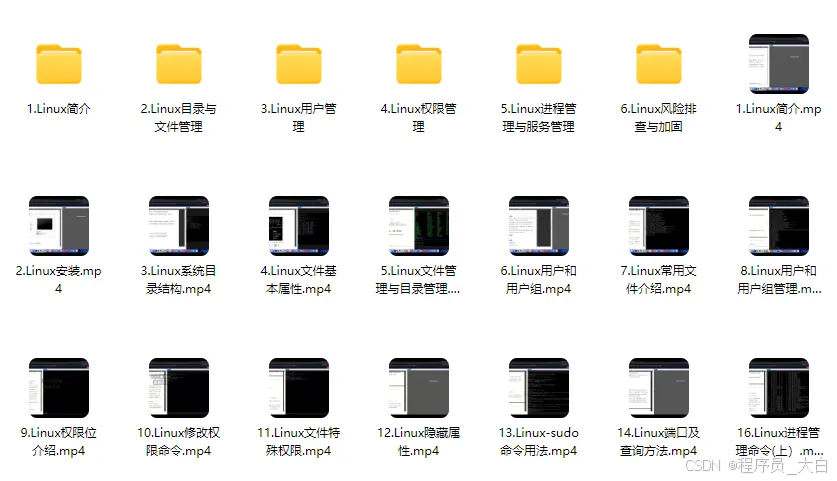

**操作系统强化:**你需要重点学习 Windows、Linux 操作系统安全配置,对比运维工作中常规配置与安全配置的差异,深化系统安全认知(比如说日志审计配置,为应急响应日志分析打基础)。

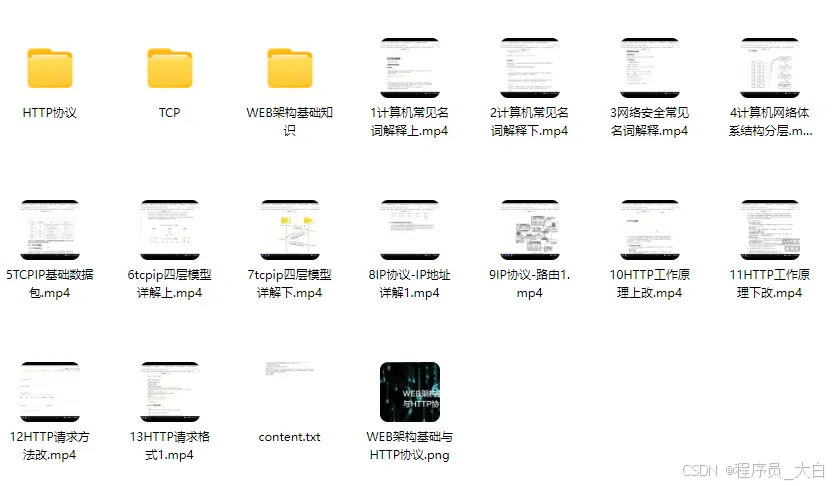

**网络协议深化:**结合过往网络协议应用经验,聚焦 TCP/IP 协议簇中的安全漏洞及防护机制,如 ARP 欺骗、TCP 三次握手漏洞等(为 SRC 漏扫中协议层漏洞识别铺垫)。

**Web 与数据库基础:**补充 Web 架构、HTTP 协议及 MySQL、SQL Server 等数据库安全相关知识,了解 Web 应用与数据库在网安中的作用。

**编程语言入门:**学习 Python 基础语法,掌握简单脚本编写,为后续 SRC 漏扫自动化脚本开发及应急响应工具使用打基础。

**工具实战:**集中训练抓包工具(Wireshark)、渗透测试工具(Nmap)、漏洞扫描工具(Nessus 基础版)的使用,结合模拟场景练习工具应用(掌握基础扫描逻辑,为 SRC 漏扫工具进阶做准备)。

(二)第二阶段:漏洞挖掘与 SRC 漏扫实战

1. 阶段目标

这阶段是真正开始“动手”了。信息收集、漏洞分析、工具联动,一样不能少。

熟练运用漏洞挖掘及 SRC 漏扫工具,具备独立挖掘常见漏洞及 SRC 平台漏扫实战能力,尝试通过 SRC 挖洞搞钱,不管是低危漏洞还是高危漏洞,先挖到一个。

2. 学习内容

信息收集实战:结合运维中对网络拓扑、设备信息的了解,强化基本信息收集、网络空间搜索引擎(Shodan、ZoomEye)、域名及端口信息收集技巧,针对企业级网络场景开展信息收集练习(为 SRC 漏扫目标筛选提供支撑)。

漏洞原理与分析:深入学习 SQL 注入、CSRF、文件上传等常见漏洞的原理、危害及利用方法,结合运维工作中遇到的类似问题进行关联分析(明确 SRC 漏扫重点漏洞类型)。

工具进阶与 SRC 漏扫应用:

-

系统学习 SQLMap、BurpSuite、AWVS 等工具的高级功能,开展工具联用实战训练;

-

专项学习 SRC 漏扫流程:包括 SRC 平台规则解读(如漏洞提交规范、奖励机制)、漏扫目标范围界定、漏扫策略制定(全量扫描 vs 定向扫描)、漏扫结果验证与复现;

-

实战训练:使用 AWVS+BurpSuite 组合开展 SRC 平台目标漏扫,练习 “扫描 - 验证 - 漏洞报告撰写 - 平台提交” 全流程。

SRC 实战演练:选择合适的 SRC 平台(如补天、CNVD)进行漏洞挖掘与漏扫实战,积累实战经验,尝试获取挖洞收益。

恭喜你,如果学到这里,你基本可以下班搞搞副业创收了,并且具备渗透测试工程师必备的「渗透技巧」、「溯源能力」,让你在黑客盛行的年代别背锅,工作实现升职加薪的同时也能开创副业创收!

如果你想要入坑黑客&网络安全,笔者给大家准备了一份:全网最全的网络安全资料包需要保存下方图片,微信扫码即可前往获取!

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

优快云大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

(三)第三阶段:渗透测试技能学习

1. 阶段目标

全面掌握渗透测试理论与实战技能,能够独立完成渗透测试项目,编写规范的渗透测试报告,具备渗透测试工程师岗位能力,为护网红蓝对抗及应急响应提供技术支撑。

2. 学习内容

渗透测试核心理论:系统学习渗透测试流程、方法论及法律法规知识,明确渗透测试边界与规范(与红蓝对抗攻击边界要求一致)。

实战技能训练:开展漏洞扫描、漏洞利用、电商系统渗透测试、内网渗透、权限提升(Windows、Linux)、代码审计等实战训练,结合运维中熟悉的系统环境设计测试场景(强化红蓝对抗攻击端技术能力)。

工具开发实践:基于 Python 编程基础,学习渗透测试工具开发技巧,开发简单的自动化测试脚本(可拓展用于 SRC 漏扫自动化及应急响应辅助工具)。

报告编写指导:学习渗透测试报告的结构与编写规范,完成多个不同场景的渗透测试报告撰写练习(与 SRC 漏洞报告、应急响应报告撰写逻辑互通)。

(四)第四阶段:企业级安全攻防(含红蓝对抗)、应急响应

1. 阶段目标

掌握企业级安全攻防、护网红蓝对抗及应急响应核心技能,考取网安行业相关证书。

2. 学习内容

护网红蓝对抗专项:

-

红蓝对抗基础:学习护网行动背景、红蓝对抗规则(攻击范围、禁止行为)、红蓝双方角色职责(红队:模拟攻击;蓝队:防御检测与应急处置);

-

红队实战技能:强化内网渗透、横向移动、权限维持、免杀攻击等高级技巧,模拟护网中常见攻击场景;

-

蓝队实战技能:学习安全设备(防火墙、IDS/IPS、WAF)联动防御配置、安全监控平台(SOC)使用、攻击行为研判与溯源方法;

-

模拟护网演练:参与团队式红蓝对抗演练,完整体验 “攻击 - 检测 - 防御 - 处置” 全流程。

应急响应专项: -

应急响应流程:学习应急响应 6 步流程(准备 - 检测 - 遏制 - 根除 - 恢复 - 总结),掌握各环节核心任务;

-

实战技能:开展操作系统入侵响应(如病毒木马清除、异常进程终止)、数据泄露应急处置、漏洞应急修补等实战训练;

-

工具应用:学习应急响应工具(如 Autoruns、Process Monitor、病毒分析工具)的使用,提升处置效率;

-

案例复盘:分析真实网络安全事件应急响应案例(如勒索病毒事件),总结处置经验。

其他企业级攻防技能:学习社工与钓鱼、CTF 夺旗赛解析等内容,结合运维中企业安全防护需求深化理解。

证书备考:针对网安行业相关证书考试内容(含红蓝对抗、应急响应考点)进行专项复习,参加模拟考试,查漏补缺。

运维网工测试转行网络攻防知识库分享

网络安全这行,不是会几个工具就能搞定的。你得有体系,懂原理,能实战。尤其是从运维转过来的,别浪费你原来的经验——你比纯新人强多了。

但也要沉得住气,别学了两天Web安全就觉得自己是黑客了。内网、域渗透、代码审计、应急响应,要学的还多着呢。

如果你真的想转,按这个路子一步步走,没问题。如果你只是好奇,我劝你再想想——这行要持续学习,挺累的,但也是真有意思。

关于如何学习网络安全,笔者也给大家整理好了全套网络安全知识库,需要的可以扫码获取!

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

优快云大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

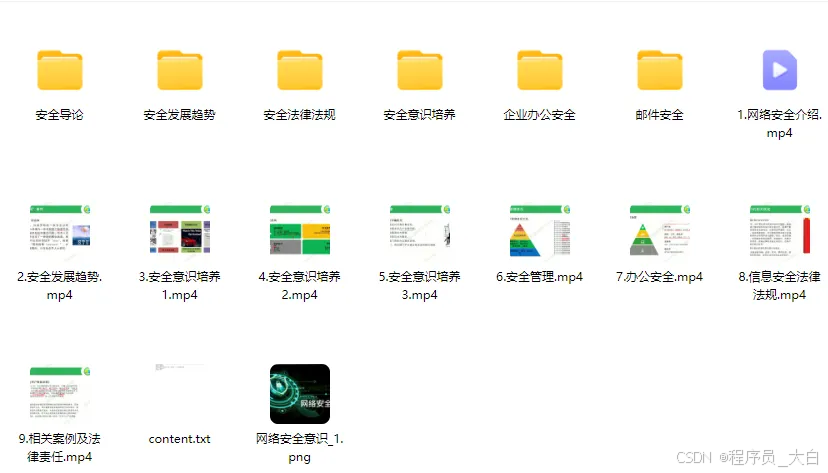

1、网络安全意识

2、Linux操作系统

3、WEB架构基础与HTTP协议

4、Web渗透测试

5、渗透测试案例分享

6、渗透测试实战技巧

7、攻防对战实战

8、CTF之MISC实战讲解

关于如何学习网络安全,笔者也给大家整理好了全套网络安全知识库,需要的可以扫码获取!

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?