课题:Datapath基本逻辑组件设计

一、实验目的

1.掌握程序计数器(PC)、多路选择器、符号扩展模块及简单加法器的原理及原理

2. ALU基本模块的设计与实现

3. 基于Xilinx ISE软件平台的逻辑组件仿真验证方法

二、实验设备

1.装有 ISE Design Suite 14.7 的计算机一台

2.EDK-3 SA ISE 实验平台

三、实验任务

1.设计并验证程序计数器(PC)的功能

2.设计并验证多路选择器的功能

3.设计并验证符号扩展模块的功能

4.设计并验证简单加法器的功能

四、实验原理

程序计数器(PC)用于控制机器指令的执行顺序,实际上是存放指令的内存地址。计算机由指令指针来控制程序指令的顺序执行,CPU根据这个地址来读取当前要执行的指令,每执行一条指令都要改变PC的值。正常运行时,输出并更新当前PC值。以后要完成的简单计算机内存组织形式为32bit*512,指令为32位,因此地址宽度为9位。又因为内存数据宽度为32位,所以每次PC加1而不是加4。

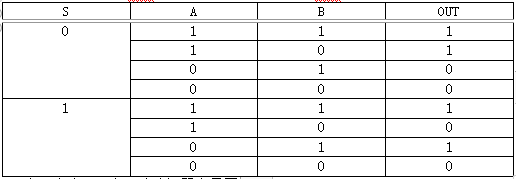

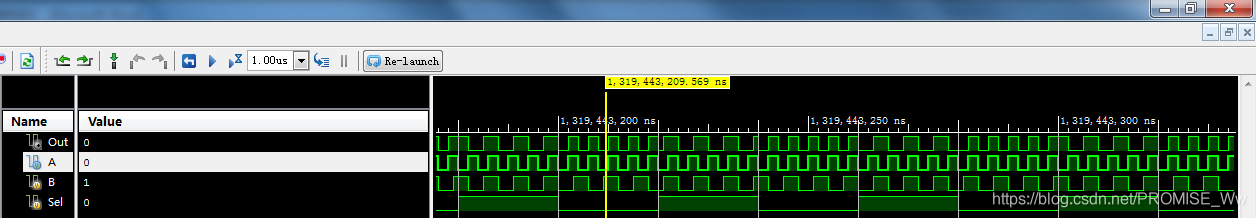

数据选择器是基本的逻辑电路,在Verilog HDL中一般用case语句生成一个多路选择器,但如果是二路选择器也可以采用三目运算符?实现。(参考源程序包括多个数据选择器)。

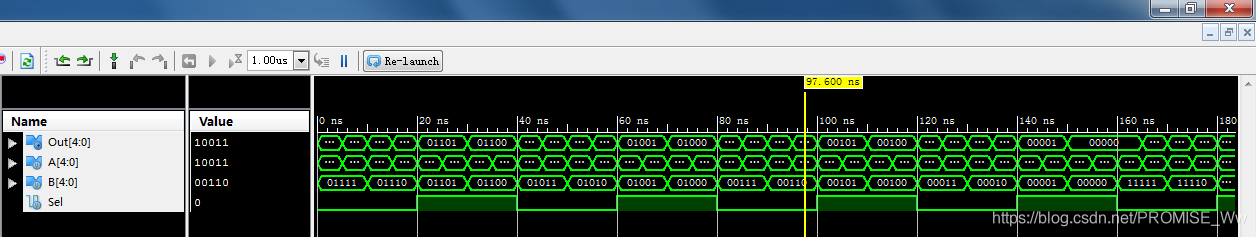

符号扩展模块用于将短字长数据扩展成长字长数据。由于在计算机内部整数均以补码形式表示,按照补码运算规则对整数进行字长扩展时最高位填充的数据位与数据本身的符号位有关。如果数据大于零即最高符号位为0则高位扩展填充位均为0;如果数据小于零即最高符号位为1则高位扩展填充位均为1。本模块主要用于CPU设计中将16位的输入扩展为32位的输出。按照以上的扩展规则,当第16位为1时,扩展位用1填充,为0时扩展位用0填充。

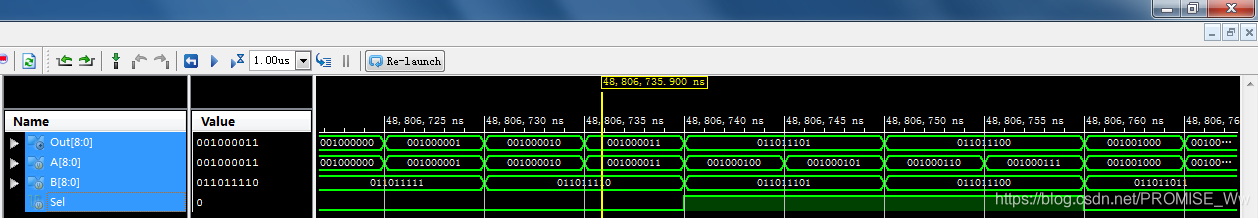

加法器实现两个数的相加,在Verilog HDL中只需要直接用’+’就会自动生成加法器,本实验所做加法器将在后面的CPU设计中使用。

五、部分代码

程序计数器(PC):

module PcTest;

// Inputs

reg Clk;

reg Rst;

// Outputs

wire [8:0] CntPc;

// Instantiate the Unit Under Test (UUT)

Pc uut (

.Clk(Clk),

.Rst(Rst),

.CntPc(CntPc)

);

always #5 Clk=~Clk;

initial begin

// Initialize Inputs

Clk = 1;

Rst = 0;

// Wait 100 ns for global reset to finish

#10 Rst=1;

#20 Rst=0;

#100 $stop;

// Add stimulus here

end

endmodule

多路选择器(以二路为例):

module Mux1Test;

// Inputs

reg A;

reg B;

reg Sel;

// Outputs

wire Out;

// Instantiate the Unit Under Test (UUT)

Mux1 uut (

.A(A),

.B(B),

.Sel(Sel),

.Out(Out)

);

always #20 Sel=~Sel;

always #2 A=~A;

always #3 B=~B;

initial begin

// Initialize Inputs

A = 0;

B = 0;

Sel = 0;

// Wait 100 ns for global reset to finish

#100;

#100 $stop;

// Add stimulus here

end

endmodule

符号扩展模块:

module SignExtTest;

// Inputs

reg [15:0] In16Bit;

// Outputs

wire [31:0] Out32Bit;

// Instantiate the Unit Under Test (UUT)

SignExt uut (

.In16Bit(In16Bit),

.Out32Bit(Out32Bit)

);

always #5 In16Bit=In16Bit-1;

initial begin

// Initialize Inputs

In16Bit = 10;

// Wait 100 ns for global reset to finish

#100 $finish;

// Add stimulus here

end

endmodule

简单加法器:

module AdderTest;

// Inputs

reg [31:0] InA;

reg [31:0] InB;

// Outputs

wire [31:0] Out;

// Instantiate the Unit Under Test (UUT)

Adder uut (

.InA(InA),

.InB(InB),

.Out(Out)

);

always #5 InA=InA+1;

always #6 InB=InB-1;

initial begin

// Initialize Inputs

InA = 0;

InB = 32'b1111111111111111111111111111111;

// Wait 100 ns for global reset to finish

#100 $finish;

// Add stimulus here

end

endmodule

六、仿真结果与解释

程序计数器PC:计算机由指令指针来控制程序指令的顺序执行,CPU根据这个地址来读取当前要执行的指令,每执行一条指令都要改变PC的值。每10毫秒记录一次数据,指示下一个数据地址。

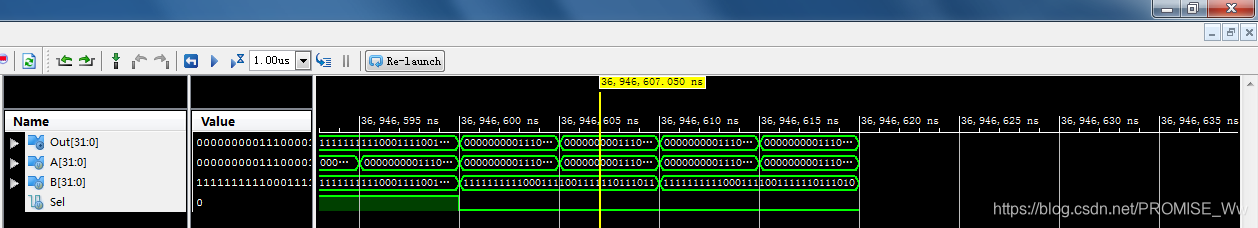

多路选择器:依据sel值,当A与B的值是否与sel相同,决定输出的值。

四路、八路、三十二路选择器也是同理。

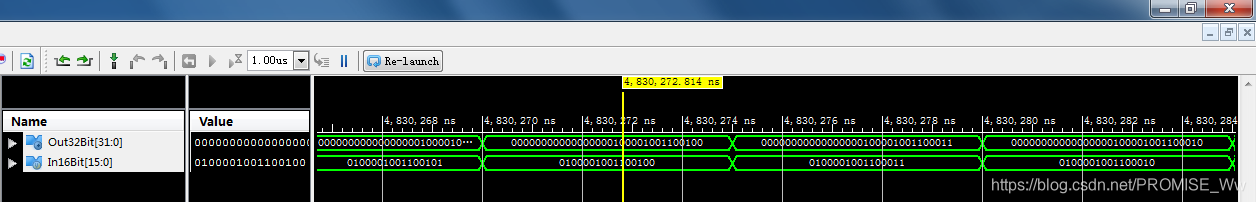

符号扩展模块:将短字长数据扩展成长字长数据,当第16位为1时,扩展位用1填充,为0时扩展位用0填充。

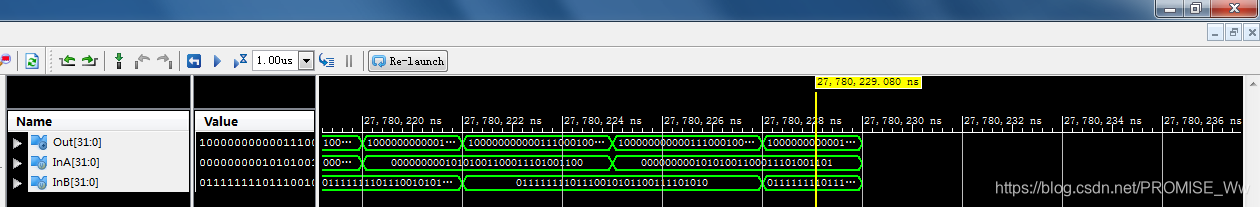

简单加法器:三十二位二进制补码加减,但是会出现数值溢出的情况造成数据错误。

涉及的源代码链接已上传:https://download.youkuaiyun.com/download/promise_ww/11801301

本文介绍了一项关于Datapath基本逻辑组件设计的实验,涵盖了程序计数器(PC)、多路选择器、符号扩展模块及简单加法器的设计与实现。通过Xilinx ISE软件平台进行仿真验证,详细阐述了各组件的工作原理和实现过程。

本文介绍了一项关于Datapath基本逻辑组件设计的实验,涵盖了程序计数器(PC)、多路选择器、符号扩展模块及简单加法器的设计与实现。通过Xilinx ISE软件平台进行仿真验证,详细阐述了各组件的工作原理和实现过程。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?