题目来源:模块 addsub - HDLBits

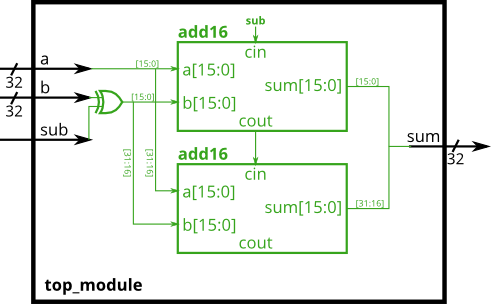

可以通过选择性地否定其中一个 inputs,从 adder 构建 adder-subtractor,这相当于反转 input 然后加 1。最终结果是一个可以执行两个作的电路:(a + b + 0) 和 (a + ~b + 1)。你得到了一个 16 位的 adder 模块,你需要实例化它两次:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );使用 32 位宽的 XOR 门,当 sub 为 1 时反转 b 输入。(这也可以看作是 b[31:0] XOR 和 sub 复制 32 次。

Verilog代码:

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire cout1,cout2,cout3,cout4;

wire [15:0]sum1,sum2,sum3,sum4;

add16 add161(.a(a[15:0]),.b(b[15:0]),.cin(1'b0),.sum(sum1[15:0]),.cout(cout1));

add16 add162(.a(a[31:16]),.b(b[31:16]),.cin(cout1),.sum(sum2[15:0]),.cout(cout2));

add16 add163(.a(a[15:0]),.b(~b[15:0]),.cin(1'b1),.sum(sum3[15:0]),.cout(cout3));

add16 add164(.a(a[31:16]),.b(~b[31:16]),.cin(cout3),.sum(sum4[15:0]),.cout(cout4));

assign sum = (sub==1'b0)?{sum2,sum1}:{sum4,sum3};

endmodule我这里是例化了四次add模块,sub为1例化2次,sub为0例化2次。不知道仅例化2次能不能实现?

1179

1179

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?