一个实现vcs自动化仿真的makefile模板

vcs的安装可以参考我另外一篇文章【点这儿】

makefile简单介绍

个人理解就是一种类似脚本的东西。

写一个名字叫Makefile的文件,里面放很多块shell命令,为每一块命令分配一个自定义名称(就像打包一样),再把包之间像树状图一样连起来。

这样以来,在终端输入一个简单的自定义名称,Makefile就能帮你运行相应的那一大堆命令。如果这个名称下面还连接(一种依赖关系)了其他块的名称,那么这些被依赖的命令块也会被执行。

所以,说白了就是把在一大串命令写到一个文本里面,然后用一个简单的名字替代了。

当然里面也有很多复杂功能,但是这里不赘述了。

要想使用makefile,需要先安装

$ sudo apt-get install make

makefile & vcs

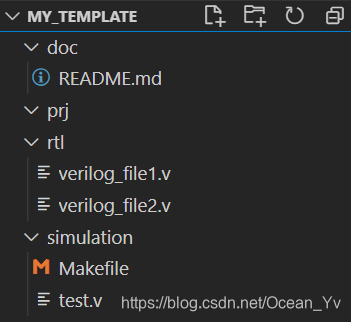

文件结构

如下:

/doc:放各种设计文档、说明文档、波形示例图

/prj:放工程文件,就是IDE自动生成的一大堆东西

/rtl:放源代码,可以有子文件夹

simulation:放Makefile、testbench,以及执行make命令之后生成的一系列文件

makefile文件内容

.PHONY:exe_file sim check cov watch_wave clean verdi

#使用说明:

# 使用前只需要修改OUTPUT、VERILOG_NAME、TIMESCALE三个变量,以及vpath

# 执行最开始可以执行[make check]检查语法错误

# 执行[make]默认执行编译并保存波形到wave.vpd文件

# 之后可以执行[make watch_wave]、[make cov]查看波形、查看覆盖率

# 执行[make sim]可以打开仿真

# 执行[make clean]可以删除过程文件

#路径与文件名定义,是需要根据工程修改的变量

vpath %.v ../rtl #放置源代码的路径,多个路径用空格隔开

OUTPUT:=mult_top #输出文件的名称

VERILOG_NAME:= test.v verilog_file1.v verilog_file2.v #仿真文件以及源代码文件

TIMESCALE:=1ns/1ps #仿真时间单位

#变量定义

VPD_NAME:=${OUTPUT}_wave.vpd

LOG_PATH:=./log

#代码覆盖率相关

CM = -cm line+cond+fsm+branch+tgl

CM_NAME = -cm_name ${OUTPUT}

CM_DIR = -cm_dir ./${OUTPUT}.vdb

SIM:=./${OUTPUT} \

-gui \

-l ${LOG_PATH}/run.log \

${CM} \

${CM_NAME} \

${CM_DIR}

VCS:=vcs -full64 -R -debug_all -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed \

-timescale=${TIMESCALE} \

-o ${OUTPUT} \

-l ${LOG_PATH}/report.log \

+define+DUMP_VPD \

+define+DUMP_FSDB \

-P /home/自定义路径/synopsys/verdi_2016.06-1/share/PLI/VCS/LINUXAMD64/novas.tab \

/home/自定义路径/synopsys/verdi_2016.06-1/share/PLI/VCS/LINUXAMD64/pli.a \

+vpdfile+${VPD_NAME} \

${CM} \

${CM_NAME} \

${CM_DIR}

VLOGAN:=vlogan -full64 \

-l ${LOG_PATH}/check.log

MID_FILE:=csrc DVEfiles .vlogansetup.args *.daidir *.key *.DB

#目标定义

exe_file:log ${VERILOG_NAME}

${VCS} $^

sim:exe_file

${SIM} &

check:log ${VERILOG_NAME} #检查语法错误

${VLOGAN} $^

log:

mkdir log

cov:

dve -full64 -covdir *.vdb &

watch_wave:

dve -vpd ${VPD_NAME} &

verdi: ${VERILOG_NAME}

verdi $^ -ssf rtl.fsdb

clean:

rm -r ${MID_FILE} ${OUTPUT} *log *.vdb *.vpd

才知道优快云居然不支持makefile语法高亮!!!

把上面的代码复制到自己的makefile文件里面,根据vcs的安装路径修改39和40行的路径、根据自己的文件结构修改11-15行的内容就好了,感觉注释得还算易懂

testbench

为了收集调试信息,需要在testbench文件中加入以下内容,一些参数可以根据自己的实际使用需求进行调整。

initial

begin

`ifdef DUMP_VPD

$vcdpluson();

`endif

end

`ifdef DUMP_FSDB

initial

begin

$fsdbDumpfile("rtl.fsdb");

$fsdbDumpvars;

#12500 $finish;

end

`endif

使用

执行makefile的时候要把终端路径换到/simulation下,个人常用的流程如下:

- 流程1:

一般用在代码基本调通了的情况下

make check #检查语法错误

make #静默仿真,并生成波型文件、覆盖率文件

make watch_wave #查看波型

make cov #查看代码覆盖率,根据个人需求选择是否使用

make clean #清理上面几步产生的文件还眼睛一个清静,根据实际需要执行

- 流程2:

用在还要狂改代码的情况下

make check #检查语法错误

make sim #打开软件仿真,不会生成波形文件和覆盖率文件,但是很方便

make clean #清理上面几步产生的文件

至此,欢迎提问/建议/指点

1641

1641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?