P3 学习心得

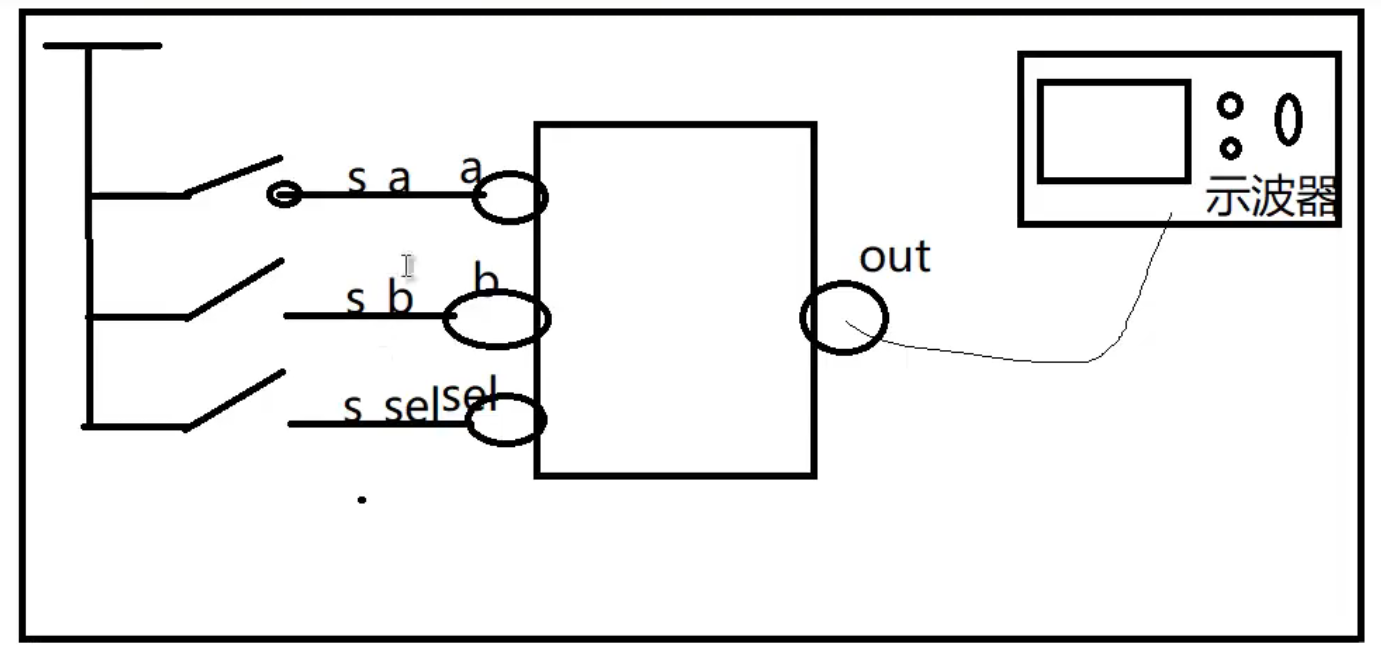

对testbench的理解:tb就是DUT的外壳,在DUT的input连接上一个类似开关的器件,在代码中以寄存器的方式存在;output的信号需要通过“示波器”来看,所以用wire的形式表现。

P4心得

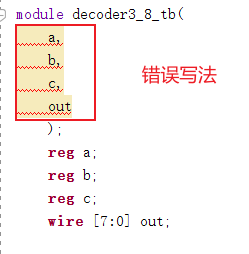

testbench中的信号不需要在括号中声明,因为只有输入和输出端口才需要在括号内声明

P5心得

①计数器的声明

reg [24:0] cnt;

其实映射到电路中是一个寄存器,不仅仅是作为代码的变量

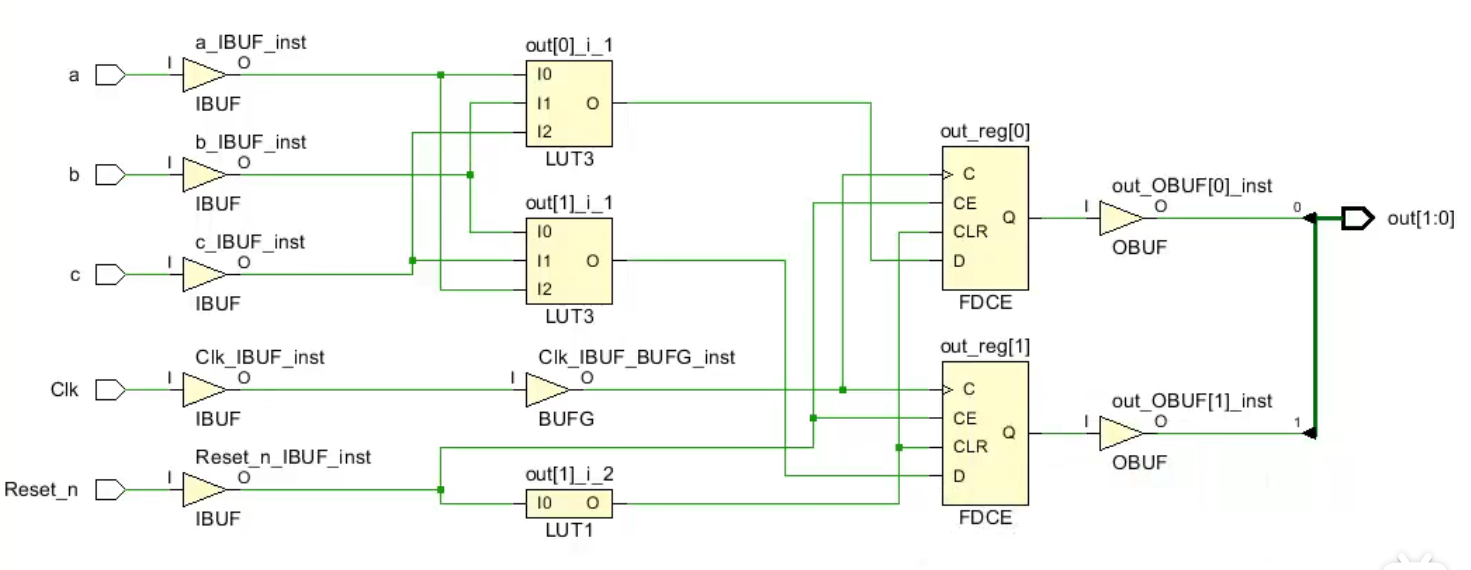

② 代码分为计数器部分和控制LED部分,将两者分开写,分别用always写的话,综合出来的电路会更简单

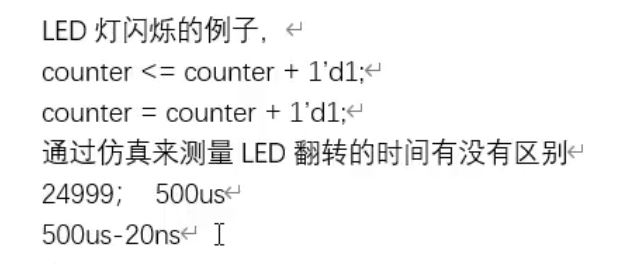

③ 计数器在24999999的那个周期就会变成25000000,所以判断条件不是cnt == 25000000而是24999999

P7心得

参数化

.v中添加

parameter CMT 2499;

testbench中例化.v文件通过defparam或者例化赋值的方式修改参数值

led led_u #(.CMT(249));

defparam led_u.CMT = 249;

P10 心得

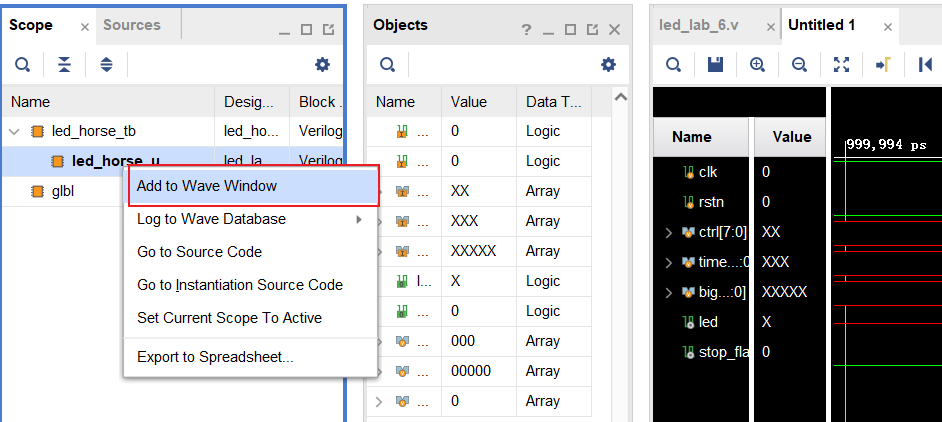

- vivado想查看设计的内部信号,通过以下方式

- ctrl+鼠标滚轮可以放大和缩小波形

- 写代码的时候,对不同的功能用不同的always写,不要写到一块,这样很难综合到电路

P11 学习心得

阻塞赋值和非阻塞赋值

采用阻塞赋值存在的缺陷:当两行代码顺序不同,综合出来的电路会不一样

例如

c = a + b

out = c + d

下面这个结果与非阻塞一致

out = c + d

c = a + b

综合出来的电路不一样,结果也会不一样

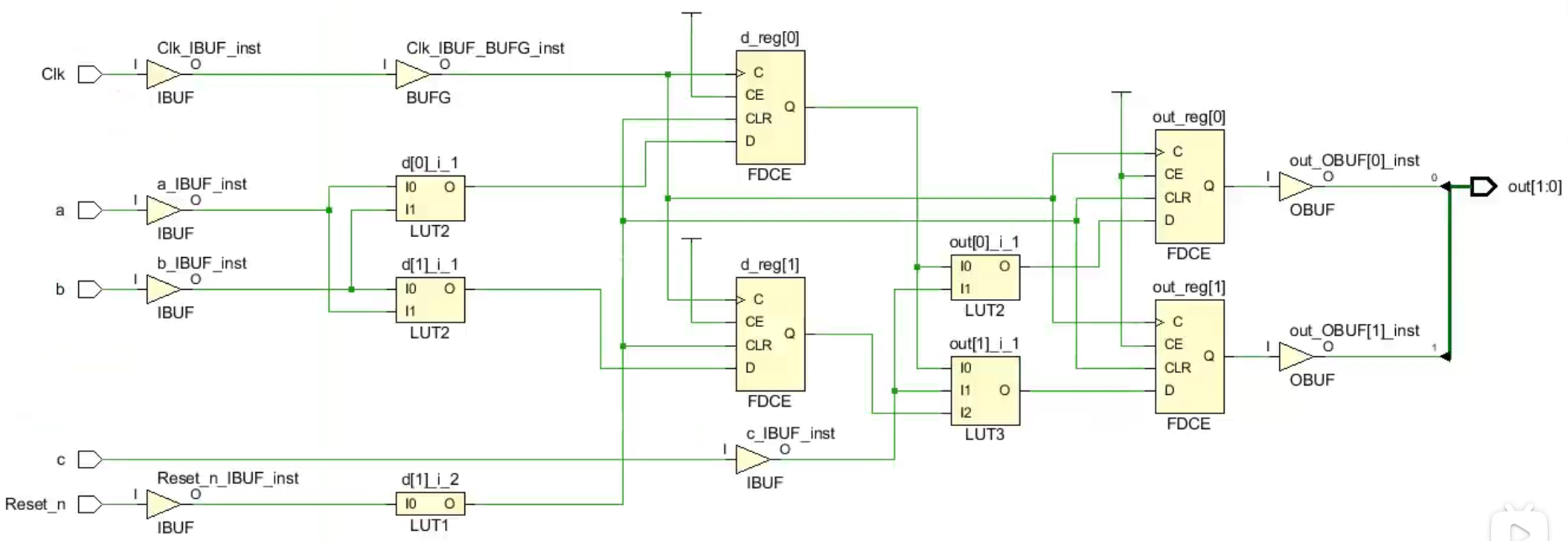

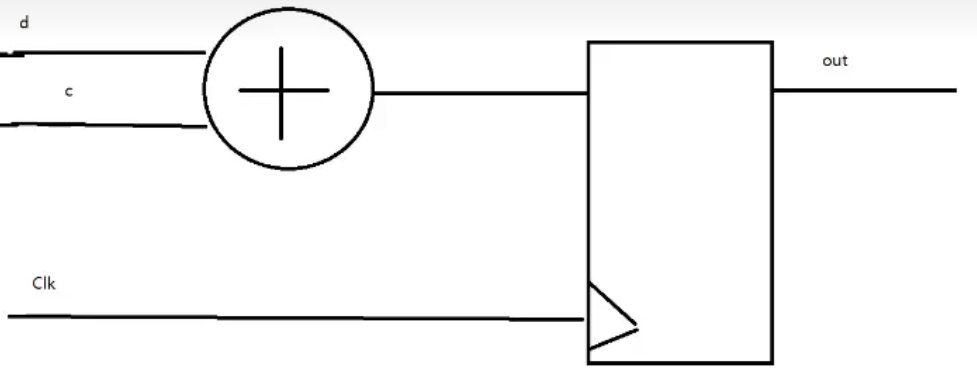

非阻塞赋值综合成电路就是D触发器

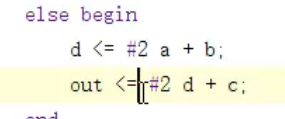

以下的写法能够仿真出接近实际状态的波形,虽然是不可综合的,但是软件在综合的时候会自动忽略掉#2的延迟,不需要注释掉

注意要点

P12

1秒除以波特率表示为 传输1bit所需要的时间

本文分享了在学习VHDL和Verilog过程中关于testbench的使用心得,包括DUT封装、信号声明、计数器设计、参数化、Vivado工具应用以及阻塞与非阻塞赋值的区别。

本文分享了在学习VHDL和Verilog过程中关于testbench的使用心得,包括DUT封装、信号声明、计数器设计、参数化、Vivado工具应用以及阻塞与非阻塞赋值的区别。

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?