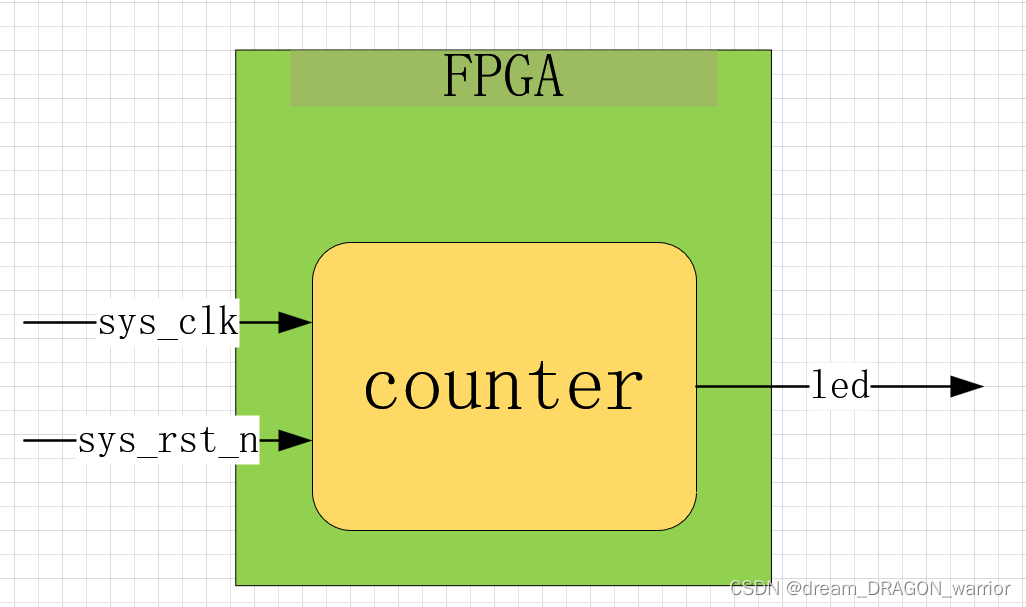

module counter #(

parameter MAX_CNT_HALF_1SEC = 25'd25_000_000

)

(

input wire sys_clk ,

input wire sys_rst_n ,

output reg led

);

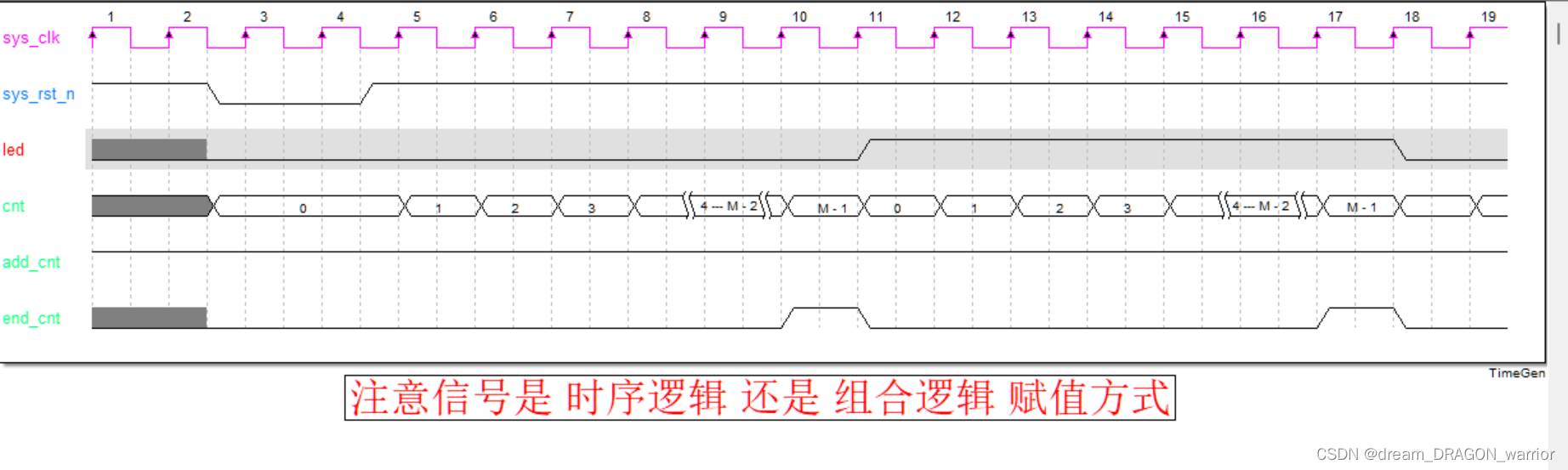

reg [24:00] cnt_half_1sec ; // 25 bit

wire add_cnt_half_1sec ;

wire end_cnt_half_1sec ;

// parameter MAX_CNT_HALF_1SEC = 25_000_000 ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_half_1sec <= 0;

end else begin

if(add_cnt_half_1sec) begin

if(end_cnt_half_1sec) begin

cnt_half_1sec <= 0;

end else begin

cnt_half_1sec <= cnt_half_1sec + 25'h1;

end

end else begin

cnt_half_1sec <= cnt_half_1sec;

end

end

end

assign add_cnt_half_1sec = 1'b1 ;

assign end_cnt_half_1sec = add_cnt_half_1sec && ( cnt_half_1sec == MAX_CNT_HALF_1SEC - 1'b1 );

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

led <= 0 ;

end else begin

if(end_cnt_half_1sec) begin

led <= ~led ;

end else begin

led <= led ;

end

end

end

endmodule

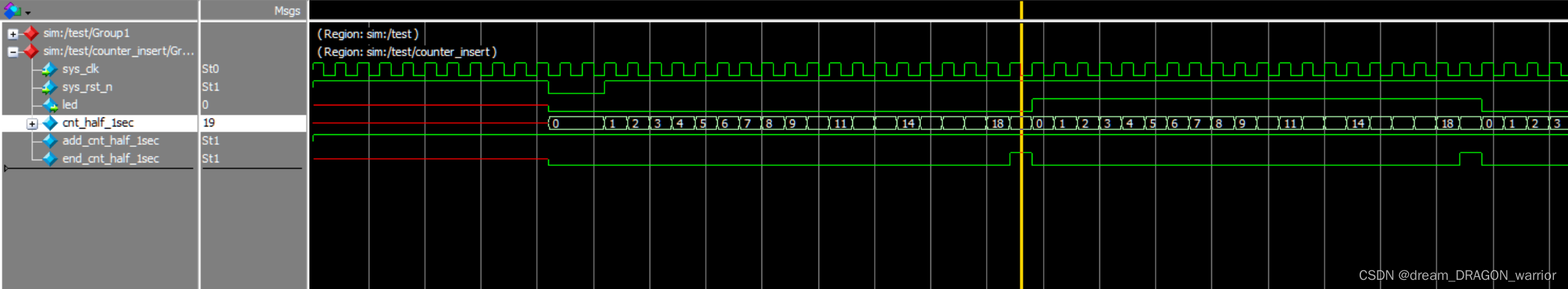

`timescale 1ns/1ns

module test();

reg sys_clk ;

reg sys_rst_n ;

wire led ;

parameter CYCLE = 20 ;

// defparam counter_insert.MAX_CNT_HALF_1SEC = 20 ;

counter

#(

.MAX_CNT_HALF_1SEC (20)

)

counter_insert

(

.sys_clk ( sys_clk ),

.sys_rst_n ( sys_rst_n ),

.led ( led )

);

initial begin

sys_clk <= 1'b1 ;

sys_rst_n <= 1'b1 ;

#( 210 ) ;

sys_rst_n <= 1'b0 ;

#( 50 ) ;

sys_rst_n <= 1'b1 ;

#( 1000 ) ;

$stop ;

end

always #( CYCLE / 2 ) sys_clk <= ~sys_clk ;

endmodule

本文介绍了Verilog代码中的一个模块,包含一个25位的计数器和一个测试模块,用于控制LED灯的切换。计数器在系统时钟上升沿触发,当计数达到最大值时,LED状态反转。

本文介绍了Verilog代码中的一个模块,包含一个25位的计数器和一个测试模块,用于控制LED灯的切换。计数器在系统时钟上升沿触发,当计数达到最大值时,LED状态反转。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?