cadence SPB17.4 - Create Differential Pair(差分)

前言

正在串SPB17.4的细节,发现建立差分对,这里,有点问题。

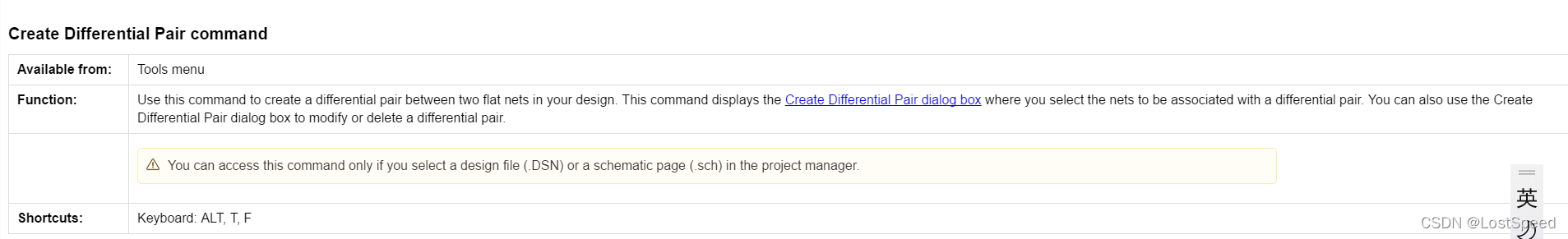

官方帮助说,只要选中.sch或.dsn, 在菜单中就能看到建立差分对的菜单。

是看见了不假,但是灰的,点不动。

官方说明如下:不好使。

帮助文件位置 D:/Cadence/SPB_17.4/doc/cap_ref/Project_manager_command_reference.html

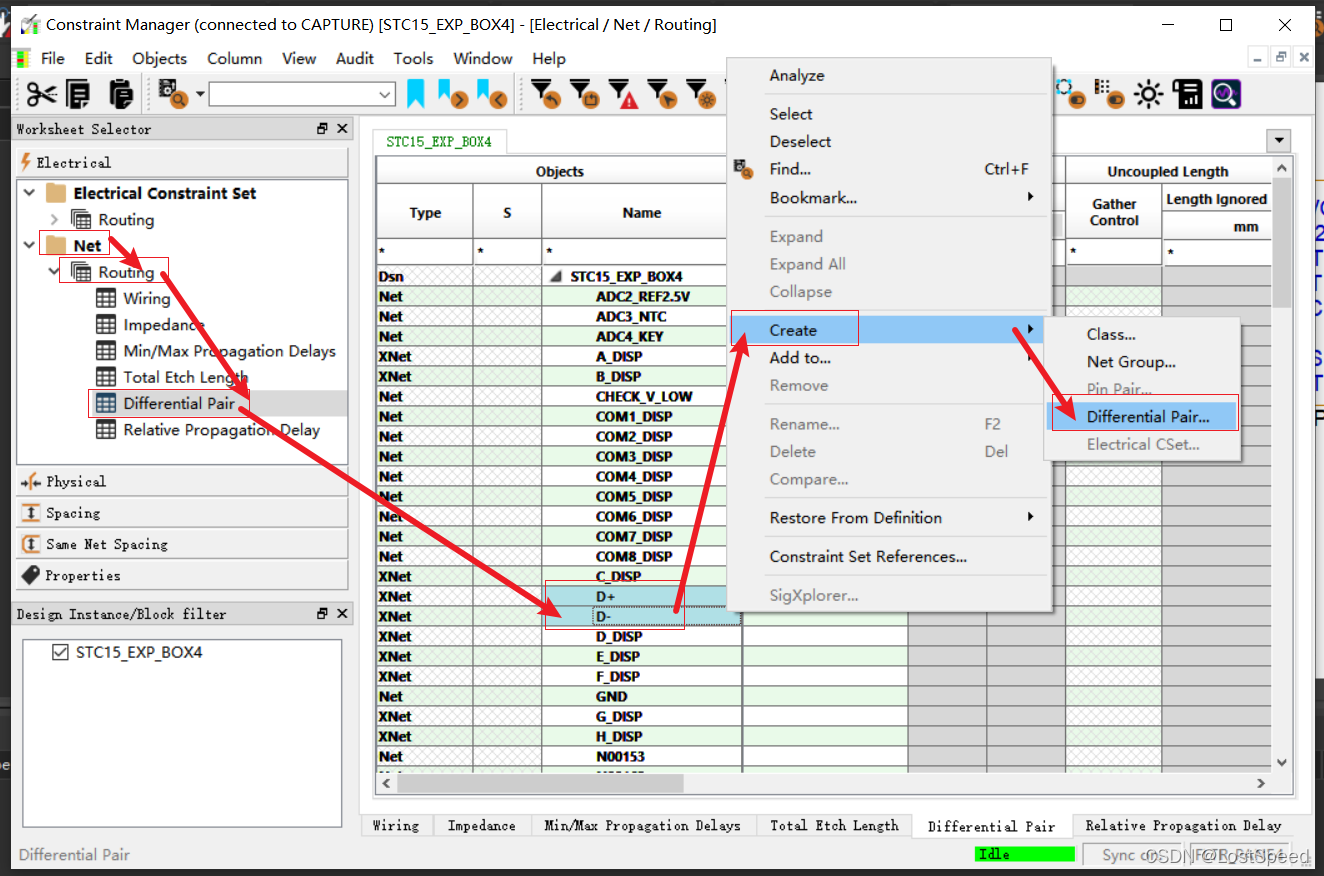

实验

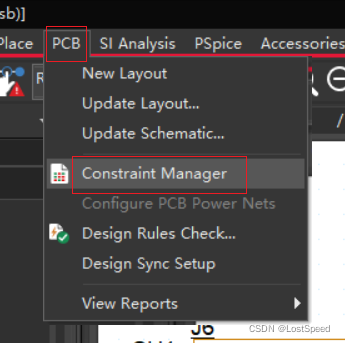

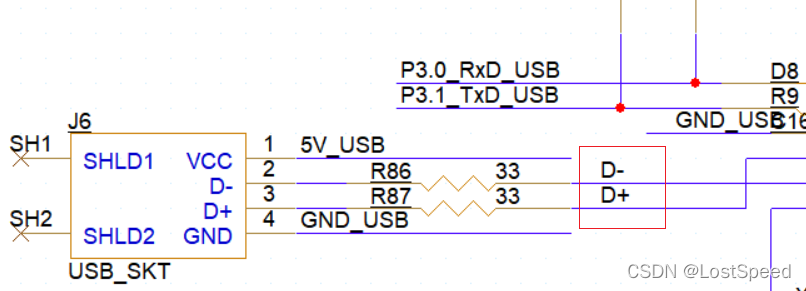

发现在约束管理器中可以设置差分对,但是设置完,在原理图中没有差分指示的显示。

是不是原理图和PCB并没有同步更新引起的?

我这是层次原理图,是不是SPB17.4有bug?

反正是可以设置了,具体布线时,是否有差分布线效果,到时候再验证。先能设置差分线再说。

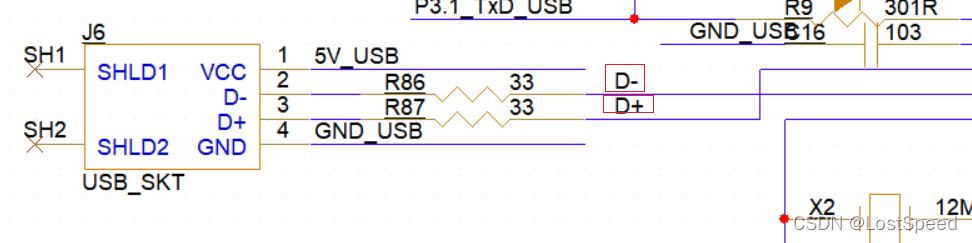

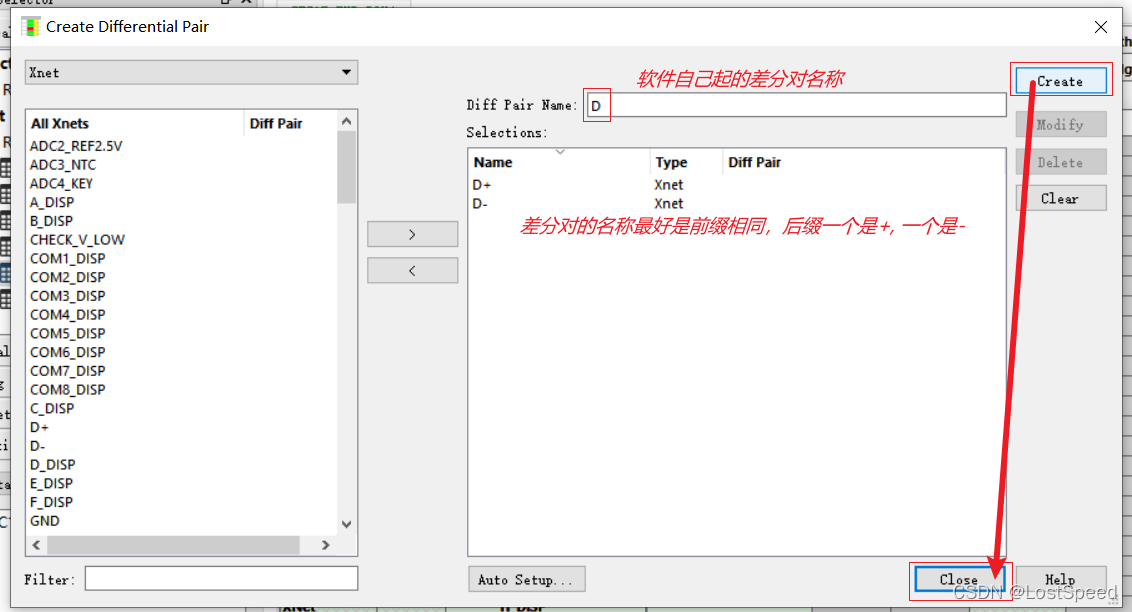

假设 D+, D-要设置为差分。

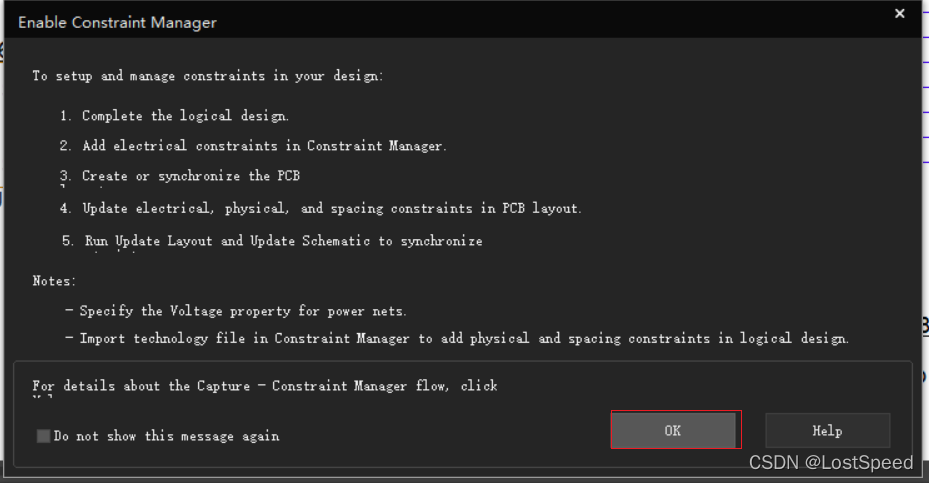

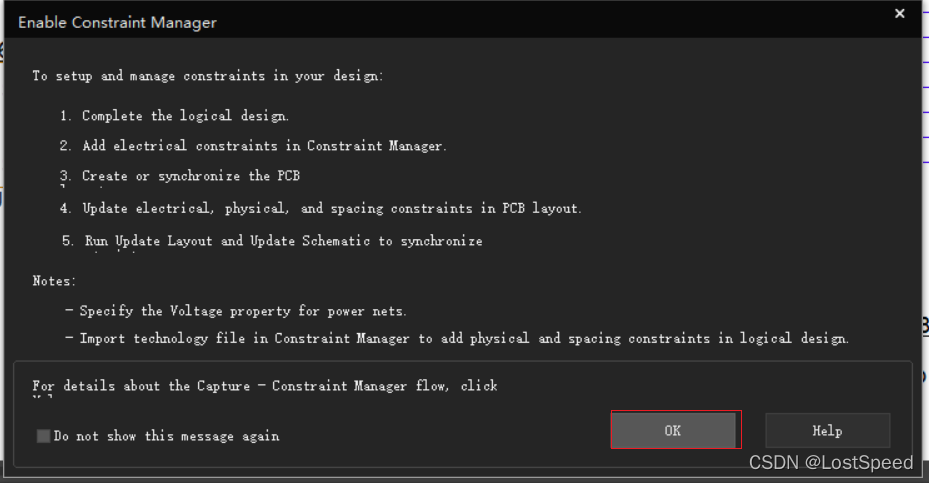

有个对话框提示,是不是要先将PCB加入SCH中才行?

按理说不该啊,就是在原理图中设置一下差分对,和其他图纸还有关系么?

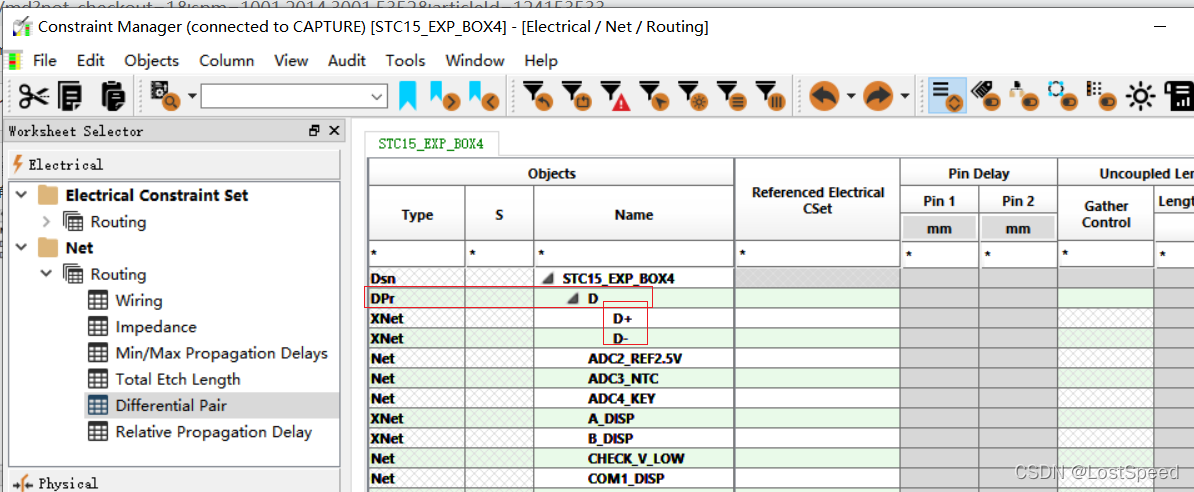

建立完差分对后,约束管理器的样子

关掉约束管理器,回到capture,没发现原理图有差分指示。

看着像做差分对前,弹出的这个对话框中描述的事情没做引起的。

先这样,以后再研究。

留言整理

博主在使用Cadence SPB17.4时遇到建立差分对的菜单灰色不可用的问题。通过约束管理器虽然能够设置差分对,但原理图中并无差分指示。怀疑可能是层次原理图导致的同步问题或软件潜在的bug。后续发现可能需要先将PCB加入SCH中,但不确定是否必要。尽管如此,差分对已经设置成功,将在布线时进一步验证效果。

博主在使用Cadence SPB17.4时遇到建立差分对的菜单灰色不可用的问题。通过约束管理器虽然能够设置差分对,但原理图中并无差分指示。怀疑可能是层次原理图导致的同步问题或软件潜在的bug。后续发现可能需要先将PCB加入SCH中,但不确定是否必要。尽管如此,差分对已经设置成功,将在布线时进一步验证效果。

3561

3561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?