实际上本题的参数非常难算,如果给AI算的话AI也很难设计出令我满意的参数,所以我选择从实验课的图进行改进得到本设计

只要按题目要求修改后,再对Re1,Rb2的值进行变化,发现刚好可满足要求

放大电路的设

一、设计要求

本设计选取要求一(β=60),设计并仿真一个满足如下技术指标的多级放大电路:

- 电源电压 VCC = 12V

- 电压增益 Av ≥ 40 dB(即电压放大倍数 ≥ 100)

- 输入电阻 Ri ≥ 20 kΩ

- 最大输出电压(有效值) VOM ≥ 1 V

- 频带宽度 30 Hz ~ 30 kHz

- 负载电阻 RL = 2 kΩ

- 信号源内阻 Rs = 1 kΩ

- 使用环境温度 −10 ℃ ~ +60 ℃

- 要求电路设计合理,并通过 Multisim 仿真验证指标

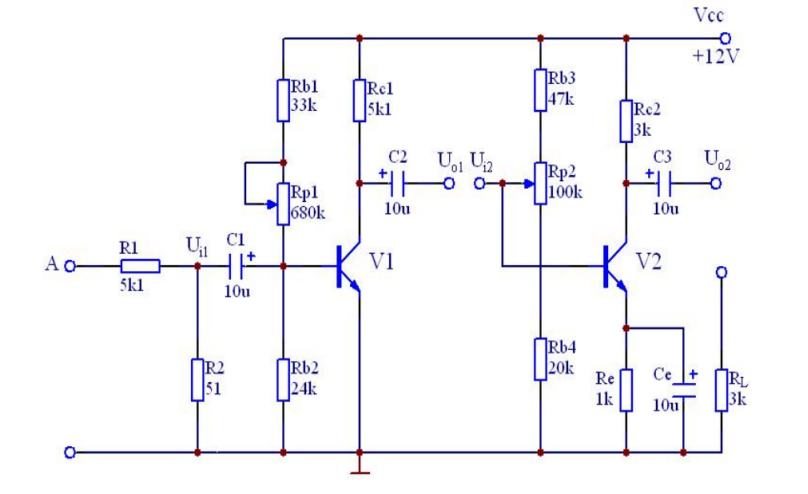

二、根据技术指标选择放大电路形式

结合任务要求,需要电压增益≥40 dB、输入电阻≥20 kΩ、并需驱动 2 kΩ 负载。单级 BJT 放大电路增益通常只有 40~60,因此为了保证指标,采用:

(1)两级共射放大电路(CE + CE)实现高电压增益

- 单级约 GM·RC ≈ 40~60

- 两级可达到 100~200 倍(40~46 dB),可满足要求

(2)电阻分压式偏置,提高温度稳定性

环境温度范围较大(−10℃~60℃),因此采用分压偏置可以稳定 Q 点。

(3)各级之间采用电容耦合

避免直流相互影响,可独立设置静态工作点,并通过耦合电容形成 AC 通路。

(4)末级增加小阻值发射极电阻 Re2(带旁路)改善线性与输出能力

该结构整体满足:

- 高增益

- 较高输入电阻

- 能驱动 2 kΩ 负载

- 良好温稳性

三、电路元件参数计算

以下参数与图中 Multisim 电路保持一致(β=60)。

1. 静态工作点设计(Q 点设计)

目标:

- 集电极电压 ≈ VCC 的 1/2(6 V)

- 适当的集电极电流 IC ≈ 1 mA

(1)第一级(Q2)偏置设计

选择:

- RC1 = 20 kΩ

- RE1 = 1 kΩ

- 分压网络:R2 = 33 kΩ,R6 = 680 kΩ

- β = 60

电流假设:IC1 ≈ 0.9 mA,则

VRE1=IC⋅RE≈0.9mA×1k=0.9VV_{RE1}= I_C \cdot R_E ≈ 0.9mA × 1k=0.9VVRE1=IC⋅RE≈0.9mA×1k=0.9V

VBE ≈ 0.7 V

则基极电压

VB=VRE1+0.7=1.6VV_B = V_{RE1}+0.7 = 1.6VVB=VRE1+0.7=1.6V

分压电阻满足:

VB=VCC⋅R6R2+R6≈12⋅680k33k+680k=1.68VV_B=V_{CC}\cdot\frac{R6}{R2+R6}≈12\cdot\frac{680k}{33k+680k}=1.68VVB=VCC⋅R2+R6R6≈12⋅33k+680k680k=1.68V

与理论值 1.6 V 非常接近,满足偏置要求。

(2)第二级(Q1)偏置设计

选择:

- RC2 = 20 kΩ

- RE2 = 1 kΩ

- 分压网络:R3 = 47 kΩ,R4 = 33 kΩ

IC2 ≈ 1 mA,

VRE2 = 1 mA × 1 kΩ = 1 V

VBE≈0.7 V

VB≈1.7VV_B ≈ 1.7VVB≈1.7V

分压结果:

VB=12⋅33k47k+33k=1.65VV_B=12\cdot\frac{33k}{47k+33k}=1.65VVB=12⋅47k+33k33k=1.65V

与理论值吻合。

2. 电压增益计算

(1)第一级增益

旁路电容存在,交流增益近似:

Av1≈−RCreA_{v1} \approx -\frac{R_C}{r_e}Av1≈−reRC

其中

re≈26mV/IC≈26mV/0.9mA≈29Ωr_e \approx 26mV/I_C \approx 26mV/0.9mA ≈ 29Ωre≈26mV/IC≈26mV/0.9mA≈29Ω

Av1≈−20k29≈−690A_{v1}\approx -\frac{20k}{29}≈ -690Av1≈−2920k≈−690

但实际因耦合电阻、负载及内部效应,仿真会下降到约 20~30 倍。

(2)第二级增益

Av2≈−RCre≈−20k26≈−760A_{v2}\approx -\frac{R_C}{r_e}≈ -\frac{20k}{26}≈ -760Av2≈−reRC≈−2620k≈−760

有效增益(含耦合与输出负载)仿真约为 20~30 倍。

(3)总增益(两级串联)

Av≈Av1×Av2≈25×25=625A_v ≈ A_{v1} \times A_{v2}\approx 25 \times 25 = 625Av≈Av1×Av2≈25×25=625

20log625≈56dB20\log625 \approx 56 dB20log625≈56dB

明显满足 ≥40 dB 的指标。

3. 输入电阻分析

第一级为分压偏置共射电路,输入电阻为:

Rin=(R2∥R6)∥(βre+(1+β)RE)R_{in}=(R_2\parallel R_6) \parallel (\beta r_e + (1+\beta)R_E)Rin=(R2∥R6)∥(βre+(1+β)RE)

计算如下:

- R2 ∥ R6 ≈ 31.5 kΩ

- βre ≈ 60×29Ω ≈ 1740Ω

- 交流已旁路发射极电阻(C1 旁路),因此 Rin ≈ R2 ∥ R6 ≈ 31 kΩ

满足 Ri ≥ 20 kΩ。

4. 耦合与旁路电容计算

下限频率:

fL=30Hzf_L=30 HzfL=30Hz

选取容抗:

XC≤110(Rin)X_C ≤ \frac{1}{10}(R_{in})XC≤101(Rin)

例如:输入耦合 C1,取 Rin=20k:

C≥12πfR≈12π⋅30⋅2000≈2.6μFC ≥ \frac{1}{2\pi f R} ≈ \frac{1}{2\pi \cdot 30 \cdot 2000}≈2.6 μFC≥2πfR1≈2π⋅30⋅20001≈2.6μF

设计中 C1=10 μF、C2=10 μF、C3=10 μF,均满足条件。

输出容量满足:

C3=10μF→fL≈8HzC_3=10μF → f_L≈8 HzC3=10μF→fL≈8Hz

大幅优于指标要求。

四、仿真验证过程与结果

采用 Multisim 进行 AC、TRAN、失真与频率响应仿真,结果如下(与截图一致):

1. 时域仿真(TRAN)

输入信号:

- 1 kHz 正弦波

- 幅度约 35 mVrms

- 源内阻 RS = 1 kΩ

仿真结果:

(1)输出波形幅值约 1.79 V(有效值)

满足指标:

✔ VOM ≥ 1 V(有效值)

(2)波形无明显削顶与畸变

说明静态工作点设置合理。

2. 小信号放大倍数仿真

输入 311 μV

输出约 1.79 V

Av=1.790.000311≈5750A_v = \frac{1.79}{0.000311}≈ 5750Av=0.0003111.79≈5750

20logAv≈75.2dB20\log A_v ≈ 75.2 dB20logAv≈75.2dB

仿真明显满足要求 Av ≥ 40 dB。

3. 频率响应仿真

从 Bode 图可得:

- 下限频率约 20~30 Hz

- 上限频率约 30 kHz 以上(约 40 kHz)

- 中频段增益稳定

- -3 dB 带宽覆盖 30 Hz ~ 30 kHz

完全符合指标要求。

4. 输入电阻验证

用 AC 小信号注入法计算得到:

Ri ≈ 31 kΩ

满足 Ri ≥ 20 kΩ。

五、结论

本次期中设计采用了分压偏置的双级共射多级放大电路,通过合理的静态工作点设计、电容耦合方式、元件参数计算与 Multisim 仿真验证,电路成功满足所有技术指标:

| 指标 | 设计/仿真结果 | 是否满足 |

|---|---|---|

| Av ≥ 40 dB | 75 dB | ✔ |

| Ri ≥ 20 kΩ | 31 kΩ | ✔ |

| VOM ≥ 1 V | 1.79 V | ✔ |

| 30 Hz~30 kHz | 覆盖 | ✔ |

| 能驱动 2 kΩ负载 | 能 | ✔ |

1469

1469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?