Xilinx DP1.4 概述

Xilinx的DisplayPort 1.4(DP1.4)技术是一种高性能视频接口标准,支持高分辨率、高刷新率显示以及多流传输。它通常用于FPGA和SoC设计中,适用于需要高带宽视频传输的应用场景。可参考Xilinx官方文档PG230、PG299、PG300。

主要特性

- 高带宽支持:DP1.4支持高达32.4 Gbps的带宽(HBR3模式)。

- 显示流压缩(DSC):支持VESA DSC 1.2压缩技术,实现无损或视觉无损压缩,提升传输效率。

- 多流传输(MST):允许通过单个DP接口驱动多个显示器。

- 前向纠错(FEC):与DSC结合使用,确保数据传输的可靠性。

支持的Xilinx器件

Xilinx的以下系列支持DP1.4功能:

- UltraScale+ FPGA:如Virtex UltraScale+和Kintex UltraScale+系列。

- Zynq UltraScale+ MPSoC:集成硬核DP1.4控制器,支持视频处理与显示输出。

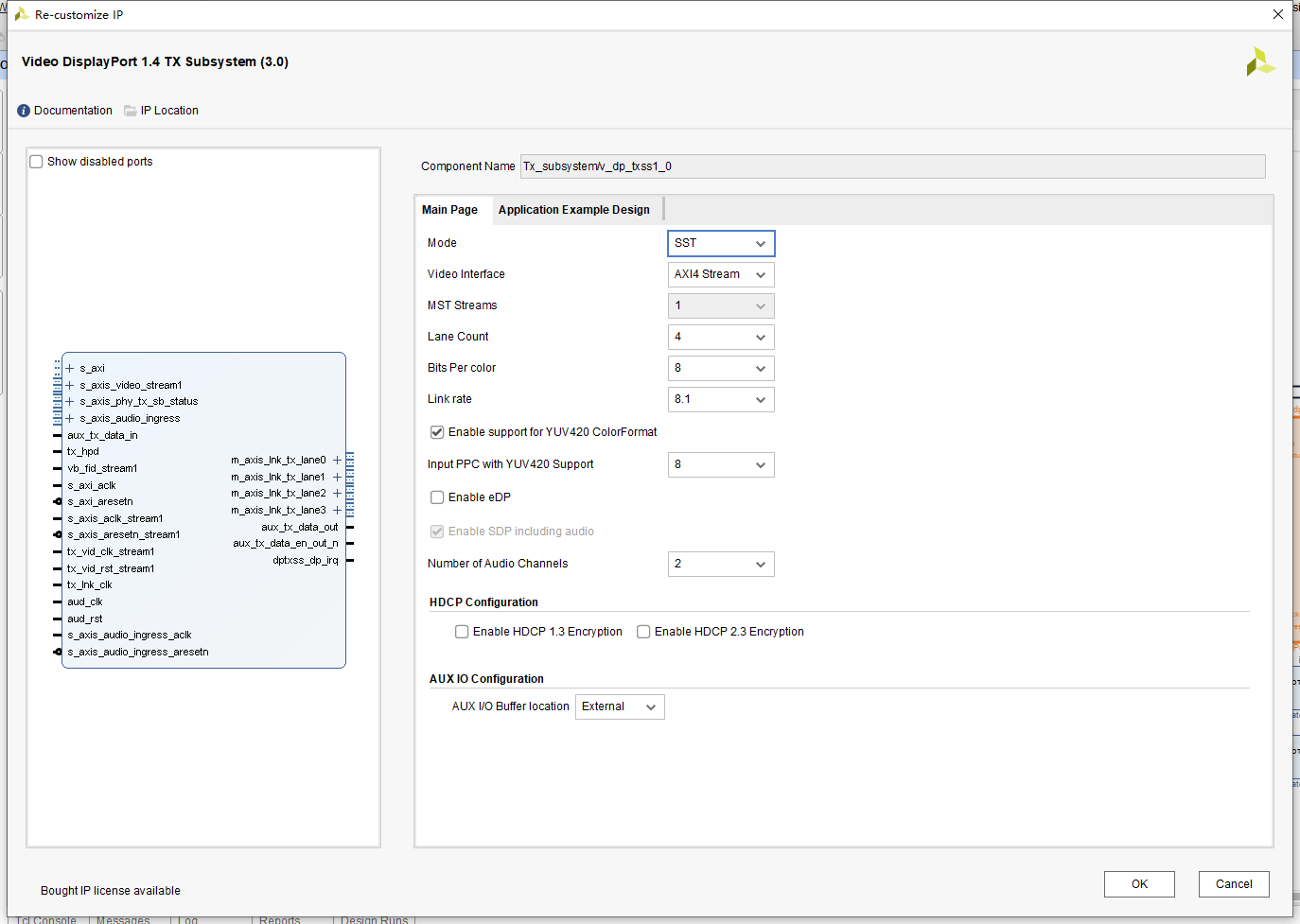

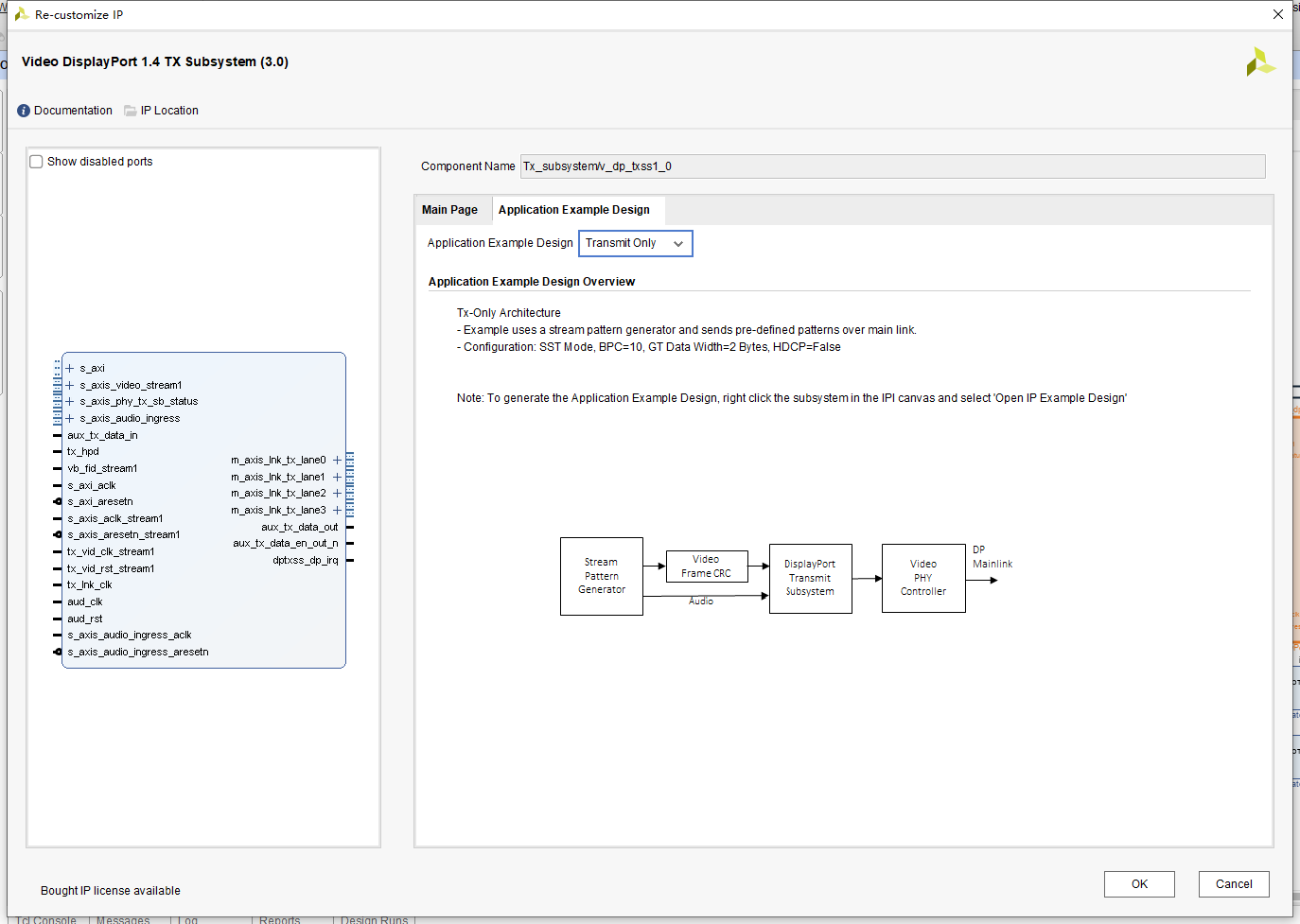

1.DP1.4 TX IP配置如下:

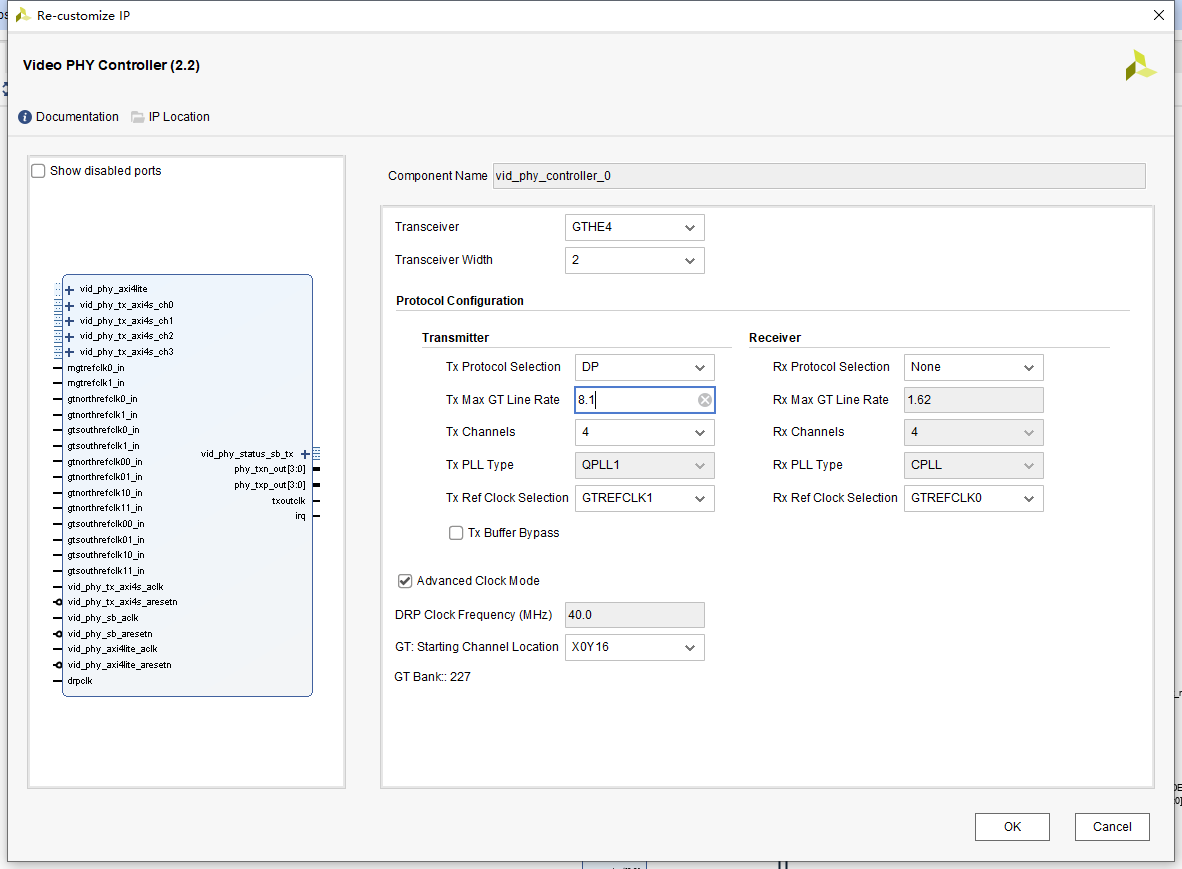

2.Video PHY Controller IP配置如下:

总结:工程只支持DP1.4 TX,经过测试DP1.4 的输出分辨率最高支持8K30Hz(8K60hz没有配置成功),支持嵌入自定义的音频,也可以加入自定义的1D LUT、3D LUT。

2859

2859