V-By-One RX 是一种高速串行接口技术,主要用于传输视频信号,常见于工业显示器、医疗设备和车载显示屏等场景。其特点是采用差分信号传输,支持高带宽、低电磁干扰(EMI),且无需外部时钟信号,通过嵌入式时钟恢复机制实现同步。

采用FPGA高速Serdes直接解析VBO RX,做到8K向下兼容,本文选用Xilinx UltraScale+系列FPGA。

目前市面上V-By-One接口由于LCD玻璃的庞大需求,VBO TX得到了广泛应用,直接能够驱动8K玻璃面板的芯片方案已经很成熟。但是VBO RX能够做到8K向下兼容,lane数和数据排列自定义的芯片就少见。基于现状充分利用FPGA Serdes优势,很少的走线就可以做到VBO RX 8K向下兼容。

一、技术特点

- 差分传输:使用一对差分线传输数据,抗干扰能力强。

- 嵌入式时钟:数据流中嵌入时钟信息,无需单独时钟线。

- 高带宽:单通道速率可达 3.75 Gbps,多通道并联可支持更高分辨率(如 4K/8K)。

- 低功耗:相比传统接口(如 LVDS),功耗更低。

-

3D frame identification

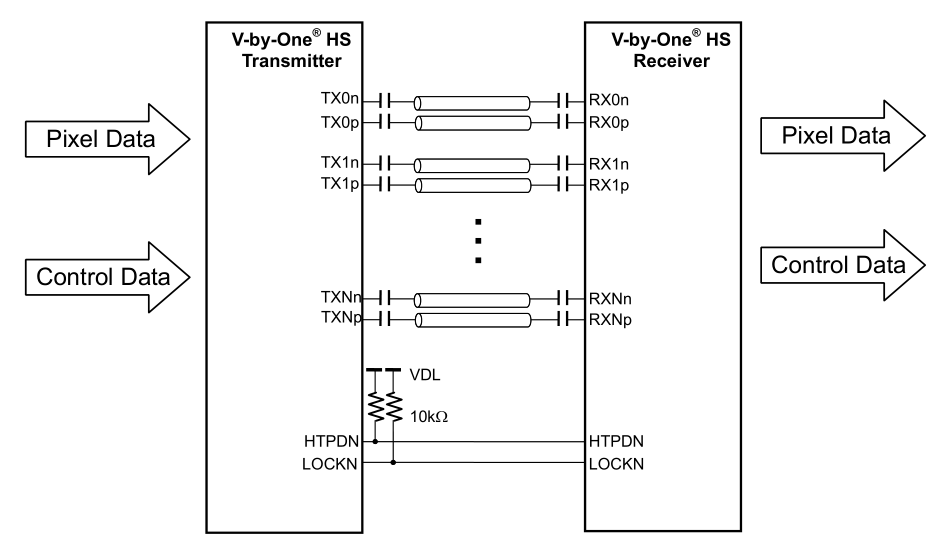

二、VBO 系统框图

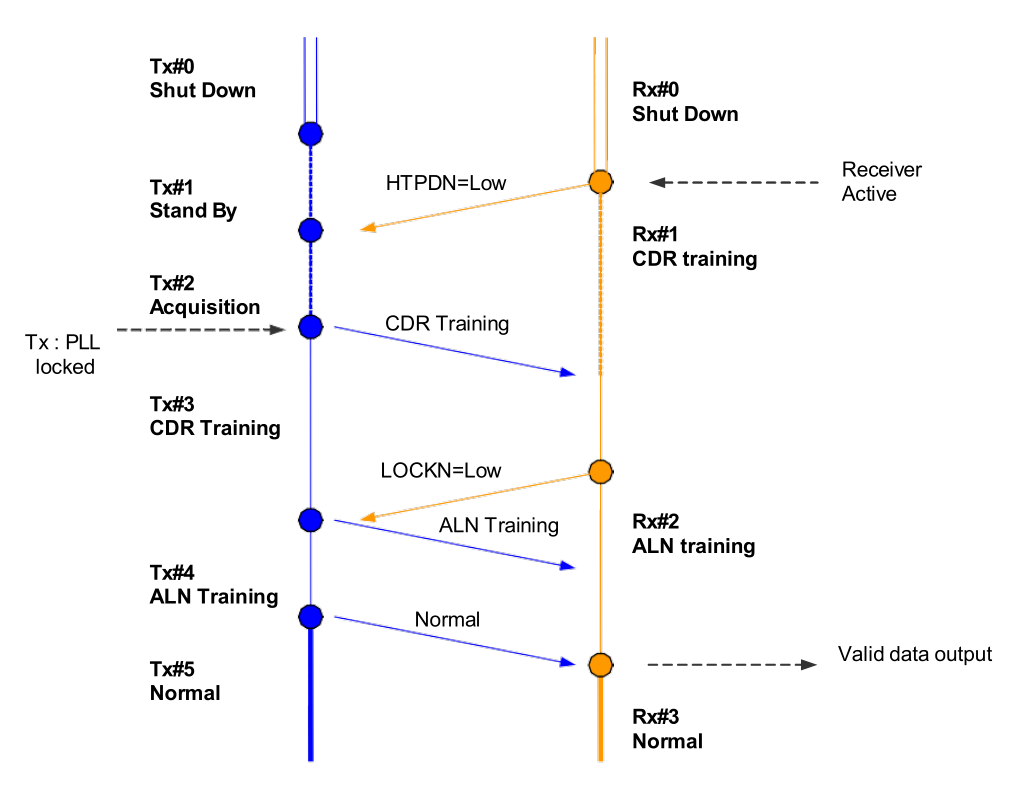

二、启动流程

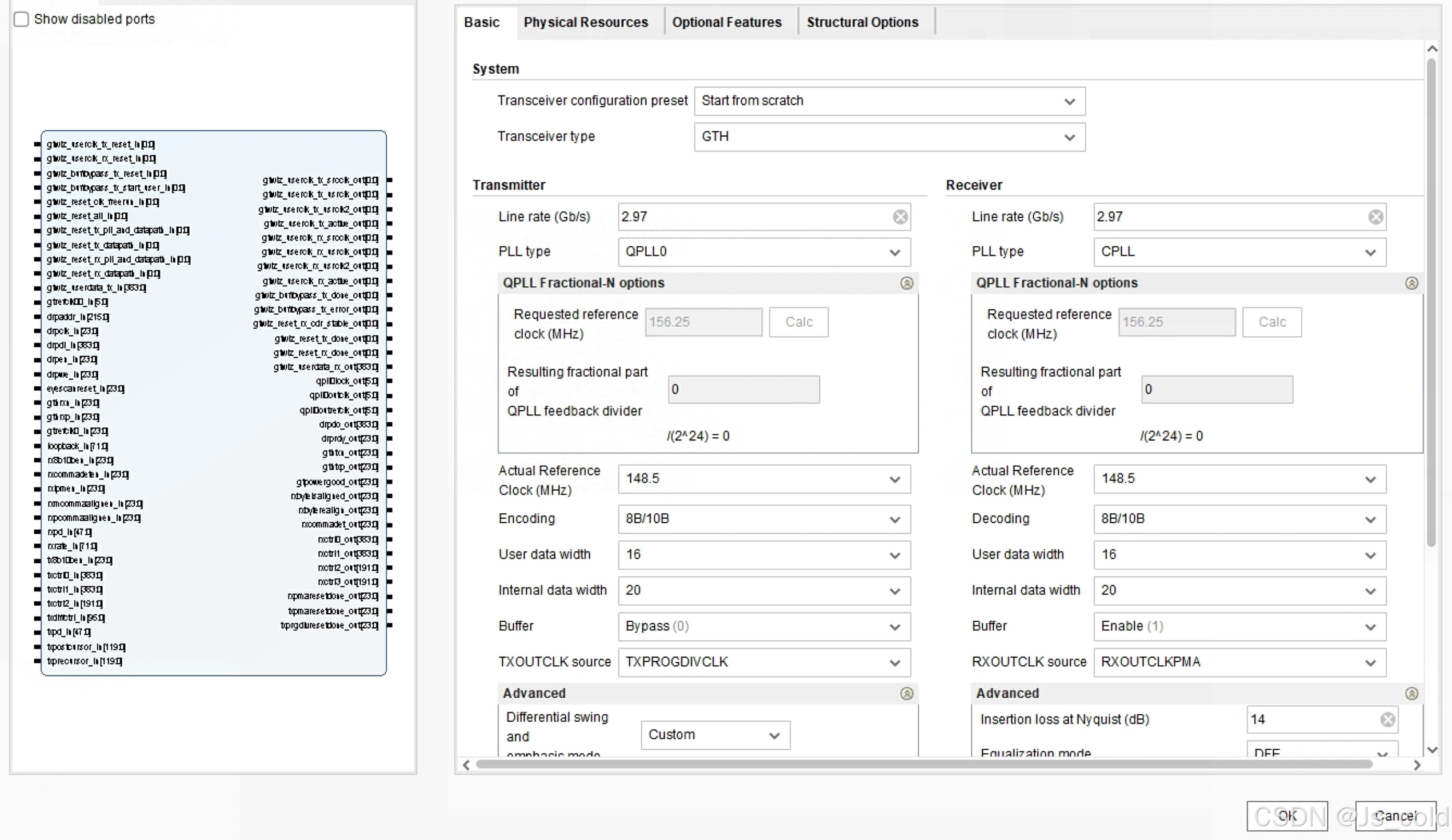

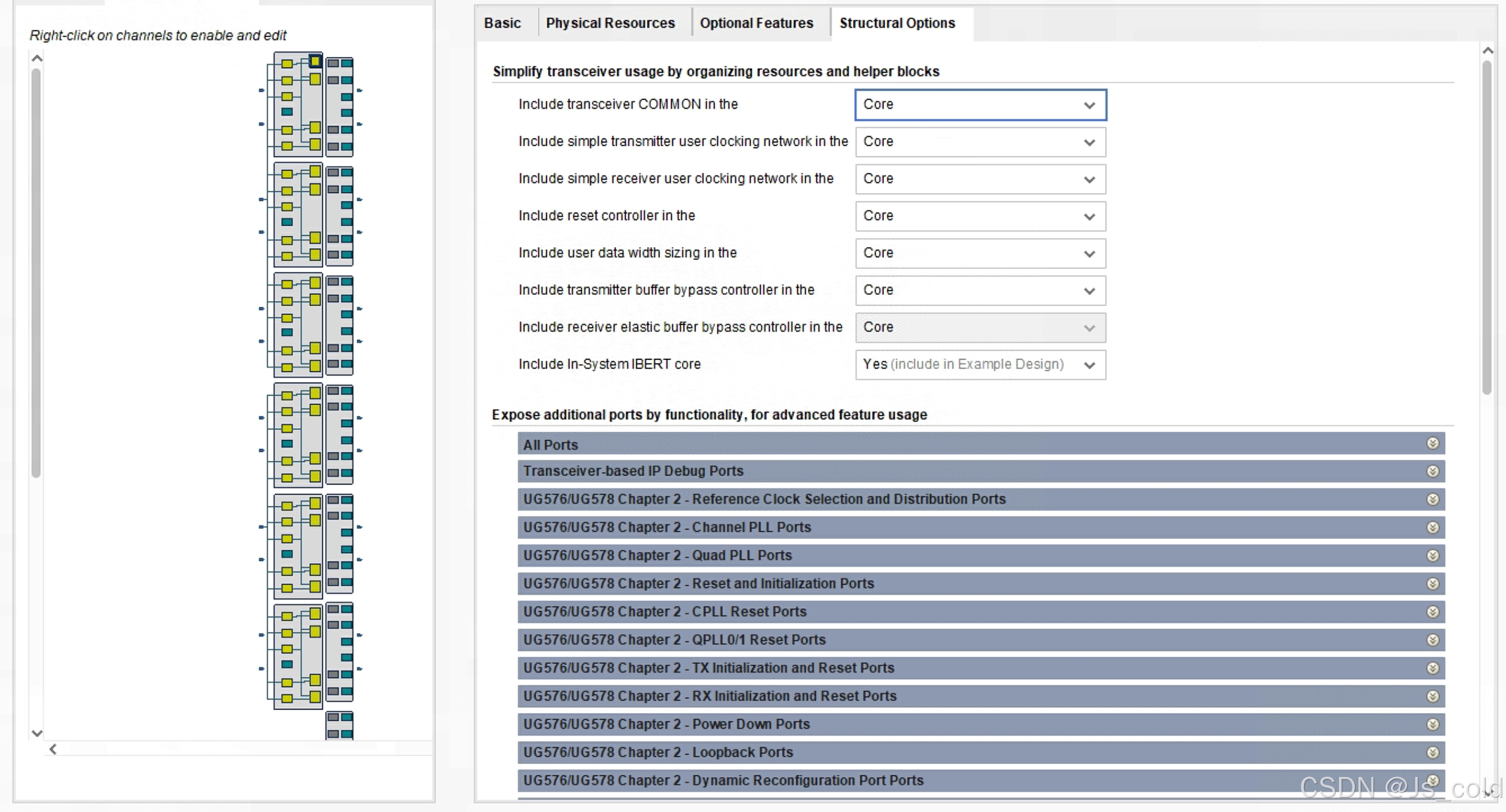

三、Serdes配置

四、PCB Layout

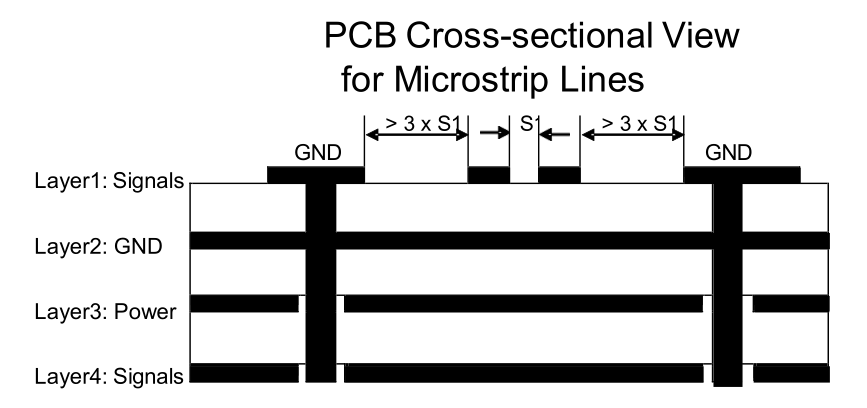

1. 使用至少四层的PCB,每层分配信号、地线、电源和信号。(参见下图)

2. 高速信号的PCB线路必须是差分特性阻抗为100Q的单端微带线或耦合微带线。

3. 尽量减少差分对(下图中的S1)之间的迹线距离,以最大化共模抑制和耦合效应,这有助于减少电磁干扰(EMD) 。

4. 对称布线差分信号迹线。

5. 避免直角转弯,或尽量减少高速迹线上的过孔数量,因为它们通常会导致传输线路中的阻抗不连续,并降低信号完整性。PCB迹线、连接器或电缆之间的阻抗不匹配也会导致反射,从而限制高速通道的带宽。

五、结论

根据FPGA高速Serdes直接解析VBO RX,灵活配置高速口数量,支持逐点/左右分屏/四分屏/八分屏等数据排列,已成功实现8K120Hz/60Hz、4K120Hz/60Hz等分辨率解析,纯逻辑代码编写,不受FPGA平台限制,移植便捷,可以嵌入自定义命令、状态、数据等等。

六、合作交流

欢迎私信交流指正。

3095

3095