分析复位开关和三极管点亮Led灯

文章目录

前言

我本是一个Android应用开发工程师,在自学驱动过程中曾无数次为原理图抓狂,奈何自己确实没有任何模电、数电、硬件、大学物理相关基础。 软件工程专业出生,所以总是挠头,看到原理图 自身原因很懵逼,及时硬件同事给我讲了一次,可能下一次还是懵逼。

硬着头皮看看吧,然后根据自身情况总结知识点,一步一个脚印吧!

参考资料

NPN与PNP的区别

NPN三极管与PNP三极管的电路板应用选择

详解三极管NPN与PNP区别

NPN和PNP 的电流方向 、大小关系 、电压偏置

三极管之——PNP与NPN

新手必看!三极管在电路中的应用分析

三极管的应用:开关电路

一、复位开关原理图分析

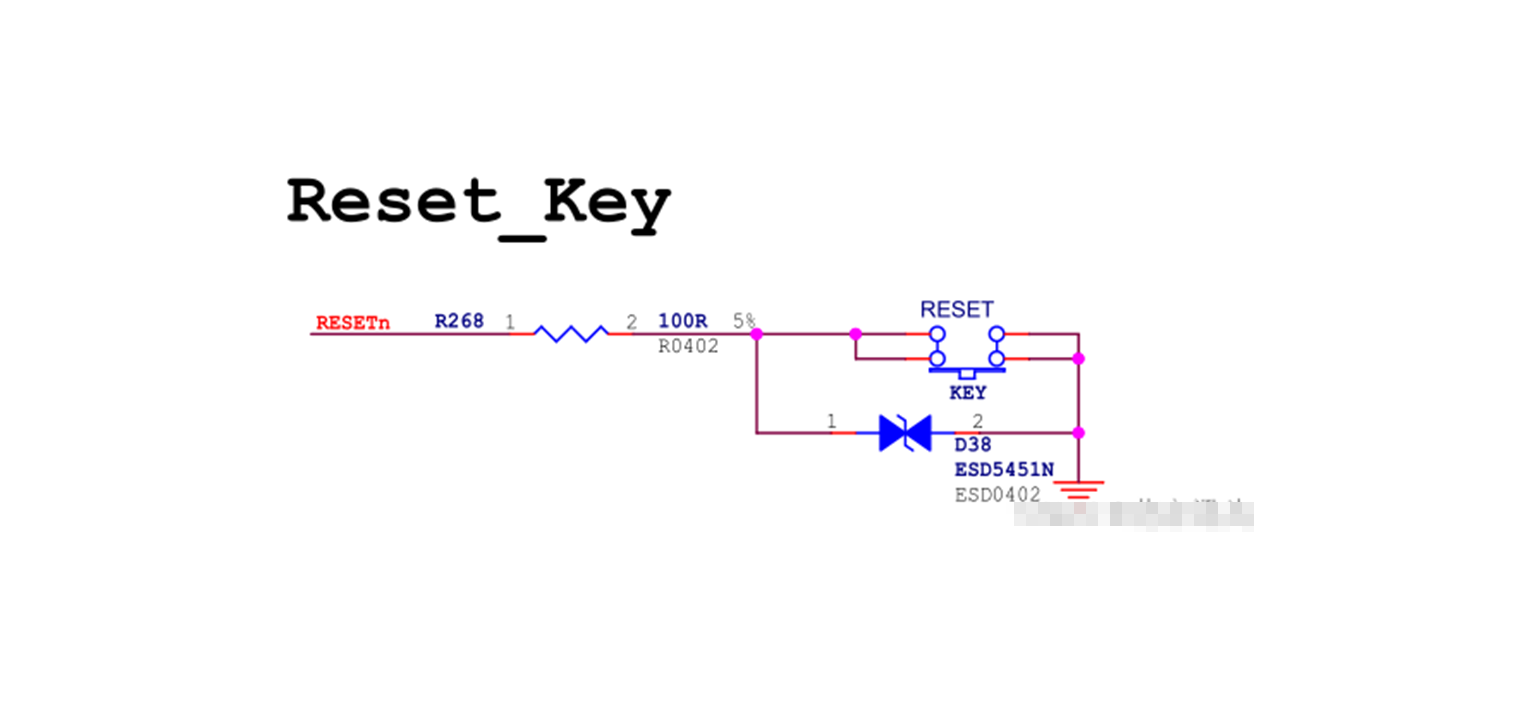

比如说,如下这个简单的原理图,同个这个原理图,我们能获取哪些知识点?

该原理图展示了一种手动复位+防静电保护的复位电路,核心是通过电阻、开关、二极管协同实现复位信号的稳定控制。以下是各元件与工作逻辑的详细拆解:

元件功能与连接逻辑

-

R268(100R上拉电阻):连接在RESETn(复位引脚)与电源(假设为+3.3V)之间,作用是上拉复位引脚至高电平,让电路在正常工作时保持“非复位”状态。

-

R0402(51Ω电阻):串联在RESETn与RESET节点之间,用于限流与信号匹配,避免复位引脚直接短路或信号冲突。

-

KEY(手动复位开关):通过开关的通断控制RESET节点的电平。当开关断开时,RESET节点由R268上拉至高电平;当开关闭合时,RESET节点被拉低至地(GND)。

-

D38(ESD5451N静电保护二极管):连接在RESET节点与地之间,作用是抑制静电干扰,防止外界静电击穿复位引脚,保障电路可靠性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

689

689

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?