一、实验目的

- 掌握R-S触发器、D触发器和JK触发器的工作原理及其相互转换。

- 学会用74LS00芯片构成钟控RS触发器。

- 学会用74LS112实现D触发器

- 学会在Quartus II上用D触发器实现JK触发器。

二、实验原理

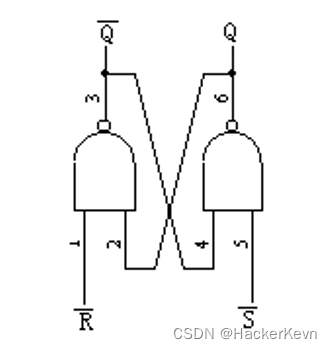

- 基本R-S触发器是直接复位-置位的触发器,它是构成各种功能的触发器的基本组成部分。基本R-S触发器可由交叉耦合的两个“与非”门组成,如图所示:

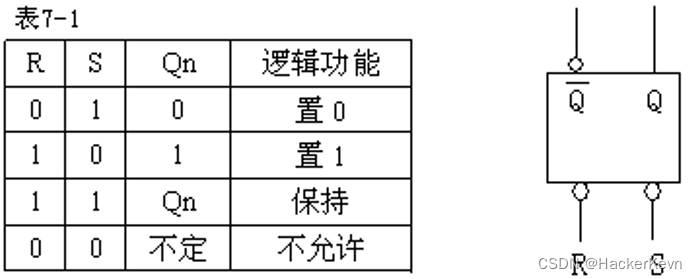

其逻辑符号和真值表如下图所示:

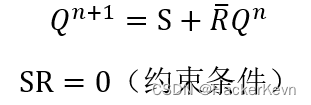

其特性方程如下所示:

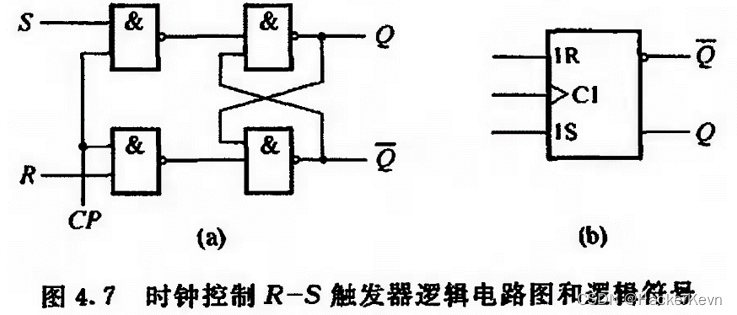

- 钟控R-S触发器由4个“与非”门组成,其中两个“与非”门构成基本R-S触发器,另外两个“与非”门构成控制电路。在时钟信号没有到来时,不管R、S端输入为何值,触发器的状态保持不变。当时钟信号到来时,R和S的输入就可能使触发器置0或置1。其逻辑电路图和逻辑符号如下图所示:

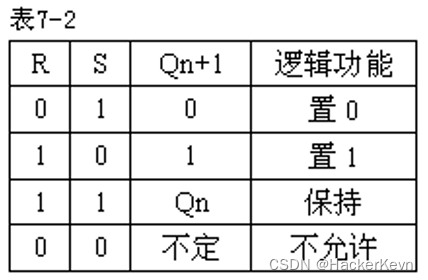

其真值表如下图所示:

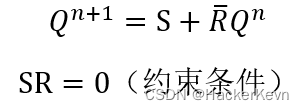

其特性方程如下所示:

- 由于钟控R-S触发器在时钟信号作用期间,当R、S的输入同时为1时,触发器会出现状态不确定现象,故为使R、S端始终处于互补引入只有单输入端的D触发器。其逻辑功能为:当时钟信号到来时,如果输入D=0,则触发器输出Q=0,即触发器置0;如果输入D=1,则触发器置1,即触发器输出Q=1。而当时钟信号没有到来时,无论D输入何值,触发器保持原来状态不变。其逻辑电路图和逻辑符号如下图所示:

本文详细介绍了R-S、D和JK触发器的工作原理,以及如何用74LS00和74LS112芯片进行实验实现。通过QuartusII软件设计JK触发器,并探讨了触发器间的逻辑转换。实验有助于理解和应用这些基本触发器技术。

本文详细介绍了R-S、D和JK触发器的工作原理,以及如何用74LS00和74LS112芯片进行实验实现。通过QuartusII软件设计JK触发器,并探讨了触发器间的逻辑转换。实验有助于理解和应用这些基本触发器技术。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6万+

6万+