在 FPGA 开发圈,有这样一句话:

“代码能跑不代表能用,能用不代表能过 timing。”

而如何从“能实现”到“能优化”,正是 FPGA 工程师成长的关键分水岭。

如果你正在努力迈过这道坎,那么这本书—— 《AMD FPGA设计优化宝典:面向Vivado/VHDL》

几乎是你必须拥有的一本参考书。

一本由工程师写给工程师的“实战宝典”

作者高亚军,是业内熟悉的名字—— Xilinx(现为 AMD)资深战略应用工程师,长期专注于时序收敛、代码优化与Vivado工具分析。 这本书凝聚了他多年在实际项目中的经验总结, 几乎可以说是 “AMD FPGA架构 + Vivado优化实战” 的系统教程。

书中不仅讲“怎么写”,更讲“为什么要这么写”:

从底层架构出发,解释每一种资源(LUT、FF、DSP、BRAM)的硬件特点

对应给出VHDL编写风格与优化建议

并结合 Vivado 工具分析,深入讲解“时钟规划”“布线拥塞”“扇出优化”等工程难题

这是一本能让你真正理解 Vivado 背后逻辑的书。

内容亮点速览

本书基于 AMD Xilinx FPGA 最新架构(7系列、UltraScale/UltraScale+、Versal ACAP), 涵盖 RTL 编写风格、时序优化、布线拥塞分析等关键主题。

共 10 章,系统全面、逻辑清晰:

📑 目录

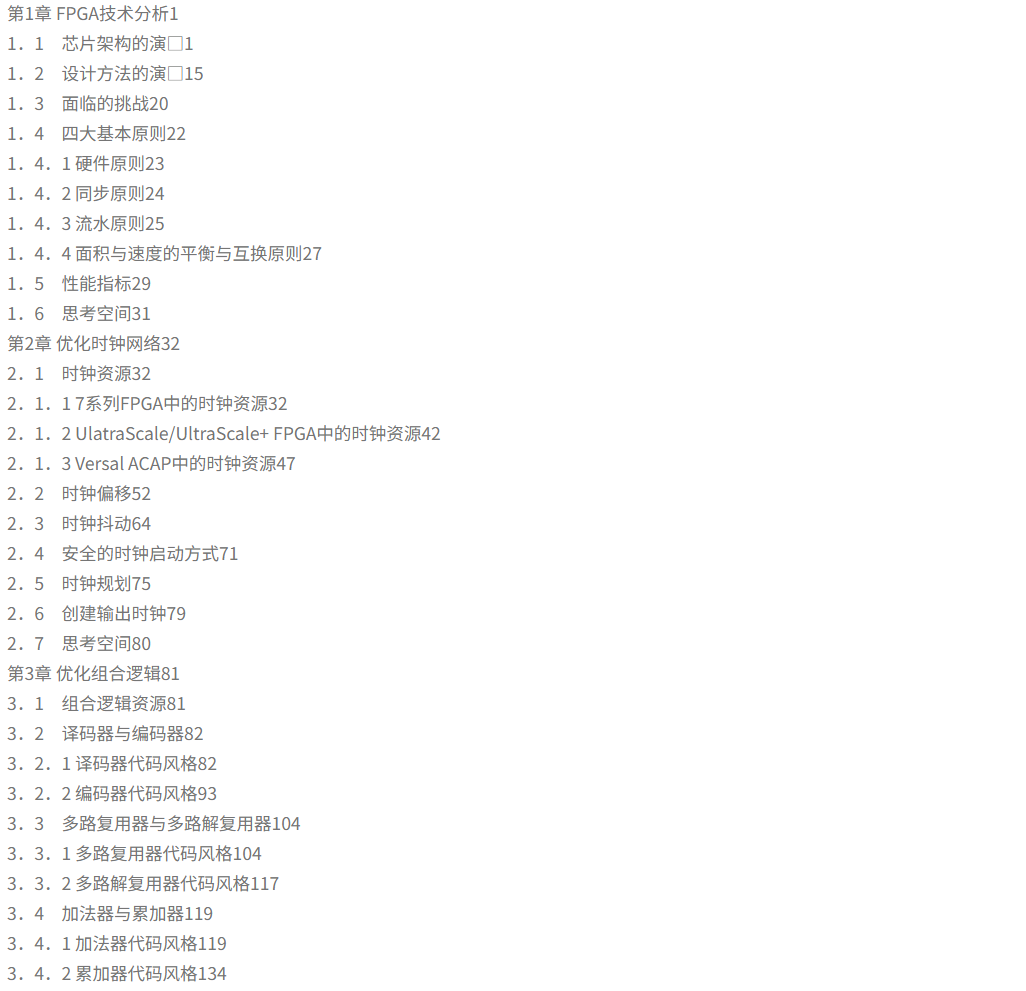

第1章 FPGA技术分析

芯片架构的演变、设计方法与四大原则(同步、流水、平衡等)

第2章 优化时钟网络

时钟资源、偏移与抖动分析、时钟规划与安全启动方法

第3章 优化组合逻辑

译码器/编码器、加法器、移位器、奇偶校验等逻辑风格

第4章 优化触发器

同步/异步复位策略、建立时间、亚稳态与控制集管理

第5章 优化移位寄存器

移位寄存器结构与时序路径管理

第6章 优化存储器

分布式RAM、BRAM、UltraRAM、FIFO、XPM存储结构

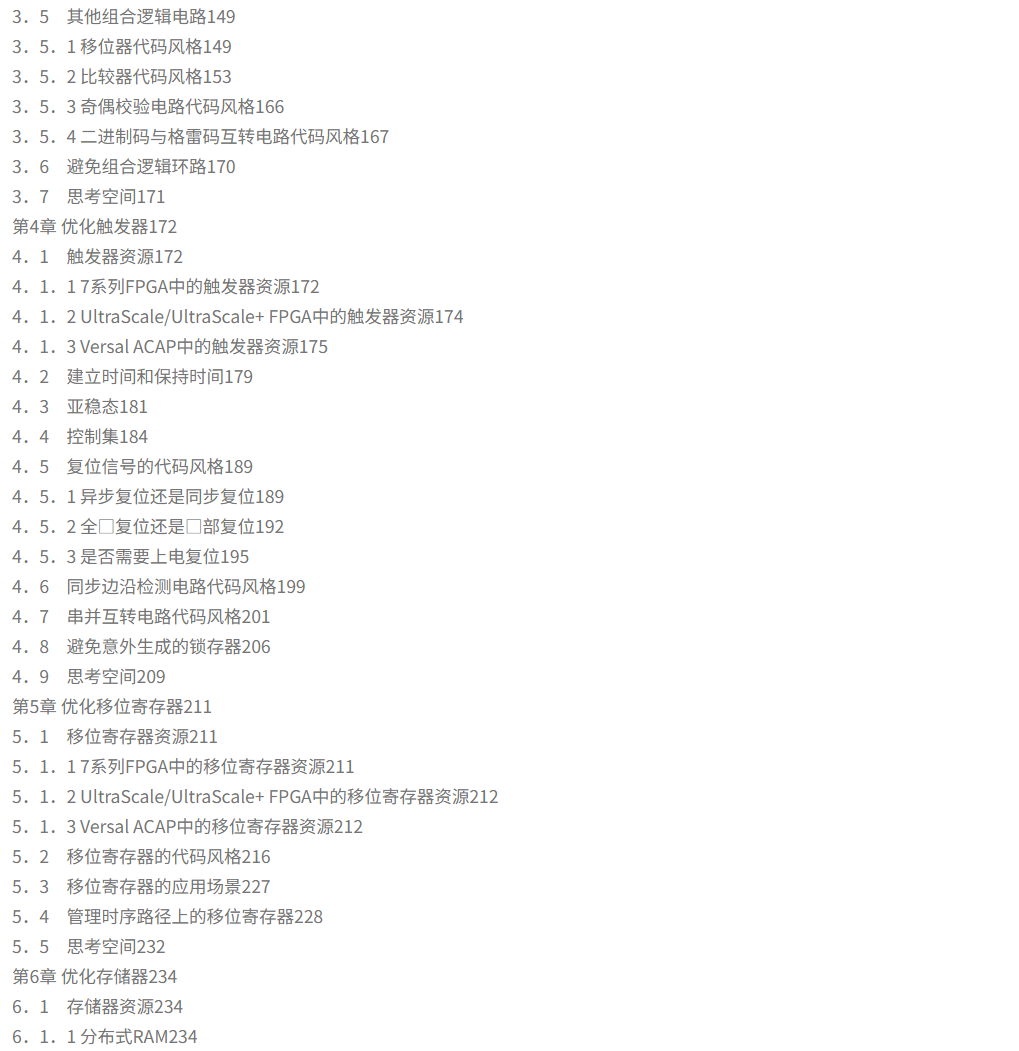

第7章 优化乘加运算单元

DSP资源使用、复数乘法与内积优化

第8章 优化状态机

编码方式、控制器实现与ROM状态机结构

第9章 优化扇出

约束、流程与代码层面降低扇出的方法

第10章 优化布线拥塞

识别拥塞类型、利用设计与约束改善布线瓶颈

▍不仅仅是一本书,而是一套“思维方式”

📘 这不是一本“工具教程”, 而是教你如何让 FPGA 设计更优雅、更工程化的“方法论”。

你会在书中看到这样的建议:

什么时候该 pipeline?

为什么全局复位反而会拖慢时序?

怎样写出 Vivado 真正喜欢的 RTL?

这类问题,往往只有在一线项目踩坑多年后才能体会到—— 而作者把这些经验浓缩成一本 400 多页的“优化手册”, 让你少走很多弯路。

▍适合读者

想进阶为高级 FPGA 工程师的开发者

使用 Vivado/VHDL 进行架构优化的研究生

关注时序收敛与性能优化的项目负责人

▍推荐语

“这本书的价值,不在于让你写出能跑的代码, 而是让你写出能过 timing、能被复用、能被量产的代码。”

对所有从事 FPGA 开发、系统优化或数字信号处理的工程师来说, 这不仅是一本技术书,更是一份工程哲学指南。

图书链接

通过网盘分享的文件:AMD FPGA设计优化宝典_面向VivadoVHDL_高亚军.pdf 链接: https://pan.baidu.com/s/1IZ7c-LheglD8S7HWlKC3ug?pwd=open 提取码: open

PS:如果本书对您有帮助,请购买正版书籍。另,本文分享资源只为了学习沟通,切勿商用,商用引起的任何纠纷与本公众号无关~

7038

7038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?