关注、星标公众号,精彩内容每日送达

来源:网络素材作者:Chris Sousa, 莱迪思半导体区域销售经理

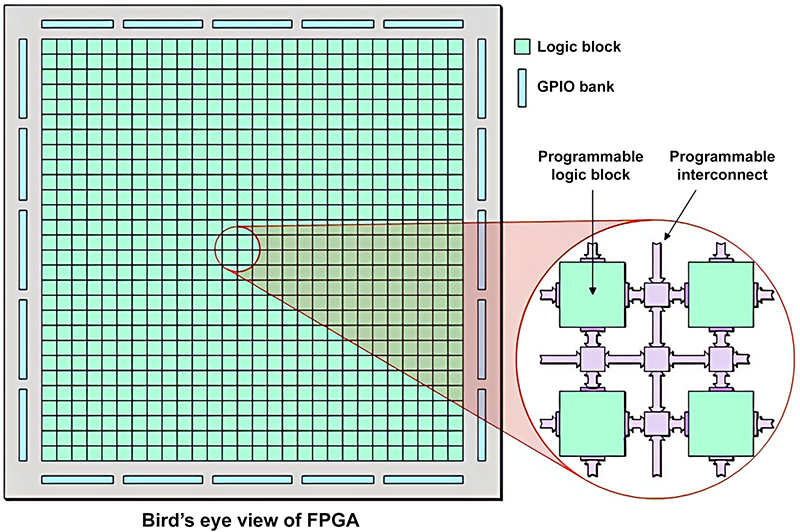

在专用半导体中,现场可编程门阵列(FPGA)因其灵活性和高效性,正在成为推动计算创新的重要力量。

FPGA 能够实现低延迟、低功耗和高性能的设备,这正是人工智能(AI)、机器学习(ML)、高效数据中心以及新一代网络基础设施所需的核心能力。

凭借这些优势,FPGA 为工程师和开发者带来了更多可能性。但需要强调的是,FPGA 并不是解决所有问题的“万能钥匙”。要想真正发挥 FPGA 的潜力,开发者必须理解它的独特优势,并学会如何在设计和实现过程中平衡各类限制条件。

FPGA 设计与开发的关键考量

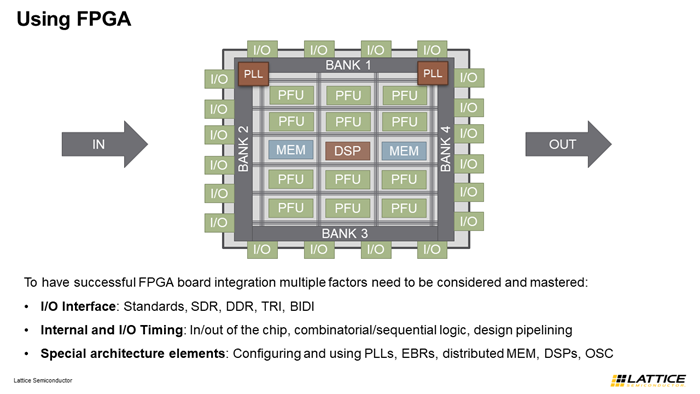

FPGA 并非即插即用,其价值的释放依赖于对性能决定因素的深入理解,主要体现在以下几个方面:

1. 空间与功耗限制

从智能手机到车载边缘传感器,如今的设备越来越小,功耗预算也愈发紧张。这对芯片设计提出了更高要求——开发者需要在设计初期就考虑到空间与能耗的限制,并持续跟踪设计变更对整体系统的影响。

若忽视这些因素,可能导致布线拥堵、能量浪费,甚至在后期被迫进行高成本的返工。只有从一开始就做好资源分配与监控,才能保证最终产品在系统层面和 IP 层面都满足预期规格。

2. 热管理与功率损耗

电路能否可靠运行,不仅取决于供电是否充足,还取决于在运行过程中如何控制损耗和发热。每增加一个功能模块,漏电流和静态功耗都会上升,相应地系统内部温度也会升高。

如果散热处理不当,轻则影响性能和效率,重则导致元件损坏,甚至存在安全风险。因此,在整个设计周期内,始终把热限制与散热策略放在优先级最高的位置,是保障可靠性的前提。

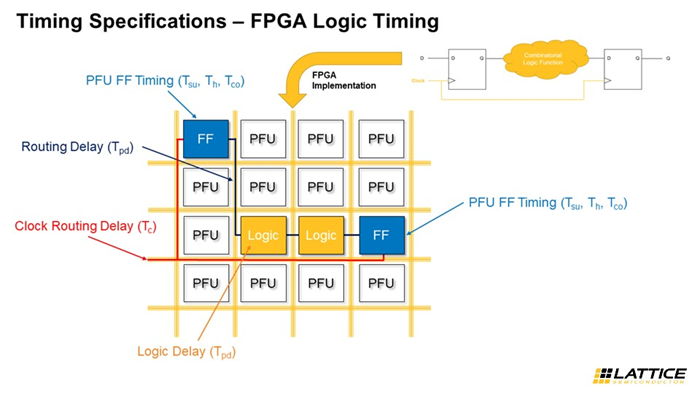

3. 时序与运行速度

时序约束直接影响布局布线,因为走线长度与电阻、能耗等密切相关。合理的时序设计可以避免建立时间/保持时间违例,提升系统的可靠性。

与此同时,时钟域的划分与同步也是 FPGA 设计的核心环节。如果时钟域管理不当,可能出现亚稳态、数据错误,甚至影响功耗和效率。而且这些问题往往在后期难以修复,排查也非常耗时。

总体来看,功耗、发热、时序三者之间相互影响、环环相扣:更高的功耗会增加发热风险,时序优化会占用额外的空间资源,而热限制又会约束算力发挥。因此,设计过程中每一次选择都可能改变系统的整体需求。

验证与测试的重要性

在进入量产前,开发者必须验证 FPGA 设计是否按预期运行。通过测试,可以尽早发现隐藏问题,避免产品上市后出现高额的返工和替换。

此外,如今已有先进的仿真工具,可以在设计早期对方案进行可行性验证,并快速评估变更的影响。借助这些工具,开发者不仅能节省时间和成本,还能尝试更多创新性的设计思路,甚至为未来的芯片迭代建立模板。

自信地运用半导体

像 FPGA 这样的高性能半导体,已经彻底改变了我们与计算系统的交互方式。它们为开发者提供了灵活性、算力和处理能力,使各行业能够落地更多创新应用。

然而,只有在设计中充分考虑功耗、散热、时序等制约因素,并做到平衡取舍,FPGA 的真正价值才能被释放。随着系统复杂度的提升,掌握“平衡的 FPGA 设计之道”,将是通往下一代计算的关键。

本文翻译自:Embedded

(全文完)

声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

759

759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?