关注、星标公众号,精彩内容每日送达

来源:网络素材一、为什么芯片有多个不同的供电电压?

优化性能与功耗:芯片的核心部分(Core)和输入输出部分(IO)可能采用不同的电压。核心电压通常较低,以减少功耗和发热,提高能效;而IO电压较高,以确保与外部设备的兼容性和信号完整性。通常,系统的内核电压(如FPGA的VCCINT)需要先于I/O电压(如VCCIO)上电。这是因为内核电压为芯片的逻辑部分供电,必须在I/O电压之前稳定,以确保数据的正确处理和传输。

模拟和数字电压分离:有些系统可能需要将模拟和数字电路的电源分开,以防止相互干扰。例如,模拟电路可能对电源噪声更敏感,因此可能需要一个独立且更稳定的电源。

电压域的独立上电:在多电压域的系统中,可能需要独立控制每个电压域的上电时序。例如,有些电压域可能需要比其他域更早或更晚上电,以确保系统的正确启动。

电压转换器的选择:不同的电压转换器(如开关稳压器和线性稳压器)可能有不同的上电时序要求。这些要求通常由转换器的设计和负载特性决定。

时序控制器的使用:在复杂的系统中,可能需要使用时序控制器来精确控制每个电压域的上电和下电时序。时序控制器可以监控不同电压域,并在必要时调整上电顺序,以确保系统的稳定运行

电源监控:在有多个电源电压的系统中,监视不同电压的能力可能很重要。许多时序控制器还内置了电源监控器或电压监视功能,以确保每个电压在正确的时间达到其目标值 [^500^]。

电压爬升控制:对于每个转换器,各电压上电的延迟也会不同。这导致不同电压域中的电压爬升不受控制,有可能引起功能问题并损坏系统。因此,通常需要可靠的上电顺序以确保每个电压在正确的时间达到其目标值 。

减少功耗:功耗与电压的平方成正比,降低电压可以显著减少功耗,这对于移动设备尤为重要,有助于延长电池寿命。

二、为什么芯片大都采用低电压大电流的供电方案?

通俗的讲,芯片可以看作由几十亿到上百亿个小开关(场效应晶体管FET)组成的。开关切换的速度f决定了计算机的性能。为了高性能,必须提高开关速度f。而V则因为省电的原因越小越好

![]()

这里要引入门延迟(Gate Delay)的概念。简单来说,组成CPU的FET充放电需要一定时间,这个时间就是门延迟。只有在充放电完成后采样才能保证信号的完整性。而这个充放电时间和电压负相关,即电压高,则充放电时间就短。

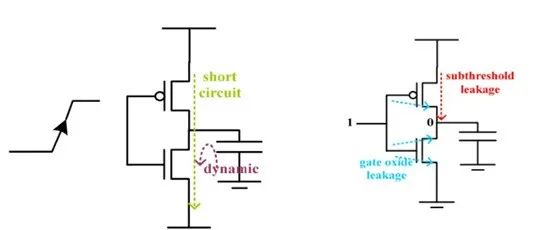

现实情况比这个更复杂。实际上,上面公式里的P只是动态能耗,主要关注占比90%的Dynamic Power,造成Dynamic Power的原因是寄生负载电容的充放电。CPU的整体功耗还包括短路功耗和漏电功耗:

![]()

短路功耗是在FET翻转时,有个极短时间会有电子直接跑掉。它和电压、频率正相关。

漏电功耗是电子穿透MOSFET的泄漏情况,它和制程与温度有关。

电源只是表示最大能提供的能力,负载才决定用了多少。

为什么芯片大都采用低电压大电流的供电方案?

降低功耗:随着晶体管数量的增加,为了减少能耗,需要降低供电电压。功耗与电压的平方成正比,因此降低电压可以有效减少功耗。除了动态功耗外,芯片的功耗还包括短路功耗和漏电功耗。降低电压可以减少短路功耗,而漏电功耗与制程和温度有关。

门延迟:晶体管的充放电时间(门延迟)与电压有关,电压越高,充放电时间越短。但为了节能,需要在保证信号完整性的前提下,尽可能降低电压。

半导体材料的特性:半导体硅管的正向饱和压降约为0.7V,因此不需要太高的电压即可工作。

工艺和电压的关系:随着制造工艺的进步,晶体管的特征尺寸越来越小,这允许芯片在更低的电压下工作,同时减少热效应和提高集成度。

晶体管密度太大导致pn节间距很小,耐压低,不能高压。电压是由制造工艺决定的,越是制成线宽小的工艺,能承受的电压越低,同时寄生电容也更小,使得同频率下单管功耗更低。如果电压太高,意味着制程必须要高很多,如果想5V供电,需要1微米的制程才可以,太小的话,容易击穿,导致损坏。

上百安的电流不是一个Vcc脚提供的,而是很多电源pin分摊的,所以几百个引脚平摊下来上百安的电流也不算太夸张

(全文完)

声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

芯片多供电电压及低电压大电流方案解析

芯片多供电电压及低电压大电流方案解析

2963

2963

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?