关注、星标公众号,精彩内容每日送达

来源:网络素材1、在verilog中有时会用signed修饰符来修饰定义的数据,运算的时候也会用$signed()任务来强制转换数据,那么signed的修饰是为什么呢,是为了区分有符号数和无符号数的加法和乘法吗?其实不是的,因为有符号数和无符号数据的加法强结果和乘法器结构是一样的,signed的真正作用是决定如何对操作数扩位的问题。

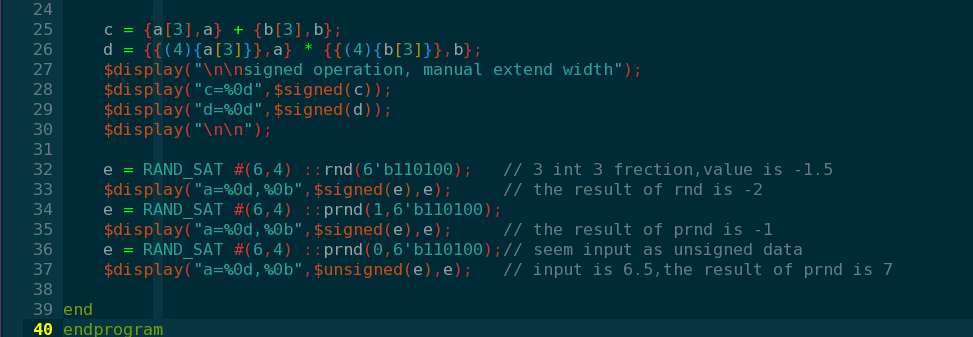

2、verilog中的加法和乘法操作前,会先对操作数据扩位成结果相同的位宽,然后进行加法或者乘法处理。比如a/b都为4位数据,c为5位数据,c = a + b,这个运算的时候会先把a和b扩位成5位,然后按照无符号加法进行相加。a/b没有被signed修饰的时候会按照无符号数的扩位方式进行扩位,即高位补0,加法的结果当然也是a、b为无符号数相加的结果。

3、如果想把a、b作为有符号数来相加,那么就得在a/b数据定义的时候用signed修改,或者在计算的时候用$signed()来修饰,这样在c = a + b,这个运算开始的扩位就会按照有符号数的方式进行扩位,在高位补符号位,加法得出的结果就是a、b视为有符号数的结果。当然c要视为有符号数据。

$signed()函数

返回有符号的值,值得注意的是verilog中的负数其实是{1’b1,pos_num},而并非高级语言中的补码。使用中最好通过增加$signed{1’b符号,正数}来实现转换以避免错误。

此外在对signed wire 或signed reg 赋值时,右侧的所有变量最好全部加上$signed函数转换,以防止遗漏,造成数据错误

signed变量移位操作时最好使用<<<和>>>,防止对符号位进行操作,导致数据出错

(全文完)

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

2378

2378

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?