点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材

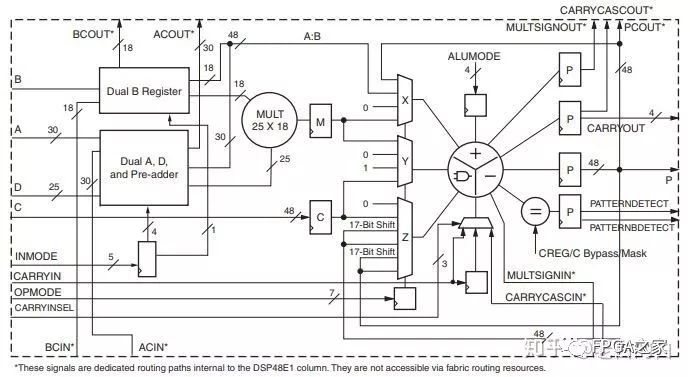

下图为Xilinx 7系列FPGA中使用的DSP48E1的框图

从中我们可以看出,输入有两个寄存器,如果用到后面的加法/减法器,与乘法器之间会有一个寄存器,然后加法/减法器的输出有一个寄存器P。

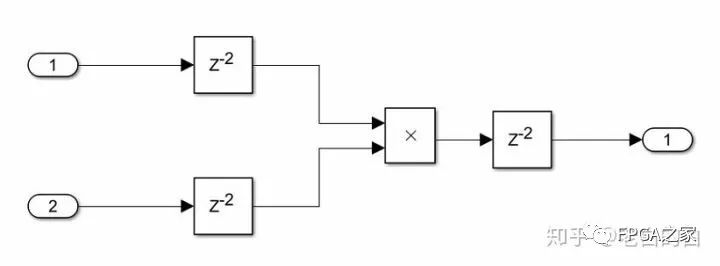

因此,如果我们**仅使用一个乘法器**时,建议在前后都加上一个delay模块并且设置delay length=2。

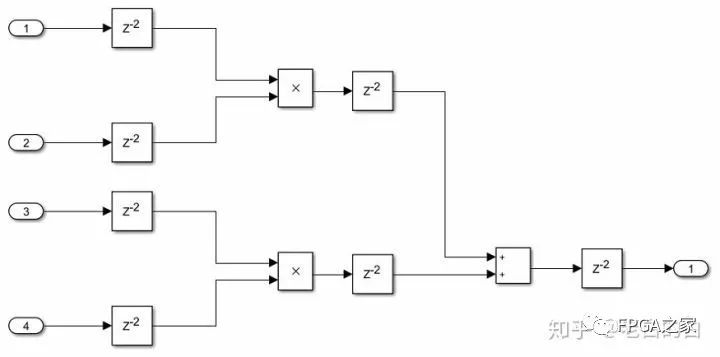

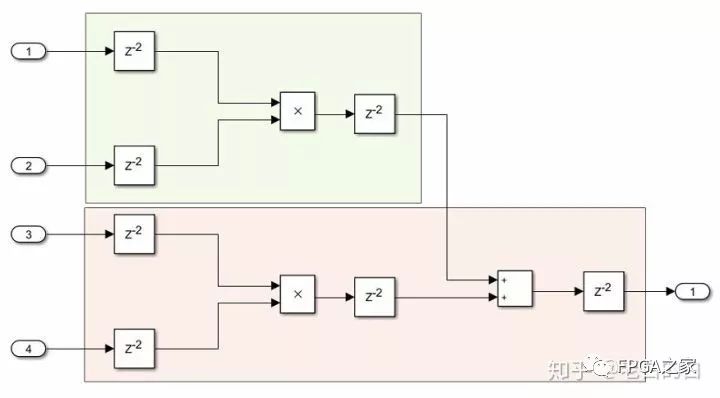

如果我们**设计一个乘法+加法器**时(如图3),

- 建议使用delay length=2的delay模块连接乘法和加法模块(乘法加法之间使用delay length=1也可以)

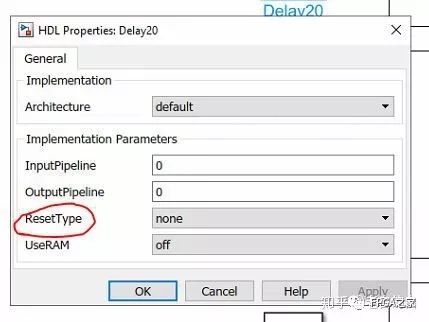

- 右键设置所有delay的HDL Block Properties中ResetType为none,这样做是为了防止全局的reset信号控制内部寄存器,需要额外逻辑,造成Vivado编译器无法优化DSP

如果使用使用HDL Coder生成Vivado项目并且综合之后,我们会发现,这个模块例化了两个DSP模块,其中一个只使用了乘法器,结果通过POUT送入另一个DSP单元进行加法运算。

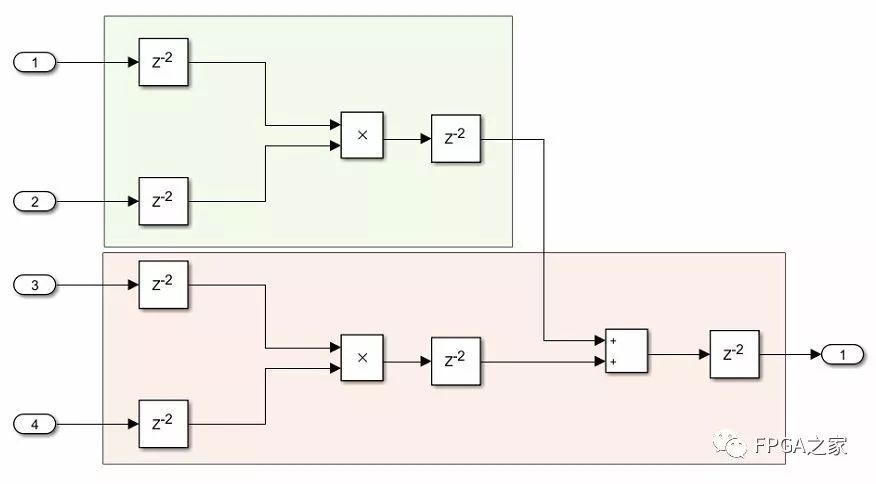

如图5,绿色框和红色框分别代表一个例化的DSP。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?