文章目录

如果再进行元器件设计的时候,元器件的 PIN 上面的标号有横线怎么处理?在输入 PIN Name 的时候添加 \ 即可。

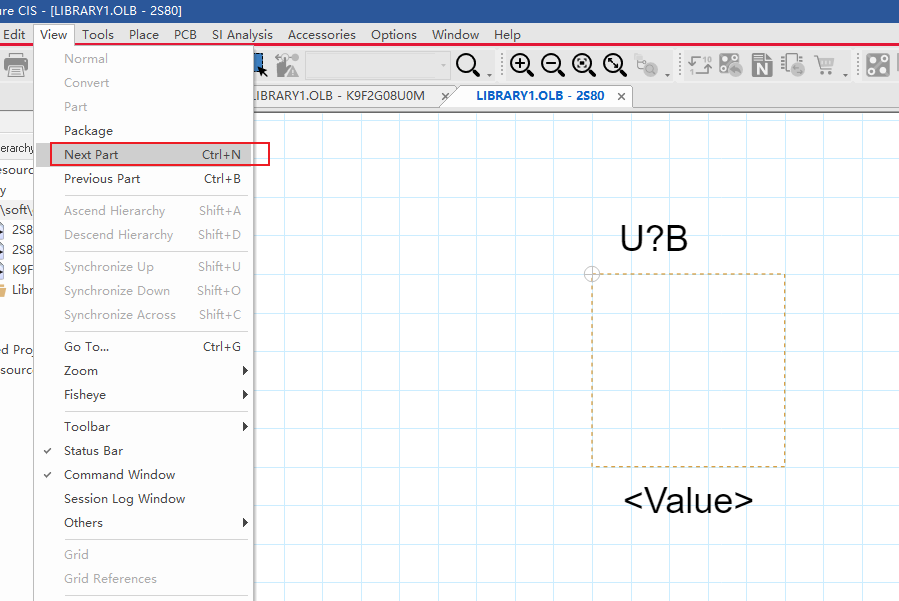

如果创建元器件的话,元器件有两个部分(或者更多),一开始只能看到一个部分,那么其他的部分去哪里找呢?、

- 在 View 里面可以进行部分的切换。

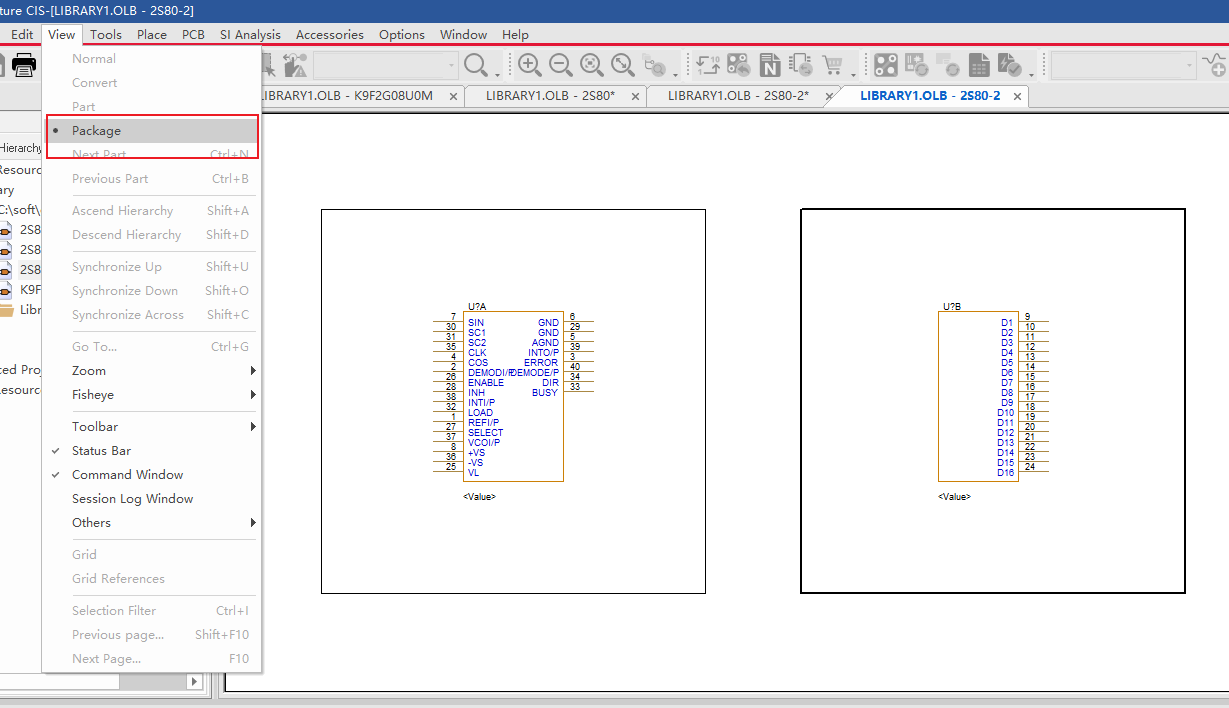

如果是创建元器件有多个部分的话如何同时显示多个部分呢?

- 通过点击 View 中的 Package 就可以看到多个了,其实可以看到啊,他这个弹出来的是一个新的试图框框,如果想看原来单独部分的话,看原来的就好了。

-

关于原理图创建 page 排序问题

基本的是按照字母表顺序进行排序的,但是呢,如果想按照自己的来,那么可以通过统一标序号命名。

调整原理图大小

通过调整 Options 里面的原理图页面属性可以调整原理图的大小,这样当原理图放不下我们的元器件时,就可以放大原理图本身的大小了。

关于在原理图添加元器件

主要需要理解的就是,你需要导入一个元器件的库,库的文件后缀为 .olb , 可以在 part 部分通过添加库,把自己的元器件添加进来,还有一个需要知道的就是 C:\soft\cadense\Cadence\SPB_17.4\tools\capture\library 路径下的 DISCRETE.olb 库还一个通用的元器件库。是软件自带的常常用到。

关于元器件的翻转与旋转问题

通过快捷键 R可以快速的旋转,然后如果要进行水平、垂直翻转的时候就可以选中元器件以后进行鼠标右键,然后就可以看到翻转选项了。

关于绘制原理图-也就是把元器件连起来

总的来说有三种情况吧:

- 方便连接的直接通过导线进行连接,快捷键为

W

- 如果是两个元器件相隔较远,不好用导线进行连接时候,这个时候网络标号就能发挥作用了,网络标号,表示相同的网络标号之间要进行连接,不过暂时不用导线表示。

- 那如果是两个要进行连接的元器件在两个页面中呢?这个时候就可以使用页面之间的连接了。虽然也没有用导线表示,但是就是表示是要连接到一起的,有一定的映射关系。

修改封装属性

如果要修改的那个元器件的封装属性的话直接双击,进入属性面板,然后找的 PCB Footprint进行修改即可。

如果是要进行批量修改的话,那就选中要修改的元器件,然后右键鼠标,找到 EDIT Properties就可以统一修改了。

显示封装信息

需要注意的是:这个操作也是可以直接更改元器件的一些属性,只需要在更新元器件以后,小心选择是更新全部或者单个就好了。

我们在原理图中看一些器件的时候,可能会需要看器件的封装是什么?

虽然可以直接通过双击查看元器件的属性,但是可以通过设置,可以直接显示元器件的封装,这样就能方便一些。

通过选中元器件点击鼠标右键后,选择编辑部件:

然后通过如下步骤就好了

最后全部更新应用,或者也可以选择自己想要更新的。

对页面网络进行页面的标号输出

要进行这一项操作的前提的适合什么,首先需要的就是对页面进行标号,也就是在原理图的右下角对原理图页面进行标号,看图。

原来我没有修改这里的时候,就会一直标号报错,说:There is more than one page numbered one 就是说有多个页面 1 ,原来的样子就是每个页面都是 Sheet 1 of 1

上面的前提设计好了之后那么如何进行标号呢?

没标页号前:

首先选择整个 .dsn文件,点击 tools 中的 Annotate(注释)

然后进入选择参数页面,要注意的就是选择页号偏移大小,一般 20 左右

ok 了

DRC 检查入口

生成网络表

网络表介绍:

什么是网络表?

网络表(Netlist)是电子设计自动化(EDA)领域中的一种关键数据文件,用于描述电路的结构与连接关系。它记录了电路中所有元件(如电阻、电容、集成电路等)的详细信息,以及这些元件之间的电气连接(即“网络”或“节点”)。网络表通常以文本格式存储,是原理图(Schematic)与物理布局(PCB Layout)之间的核心纽带。

网络表的核心内容

- 元件清单:列出电路中所有元件的名称、类型(如电阻值、电容值)、封装信息等。

- 连接关系:定义元件引脚之间的电气连接,即哪些引脚通过导线或网络相连。

- 层次结构(可选):支持复杂设计的模块化描述,例如子电路或IP核的引用。

网络表生成位置:

设置交互布局

只有设置了交互布局,原理图和 PCB 才能进行交互上

只有勾选了交互,才能正确哦

要交互布局的话,还需要先生成网络表!

如何进行搜索器件和网络

同时如果要想在同一个页面中搜索相同网络的话,直接右击选中元器件,然后选择相应网络,然后网络就会高亮了

4609

4609

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?