一、SignalTap II Logic Analyzer 简介

SignalTap II Logic Analyzer(信号逻辑分析仪),用于FPGA烧录调试时,抓取指定引脚、寄存器、ROM地址等所存储的数据值。它使用的是FPGA的片上资源(逻辑资源、RAM资源),所以一次波形抓取的最大深度与你的开发板片上资源、以及你程序代码所使用了的资源有关。

二、SignalTap II Logic Analyzer 使用

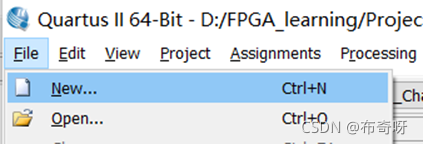

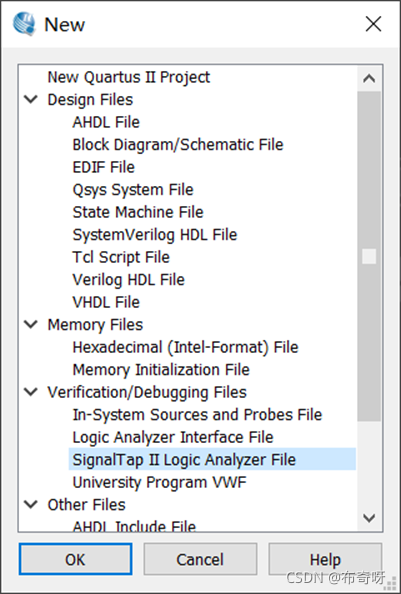

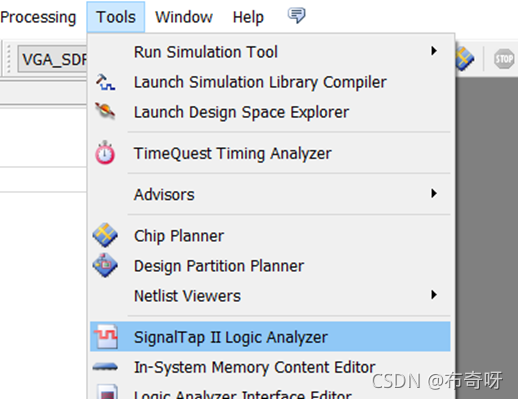

1、新建SignalTap文件

或者

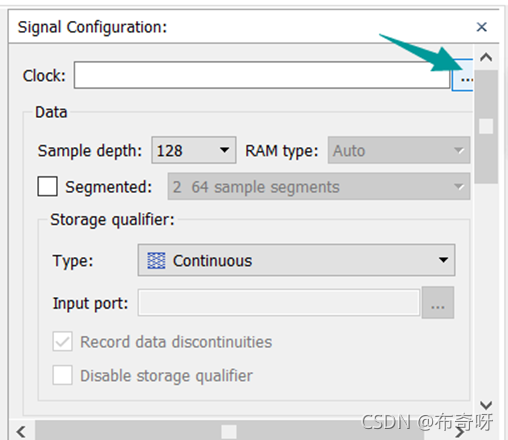

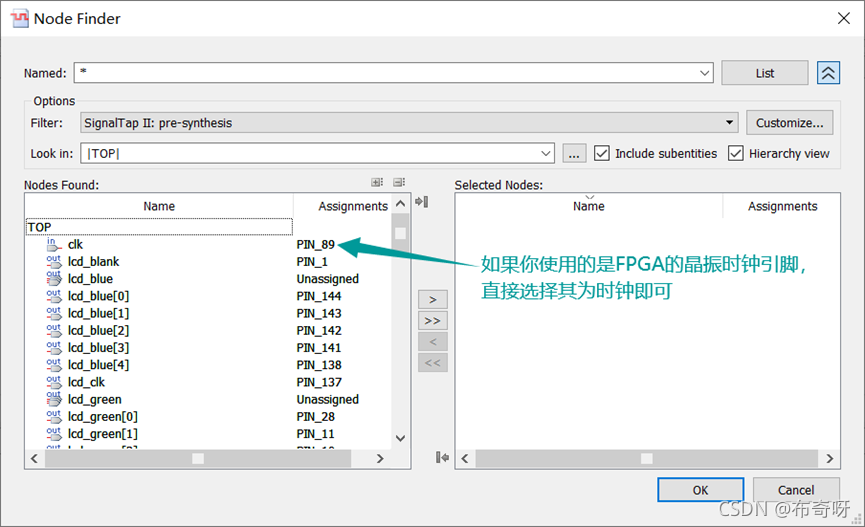

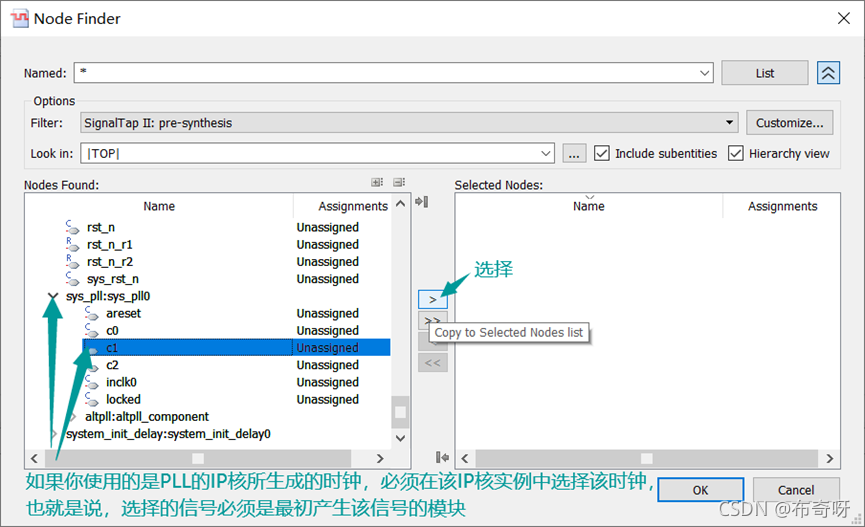

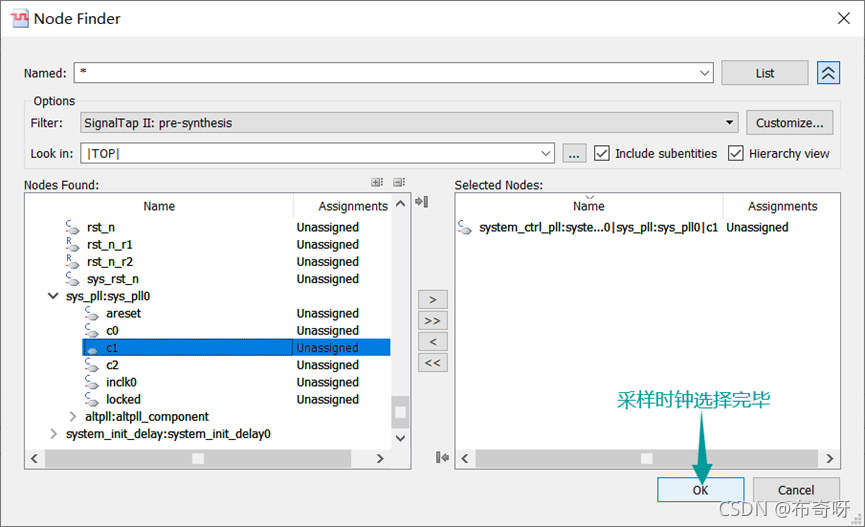

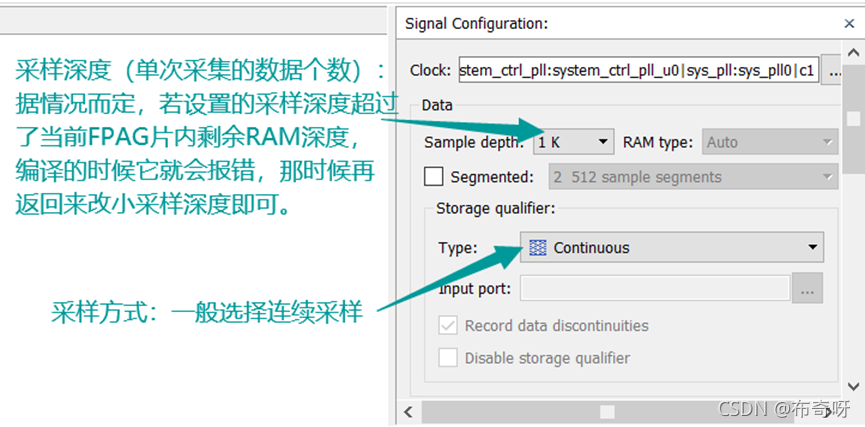

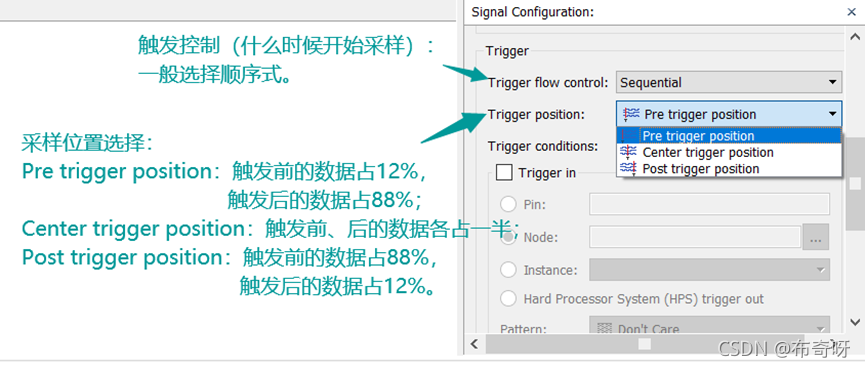

2、设置采样时钟

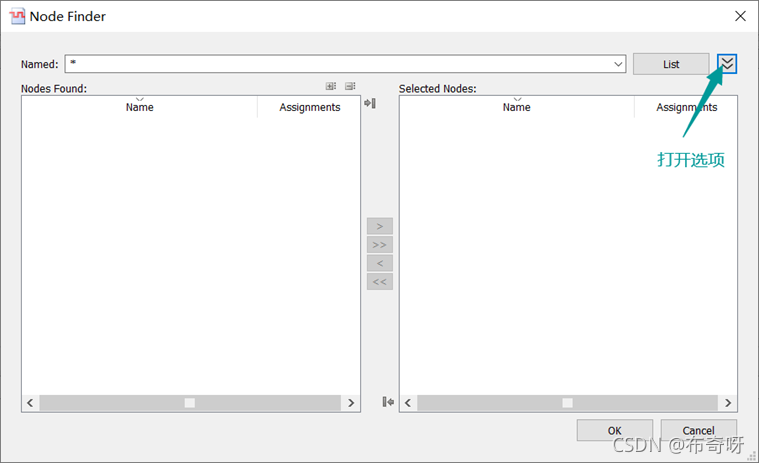

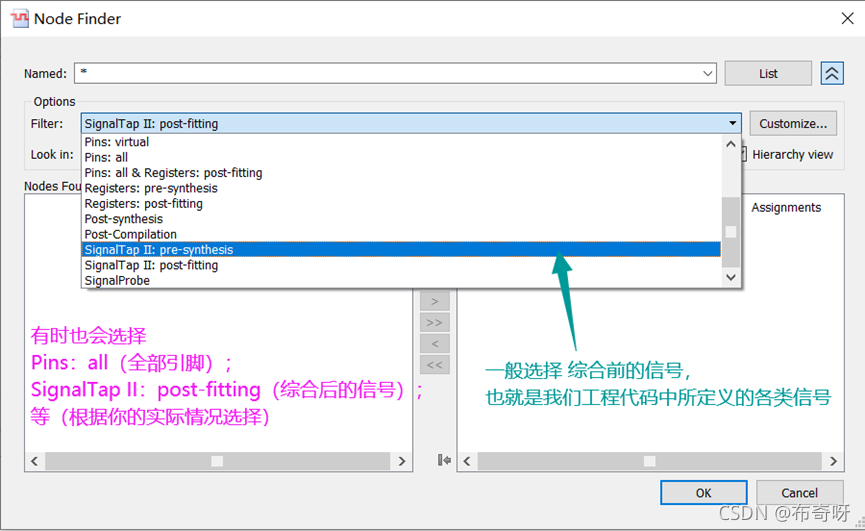

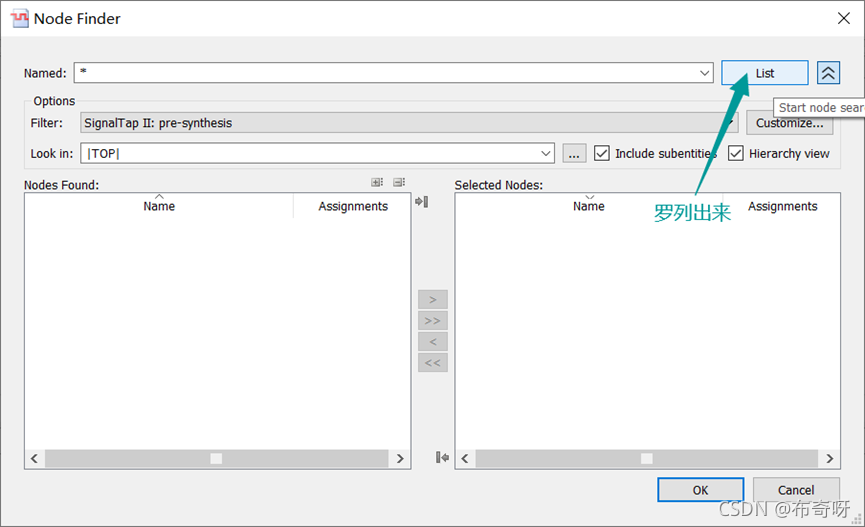

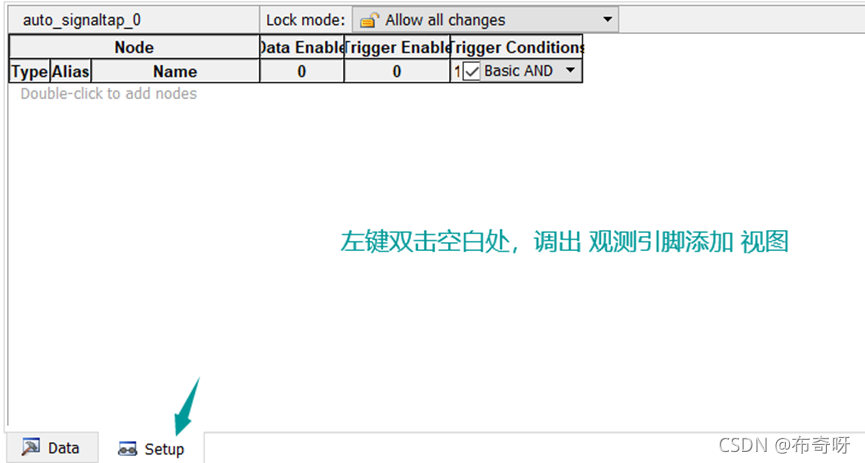

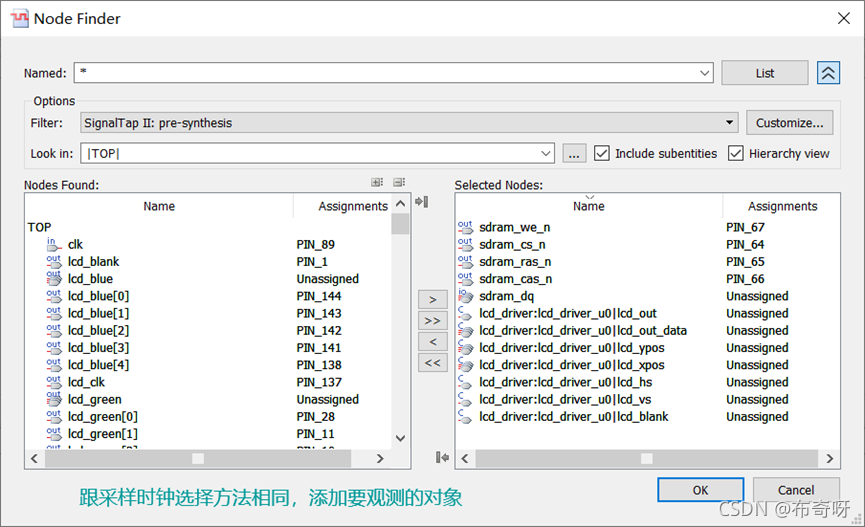

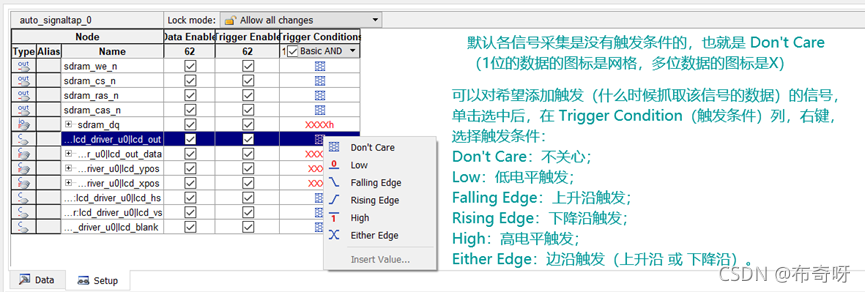

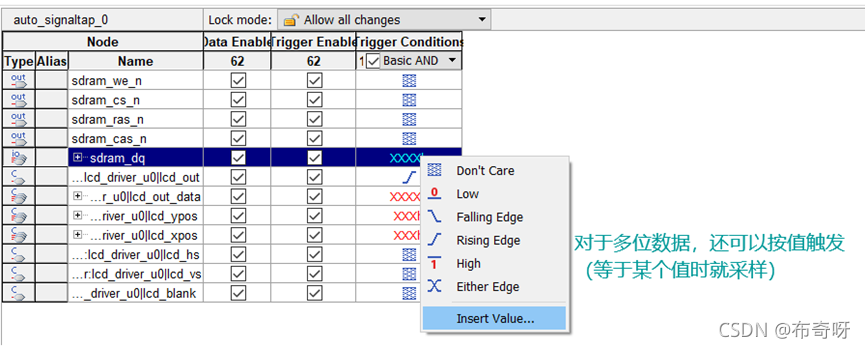

3、设置要观测的对象

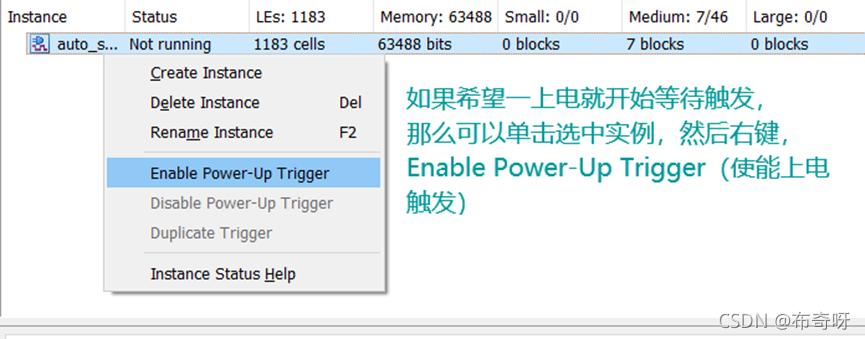

4、是否一上电就开始等待触发

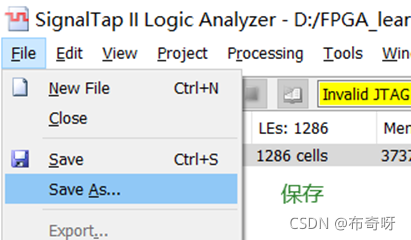

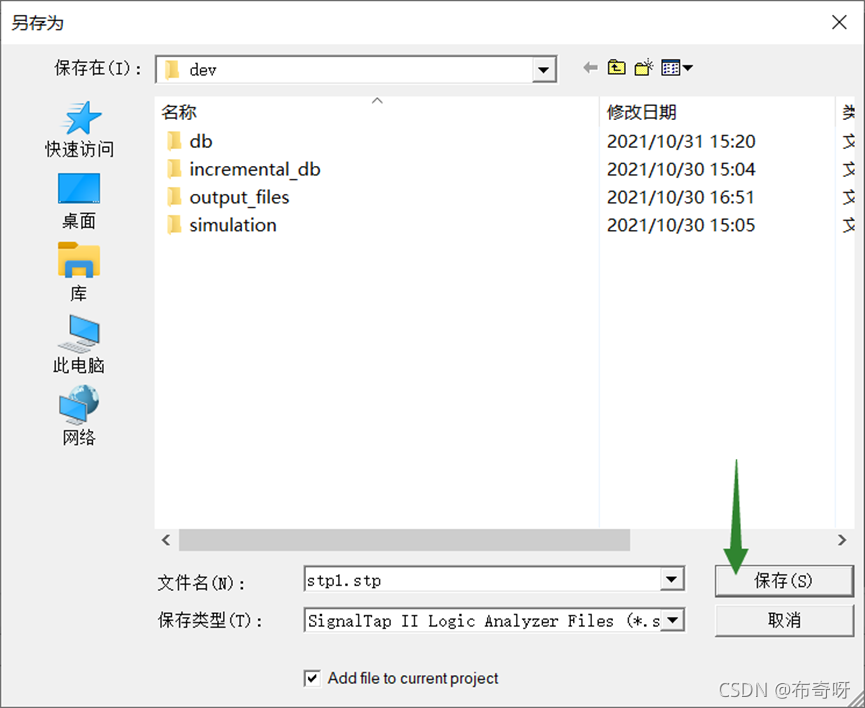

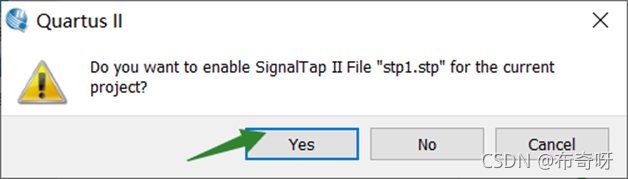

5、文件保存

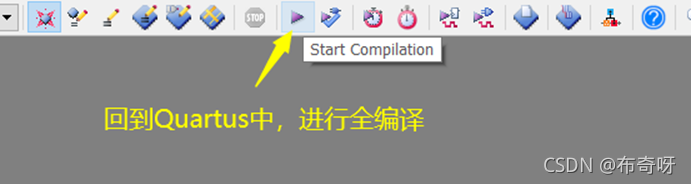

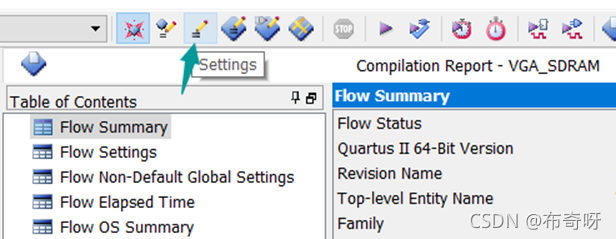

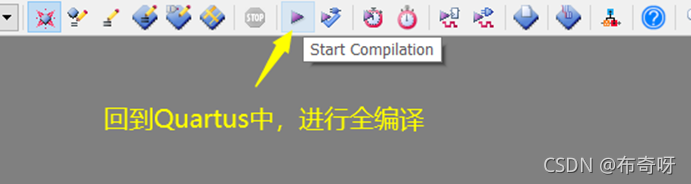

6、重新编译

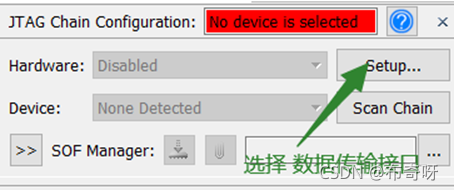

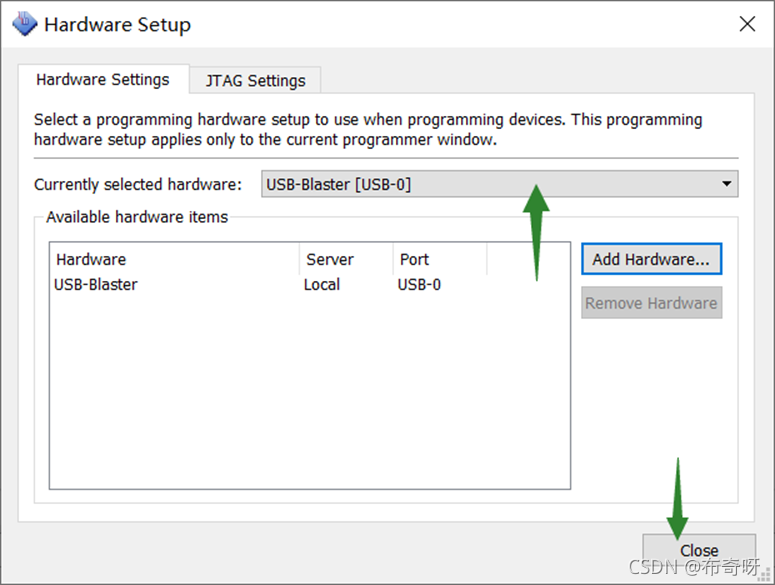

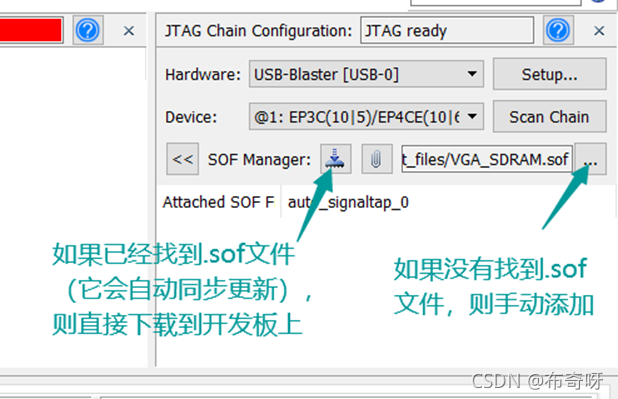

7、设置数据传输接口

8、上电烧录

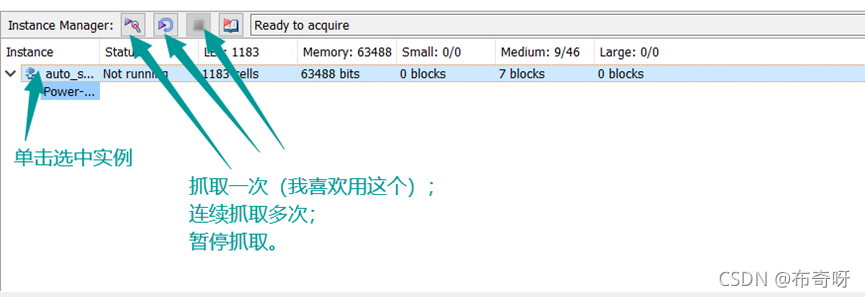

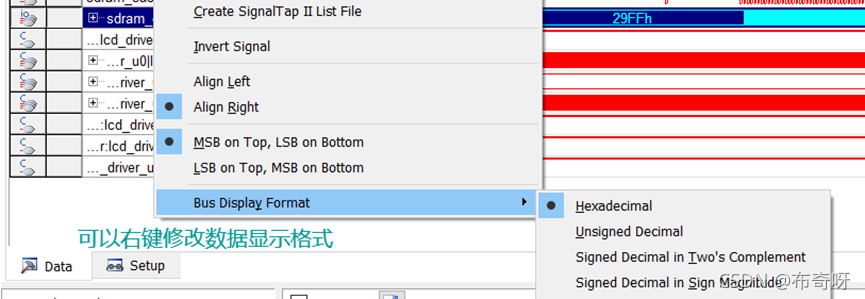

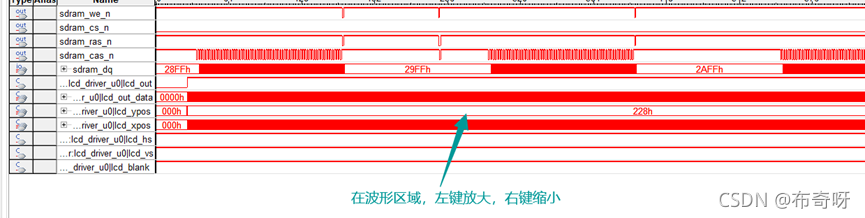

9、抓取波形

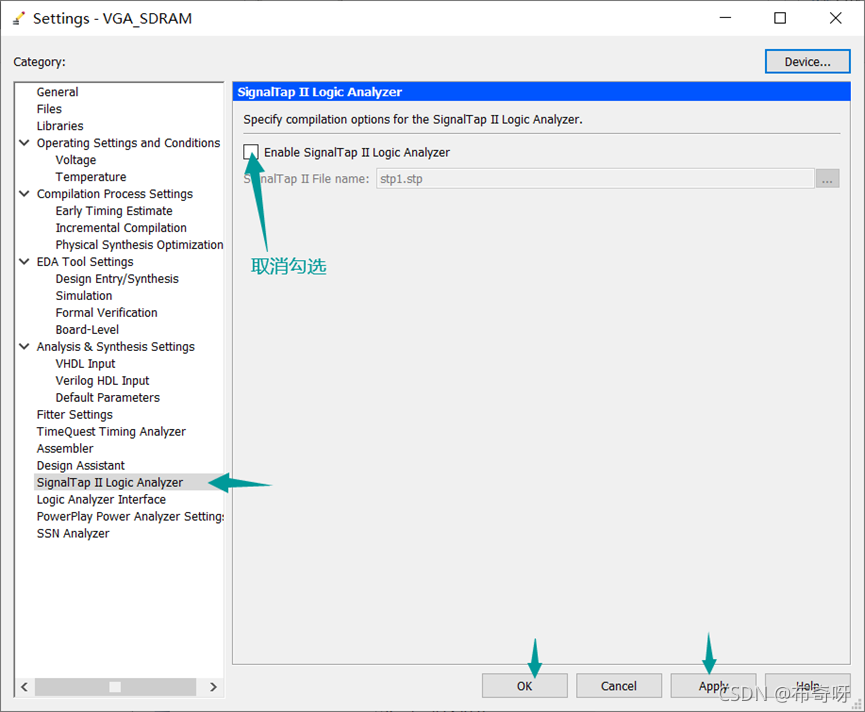

10、在工程中移除逻辑分析仪文件

若抓取的波形符合预期,则要将该.stp文件从工程中移除,避免其占有FPGA的逻辑、RAM等资源。

本文详细介绍了如何使用SignalTap IILogicAnalyzer进行FPGA的波形抓取,包括新建文件、设置采样、配置观测对象、烧录流程及资源管理。从创建SignalTap文件到移除逻辑分析仪,涵盖了全程操作步骤。

本文详细介绍了如何使用SignalTap IILogicAnalyzer进行FPGA的波形抓取,包括新建文件、设置采样、配置观测对象、烧录流程及资源管理。从创建SignalTap文件到移除逻辑分析仪,涵盖了全程操作步骤。

2056

2056

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?