working environment:

Linux

Steps

- Open RTL project:

open quartus under Linux:

quartus

open project file (file that ends with .qpt) - Signal tap II

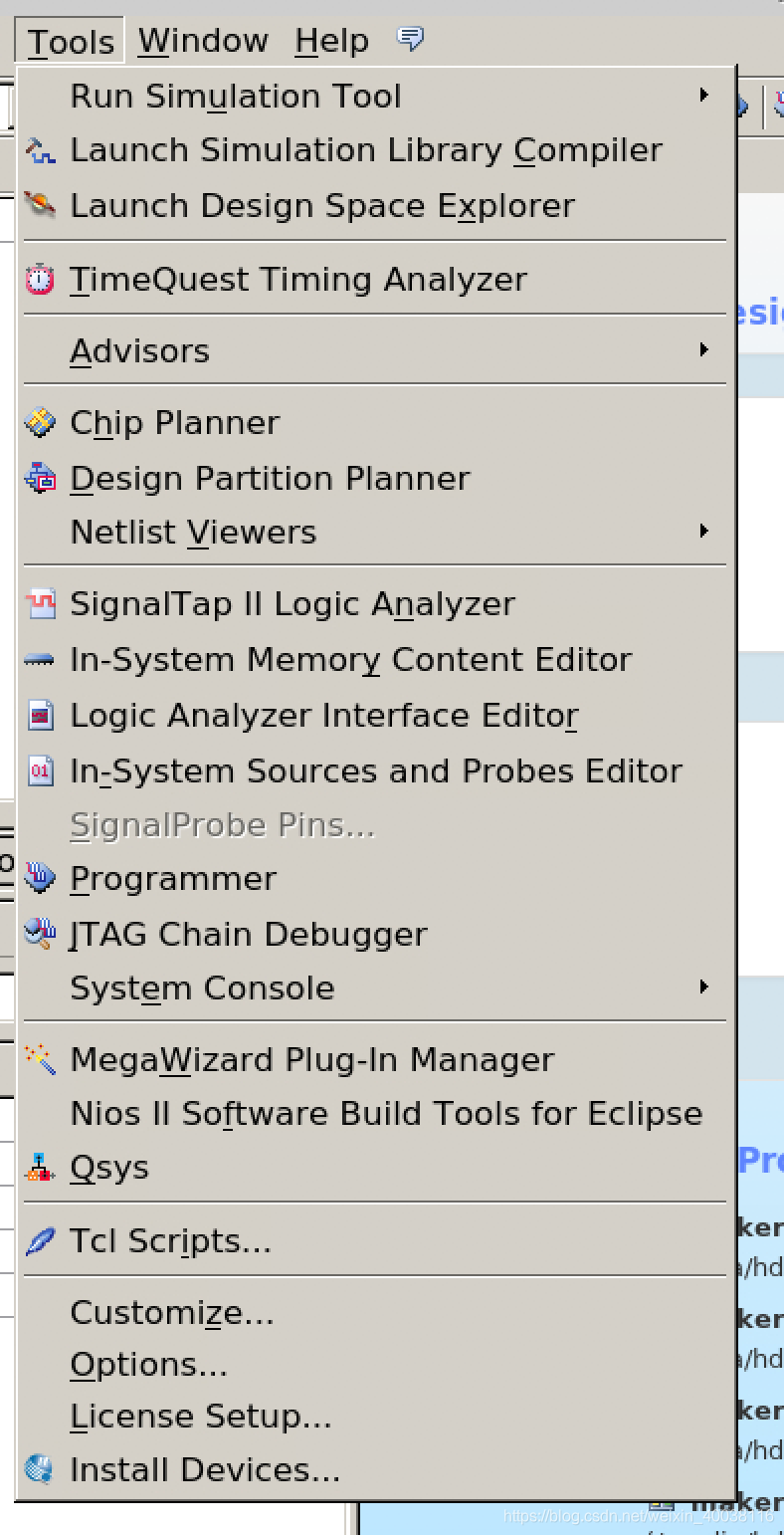

Tool -> singal Tap II

- Adding clock

signal configuration -> name:clock -> filter: Signal Tap II Pre-synthesis -> list - Adding signal that you want to test

double click in the window, adding signals and hit ok

filter: pre synthesis - Hit save, xxx.stp file will be generated

- Synthesizing the project, generating bit file “.sof”

- export your bit file to FPGA

- open signal Tap II analyzer

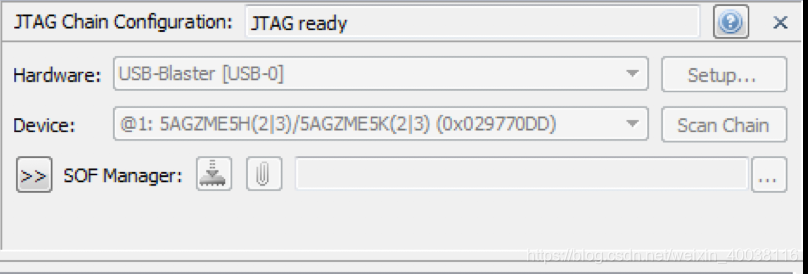

- Hit “hardware” to connect to your JTAG

- Prob the posdege of the signal that you want to trigger the test

- Programming your bit file on Altera FPGA and start testing(mine FPGA is from Altera Arria V)

在Linux环境下使用Quartus Signal Tap II进行FPGA调试,包括打开RTL项目,设置Signal Tap II,添加时钟和待测试信号,预综合过滤器配置,保存生成.stp文件,合成项目并生成.bit文件,最后将位文件导出到FPGA,通过JTAG连接Signal Tap II分析器,触发测试并编程FPGA开始测试。

在Linux环境下使用Quartus Signal Tap II进行FPGA调试,包括打开RTL项目,设置Signal Tap II,添加时钟和待测试信号,预综合过滤器配置,保存生成.stp文件,合成项目并生成.bit文件,最后将位文件导出到FPGA,通过JTAG连接Signal Tap II分析器,触发测试并编程FPGA开始测试。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6015

6015

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?