在智能手机、AI 服务器等高性能设备的核心深处,12nm 及以下先进工艺的 FinFET 晶体管正以惊人的集成度支撑着算力爆发。但随着芯片特征尺寸迈入纳米级,一个看似微小却足以导致产品批量失效的隐患 —— 静电放电(ESD)问题,正成为行业痛点。与传统平面晶体管不同,FinFET 的 ESD 失效并非简单的电流过载,其核心根源隐藏在难以消散的热量中,而预测性 TCAD 模拟正成为破解这一难题的关键。

- 反常的失效:FinFET 的 ESD 防护困局

对于传统平面晶体管,ESD 失效多发生于电流聚集的载流区域,其失效机理清晰,防护方案易于落地。但 FinFET 技术却打破了这一规律:研究发现,12nm FinFET 的输入 / 输出晶体管在击穿前几乎不承载大电流,击穿现象仍聚焦于阵列中心区域,这与以体区为电流承载核心的平面工艺特性表现一致。这一 “反直觉” 现象,让不少芯片设计者陷入困惑。

更严峻的是,随着工艺向 7nm、5nm 推进,ESD 设计窗口正急剧收缩。数据显示,从 350nm 到 7nm 节点,SG FET 的栅氧化层击穿电压(Vgox)下降了约 87.5%,在 22nm 到 7nm FinFET 节点中稳定在 2.5V—3V 的低水平;而失效电流(It2)在 22nm 平面工艺到 FinFET 工艺间再下降 ,致使 ESD 防护的容错余量持续缩减。

对 14nm FinFET SRAM 的研究还发现,局部布局效应(LLE)会进一步加剧可靠性风险。氟扩散导致传输门(PG)阈值电压(Vtsat)降低 23mV(1Fin 结构),浅沟槽隔离(STI)应力使阵列边缘器件 Vtsat 下降 15mV,栅切割(Gate-cut)的自然变异则造成 13% 的 Vth 失配,这些因素协同引发访问干扰裕度(ADM)显著下降,进行高温老化测试时极易出现失效

- 热效应主导:FinFET 失效的核心机制

FinFET 的 ESD 失效之所以呈现 “反常” 特征,核心在于其特殊结构引发的热传导困境。

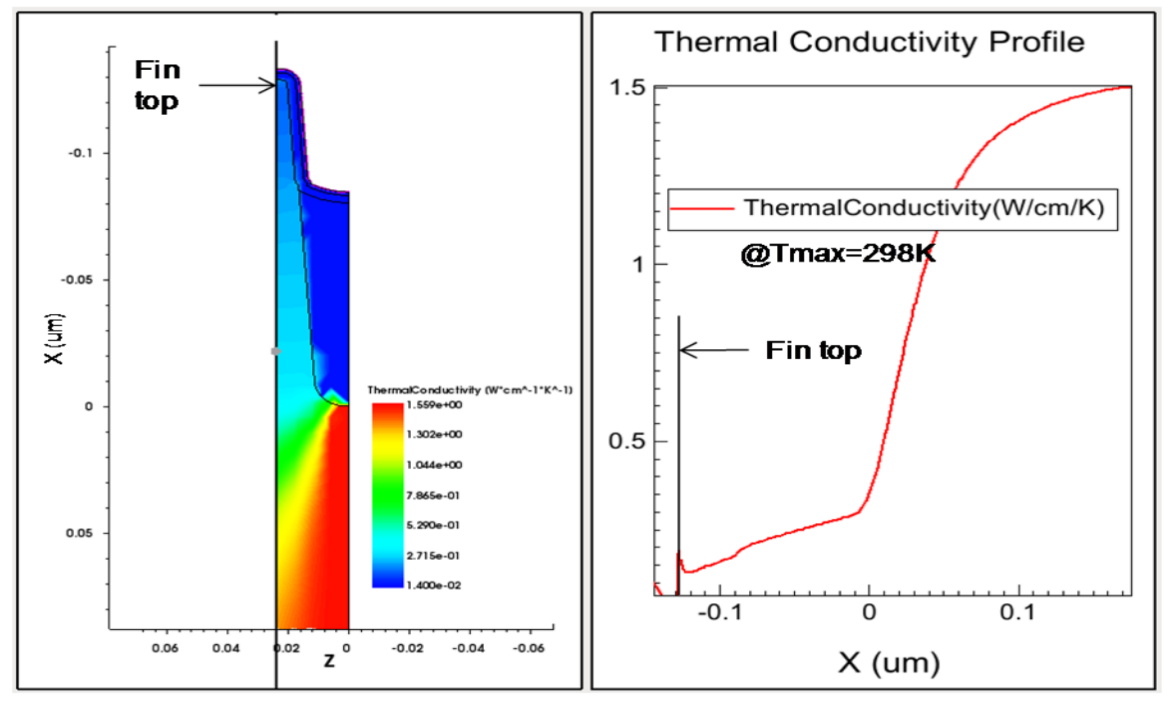

某全球晶圆代工厂团队通过实验发现,FinFET 鳍片中的热导率比体硅材料低约 87.5%,这意味着热量无法像传统平面晶体管那样高效向外传导,只能在鳍片区域局域积聚,最终引发热失控。

图 1:FinFET 结构中的热传导特性(热导率随硅厚度变化关系)

热导率的强依赖性是关键诱因:当硅厚度减小时,热导率呈指数级下降,而 FinFET 的鳍片厚度通常仅几十纳米,恰好处于热导率急剧衰减的区间。通过预测性 ESD TCAD 平台量化分析发现,硅厚度、鳍片数量与热导率形成明确的定量关系,热效应已从过去的次要因素,升级为引发 ESD 失效的核心主导机制。

电流 filamentation(丝化)现象进一步放大了热风险。在 ESD 应力下,GGNMOS 器件会经历三个阶段:首先是电不稳定性(EI)引发非均匀导通和细丝形成,随后在硅化物阻挡型器件中出现细丝扩散和均匀导通,热不稳定性最终致使热失控失效发生。而硅化物掺杂型器件因缺少细丝扩散阶段,在 EI 后直接进入热失控,失效阈值显著降低。

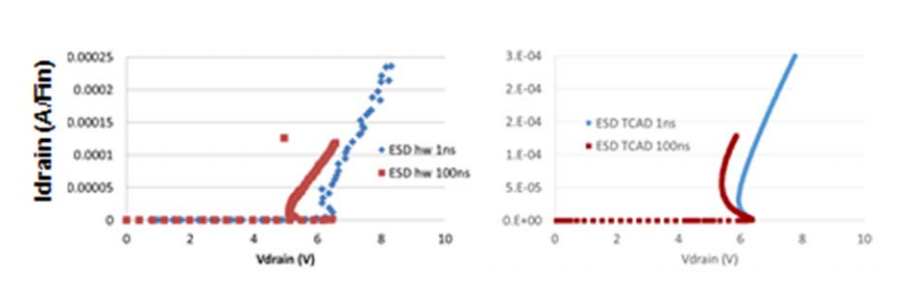

TLP(传输线脉冲)脉冲宽度对ESD性能有着显著影响。脉冲宽度越大,产生的温度越高,这会延长载流子寿命,进而降低维持电导调制状态所需的维持电压。这表明,即便芯片设计完全相同,不同的TLP测试条件也可能导致ESD鲁棒性评估结果出现显著差异。更长的脉冲因加剧热积累效应,反而使器件的失效阈值降低,进一步凸显了热效应对ESD可靠性所起的决定性作用。

图2:TLP脉冲宽度效应对比(100ns与1ns脉冲的温度变化)

- TCAD 模拟:从预测到破解的关键工具

应对 FinFET 复杂多样的 ESD 失效机理,传统的实验测试方式无法全面覆盖各类场景,预测性 TCAD 模拟成为行业突破的关键工具。某全球知名 Foundry 团队开发的 12nm FinFET ESD TCAD 平台,首次实现了热导率与硅厚度、器件拓扑(鳍片数量、活性硅区域数量)的精准关联,为失效预测提供量化参考。

该 TCAD 平台的核心价值在于全流程校准:通过匹配硬件热电阻(Rth)数据,修正自加热模型、边界热阻等参数,使晶格温度模拟误差控制在 5% 以内。相较于未校准模型,经校准的 TCAD 可精准复现 TLP 曲线的四个关键节点(击穿前、触发点、维持点、失效点),并精准预测故障位置 —— 与物理失效分析(PFA)结果一致,故障集中在衬底电阻较高的鳍片中心区域,边缘低电阻鳍片则不会被触发。

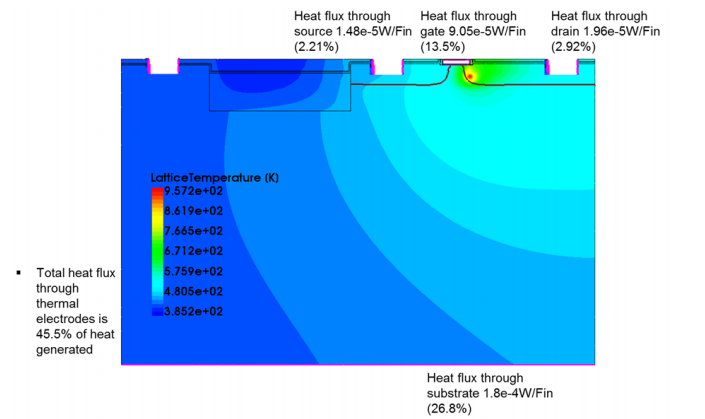

TCAD 模拟还揭示了热转换的关键细节:ESD 应力下,器件输入的全部电功率均转化为热能,其中仅 45.5% 通过热电极流出,其余 54.5% 被器件吸收导致晶格温度升高。这一发现为防护设计提供了明确方向 —— 优化热传导路径、提升热电极散热效率,可有效提升 ESD 鲁棒性。

图3:热转换与通量示意图(45.5%热量通过热电极流出)

针对 14nm FinFET 的 LLE 问题,TCAD 模拟同样发挥了重要作用。通过布局拆分验证发现,优化栅极接触间距、增加传输门(PG)的金属功函数厚度、调整 STI 结构应力分布,可分别补偿 17mV、10mV、20mV 的 ADM 退化,为 SRAM 单元的布局优化提供了量化指导。

- 设计突围:FinFET ESD 防护的实用策略

基于对热效应和 LLE 机制的深入理解,行业已形成一套切实可行的 FinFET ESD 防护设计策略,结合 TCAD 模拟可实现防护能力的显著提升。

在结构参数优化方面,通过调控鳍片数量和硅体厚度可直接改善热传导特性。增加鳍片宽度能降低热阻和电阻,使器件温度降低 7%—17%;优化鳍片间距可减少热耦合,实验表明 100nm 间距比 50nm 间距的中心鳍片温度降低 15% 以上;采用硅化物阻挡技术可改变基板电流路径,使保持电压提升 20% 以上,促进电流扩散,延长热失控时间。

电路设计层面,串联电阻的合理配置仍具备有效性,但需关注 FinFET 特有的边际效应。实测数据表明,180nm 工艺中增设 25Ω 串联电阻可使 Vt2 提升至 5.6 倍,而 14nm FinFET 工艺中仅能提升 1.6 倍,因此需通过 TCAD 模拟优化电阻参数与布局位置。针对 7nm 及以下先进工艺,输出驱动级需补充次级 ESD 防护元件,以补足 CDM(带电器件模型)防护能力的短板。

测试规范优化,测试规范的迭代亦不可或缺。由于 TLP 脉冲宽度对测试结果影响较大,建议同步采用 1ns vfTLP 与 100ns TLP 两种测试条件,全面评估器件在不同 ESD 场景下的鲁棒性; “高 - speed 串行接口测试需同步采用 1ns vfTLP 与 100ns TLP,CDM 目标水平建议从 250V 下调至 150V,平衡防护能力与电容负载”实现防护能力与信号完整性的平衡。

- 行业启示与未来展望

FinFET 技术的 ESD 防护挑战,本质上是芯片微缩过程中 “电 - 热 - 结构” 耦合效应的集中体现。这一挑战倒逼行业从设计思维上实现范式转变 ——“热” 不再是边缘因素,而是与电学性能同等重要的核心考量。

现阶段,融合物理机制的 TCAD 平台已深度融入 FinFET 设计流程。借助与 EDA 工具的深度协同,工程师能够在流片前精准预测 ESD 失效点、优化布局参数、验证防护方案,使设计迭代周期缩短超 30%,大幅降低研发成本。

未来,随着工艺向 3nm、2nm 推进,热力学模型将成为芯片设计的标配。AI 与 TCAD 的结合将进一步提升预测精度,实现热效应与 LLE 的实时优化;新型散热结构和防护材料的研发,将与设计优化形成协同,为 FinFET 的 ESD 防护开辟新路径。

对芯片行业而言,FinFET 的 ESD 防护难题挑战与机遇并存。它推动着设计、模拟、制造全产业链的技术升级,最终将使先进工艺芯片在保持高性能的同时,实现更高的可靠性。

500

500

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?