为什么 ESD 设计窗口是芯片可靠性的 “生命线”?

在智能手机、自动驾驶芯片等电子设备中,一个看不见的威胁始终存在 —— 静电放电(ESD)。

当人体携带的静电触碰芯片管脚时,瞬时可达数千伏的电压有可能直接损坏内部电路。而 ESD 设计窗口,正是芯片设计师为抵御这种威胁划出的 “安全防线”。

探索 ESD 设计窗口,对提高芯片可靠性、适应先进工艺具备不可替代的价值。以下通过多个实际案例,揭示 ESD 设计窗口研究的核心价值。

一、什么是 ESD 设计窗口?

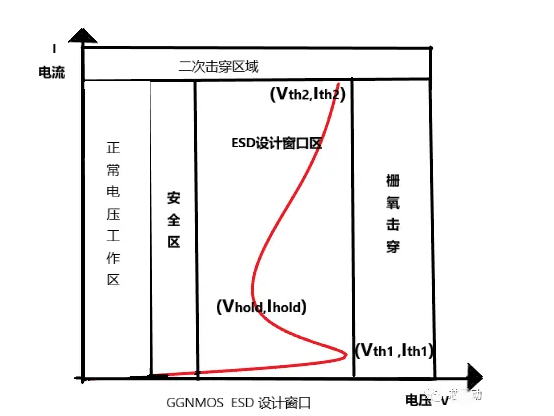

ESD 设计窗口是芯片在正常工作与 ESD 防护之间划出的 “安全工作区间”,通过电压 - 电流(I-V)特性曲线直观呈现。以最常见的 GGNMOS 器件为例,其设计窗口包含五个核心区域(如图 1 所示):

(示意图 1:包含正常工作电压区、安全区、ESD 设计窗口区、栅氧击穿区、二次击穿区,标注 Vth1、Vth2、Vhold 等关键参数)

二、研究 ESD 设计窗口的三大核心价值

1. 保障芯片正常工作,避免 “误动作”

案例 1:智能手表侧键 ESD 失效与优化

某智能手表在侧键附近进行ESD测试后发生反复开关机问题,类似于长按电源键的行为。经分析,问题源于位置 1 的电容耐压值不足(25V)且未贴 TVS 管,导致 ESD 能量直接损坏电容。

通过将电容更换为 TVS 管,并在侧键 FPC 附近增加 GND 露铜区域引导静电泄放,问题得以解决。这一案例验证了 ESD 设计窗口中 “安全区” 的重要性 —— 若维持电压(Vhold)低于工作电压,防护器件可能误触发导致逻辑混乱。优化后,通过提升 TVS 管的触发电压(Vt1)和维持电压(Vhold),确保正常工作时防护器件处于关闭状态。

案例 2:USB 接口 ESD 导致黑屏死机

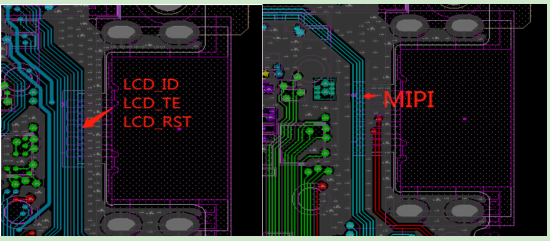

同一款智能手表在 USB 接口注入 ±10KV 接触放电时出现黑屏,定位发现悬空的 ID 管脚积累静电后对周围敏感信号放电,同时 GND 局部电平抬高干扰了 MIPI 等信号。

通过将 USB_ID 管脚接地、优化 GND 过孔分布,并将敏感信号远离接口,成功避免了二次放电。这体现了 ESD 设计窗口中 “安全裕度” 的必要性 —— 预留 10%~20% 的电压冗余可防止电压波动触发误动作。

2. 平衡防护能力与设计约束,突破 “窄窗口” 困境

案例 3:台积电 3nm 工艺的 ESD 设计突破

伴随制程节点减小,ESD 设计窗口连续变窄。例如,根据IRPS数据,40nm典型窗口为3V,7nm缩减至1.5-2V。台积电与某三方技术公司合作开发的 3nm 工艺中,采用新型可控硅(SCR)结构替代传统 GGNMOS,在 0.75V 电源电压下实现 8kV HBM 防护,同时将电源钳位电路面积缩减66%。通过调整 SCR 的触发电压(Vt1)和维持电流(Ihold),在窄窗口中实现了高电流泄放能力(TLP 测试耐受 10A 电流)。这一案例证明,通过器件结构创新可在有限窗口内平衡防护能力与面积约束。

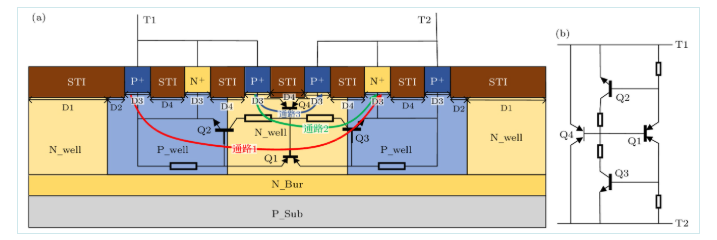

案例 4:内嵌横向 PNP 晶体管的新型 ESD 器件

某研究所提出的 PNP_DDSCR 器件,通过嵌入横向 PNP 晶体管优化 ESD 设计窗口。与传统 DDSCR 相比,其触发电压降低 31%,维持电压提高 16.8%,设计窗口优化 44.5%。在 VF-TLP 测试中,过冲电压仅为传统器件的 37%,同时保持快速触发速度。该结构的创新为窄窗口下的高电流泄放提供了新思路。

PNP_DDSCR器件结构剖面图与等效电路图

3. 抵御闩锁效应,提升极端环境可靠性

案例 5:汽车芯片高温下的闩锁规避

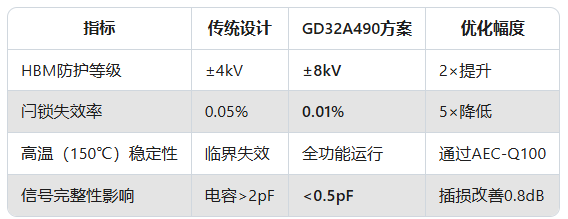

汽车电子需在125℃以上高温条件下工作。传统体硅器件易因漏电流激增和闩锁效应失效。采用 SOI 技术后,介质隔离消除了寄生双极晶体管,漏电流降低至体硅的 1/50,同时通过优化维持电压(Vhold > VDD)和维持电流(Ihold > 工作电流),成功避免闩锁。例如,某车规级 MCU 通过双级 TVS 二极管(主二极管 15pF + 箝位二极管 5pF)和保护环设计,实现 ±8kV HBM 防护 并通过 AEC-Q100 Grade 0 认证。

案例 6:高温对 MOSFET 维持特性的影响

研究表明,NMOS 器件的维持电压(Vhold)随温度升高而降低,在 195℃时可能低于电源电压导致闩锁。通过 TCAD 仿真发现,温度升高会削弱寄生双极晶体管的电流增益(β),而增大体电阻(R_body)可补偿这一效应。某 0.18μm SOI 工艺的 NMOS 器件通过优化掺杂浓度,将 Vhold 从 1.2V 提升至 1.5V,确保在 150℃环境下仍满足 Vhold > VDD 的要求。

- 未来挑战:更窄的窗口,更高的要求

案例 7:某公司车规级 MCU 的 ESD 设计

合规芯片需满足 AEC-Q100可靠性标准,其中ESD防护是核心指标之一。该公司某系列 MCU 采用 24nm 工艺,通过双级 TVS 二极管结构和 0.5μm 间距的保护环设计,在 150℃引擎舱环境下实现 ±8kV HBM 防护。量产数据显示,闩锁失效比例从 0.05% 降至 0.01%。该案例表明,在先进工艺中,全芯片协同设计(如电源轨与 I/O 端口的防护网络)是应对窄窗口挑战的关键。

结语

ESD 设计窗口是芯片可靠性的 “压舱石”。从消费电子到汽车芯片,其研究价值不仅在于避免静电损坏,更在于推动先进工艺下的设计创新。例如,台积电 3nm 工艺的 SCR 结构、某研究所的 PNP_DDSCR 器件,以及车规级 MCU 的双级防护设计,均为 ESD 设计窗口的优化提供了可借鉴的路径。将来,伴随 3nm 及以下工艺的推广,对设计窗口的精细化探讨将变为芯片本土发展的关键议题之一。

1314

1314

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?