更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们。

查找表的一个重要功能是用作逻辑函数发生器。本质上,逻辑函数发生器存储的是真值表(Truth Table)的内容,而真值表则是通过布尔表达式获得的。在Vivado中,打开网表文件,选中相应的LUT,可在属性窗口中查看真值表。从逻辑电路的角度看,查找表是构成组合逻辑电路的重要单元,正因此,也成为时序路径中影响逻辑级数的重要因素。了解常规逻辑电路的逻辑级数对于设计初期的时序评估是很有必要的。

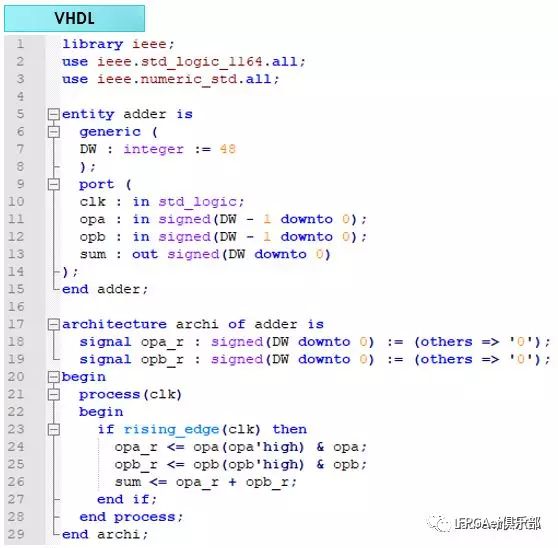

以加法器为例,相应的RTL代码如下图所示。

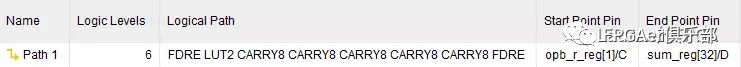

对于16-bit有符号加法运算,其逻辑级数为3,如下图所示。

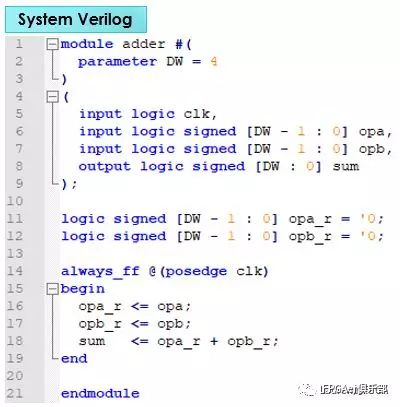

对于32-bit有符号加法运算,其逻辑级数为6,如下图所示。

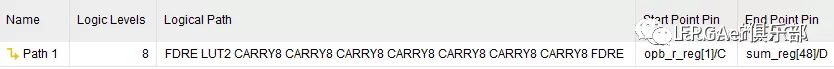

对于48-bit有符号加法运算,其逻辑级数为8,如下图所示。

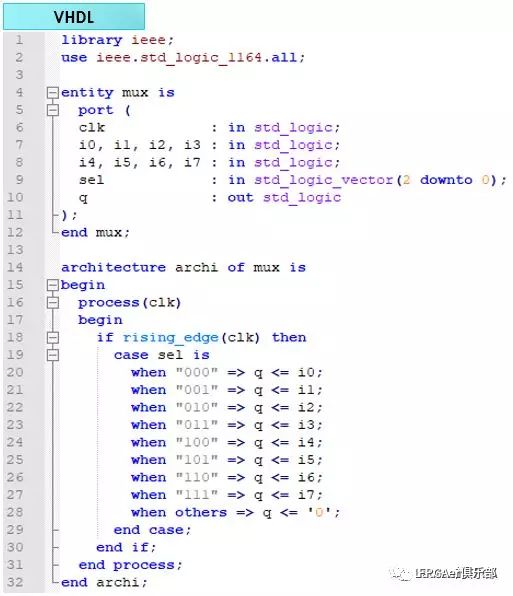

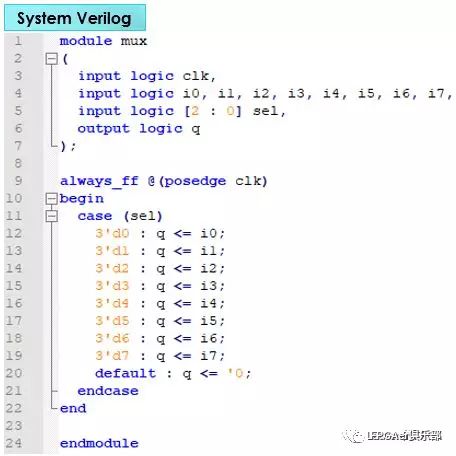

此外,1个LUT6可以实现4选1的数据选择器(MUX),同时LUT6可以与SLICE中的F7MUX、F8MUX、F9MUX等一起构成更大MUX。对于8选1的MUX,相应的RTL代码如下图所示,其逻辑级数为2(1个LUT+1个F7MUX);对于16选1的MUX,其逻辑级数为3(1个LUT+1个F7MUX+1个F8MUX);而32选1的MUX可在一个SLICE(针对UltraScale和UltraScale Plus芯片)中实现,消耗8个LUT6,4个F7MUX,2个F8MUX和1个F9MUX,因此,逻辑级数为4(1个LUT+1个F7MUX+1个F8MUX+1个F9MUX)。

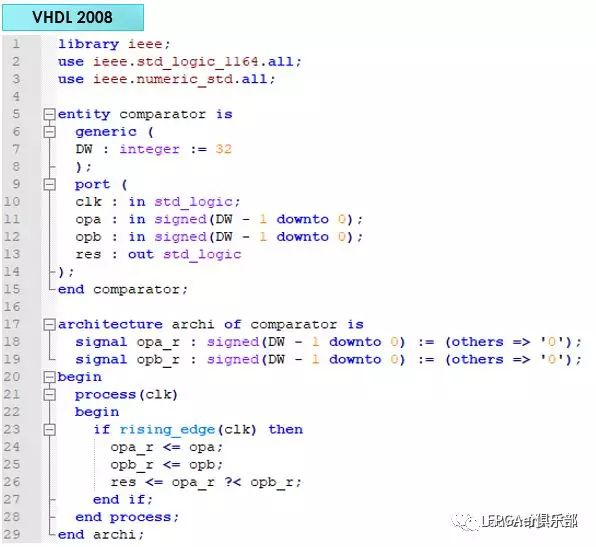

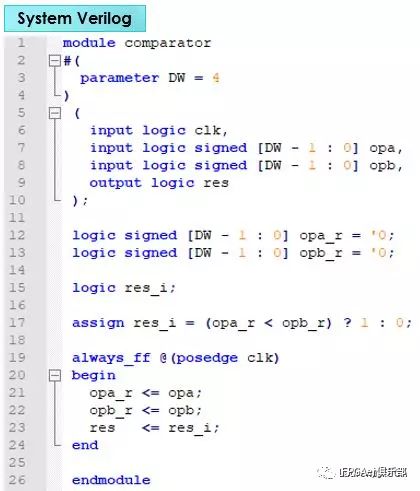

另一种常见运算是关系运算。相应的RTL代码如下图所示。当数据位宽为8-bit或16-bit时,对应的逻辑级数为2;当数据位宽为32-bit时,对应的逻辑级数为3。

结论:

本文转载自:http://xilinx.eetrend.com/news/12746,如涉及侵权,请私信小编删除。

============华 丽 的 分 割 线============

想加入我们FPGA学习交流群吗?可以长按或扫描以下二维码,审核通过后我们邀请您加入。

这些微信群旨在打造一个提供给FPGA工程开发人员及兴趣爱好者(统称“FPGAer”)进行技术交流、答疑解惑和学习的平台。而且我们也将会通过网络举办FPGA技术讲座,分享相关研究文献。

了解更多FPGA知识可以长按或扫描以下二维码关注“FPGAer俱乐部”。

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?