逻辑分析

包括

:

•

“

Netlist

”窗口

•

“

Hierarchy

”窗口

•

“

Schematic

”窗口

1、

“

Netlist

”窗口

“

Netlist

”

(

网表

)

窗口显示了网表中由综合工具所处理的设计层级。

根据综合设置

,

网表层级与原始

RTL

可能

100%

匹配

,

也可能不存在层级。通常

,

默认情况下综合在对逻辑进行最优 化时会保留大部分用户层级。由此将产生更小更快的网表。 通过使用综合工具默认设置,

即可识别网表层级

,

但层级接口也可供修改。层级中可能缺少部分管脚和层次。 网表层级以文件夹树的形式展现。在每一层中,

工具将显示如下内容

:

• 该层次存在的任意信号线的“

Nets

”文件夹

• “

Leaf Cells

”文件夹

,

前提是该层次存在硬件原语实例

• 在该层次例化的任意层级的“

hierarchy

”文件夹 展开“hierarchy

”文件夹即可显示该层次的“

Nets

”、“

Leaf Cells

”和“

hierarchies

”。单元旁的图标可显示有关设 计状态的信息。 参考

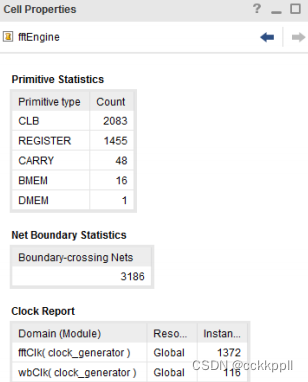

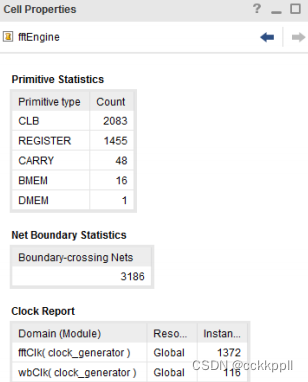

UG893

。选定“hierarchy

”的“

Cell Properties

”

(

单元属性

)

窗口可提供实用信息

,

可通过窗口底部的分类按钮来筛选所显示 的信息。选择“Statistics

”

(

统计数据

)

按钮可显示使用率统计数据

,

包括

:

• 整个层级分支的原语使用率

• 跨层级边界的信号线数量

• 每个时钟

,

包括该时钟是否位于全局布线上

,

以及该时钟在当前层级分支中的负载

2、

“

Hierarchy

”窗口

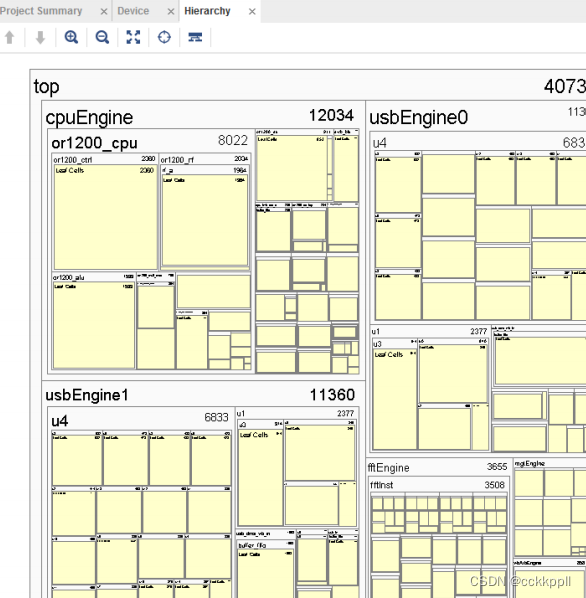

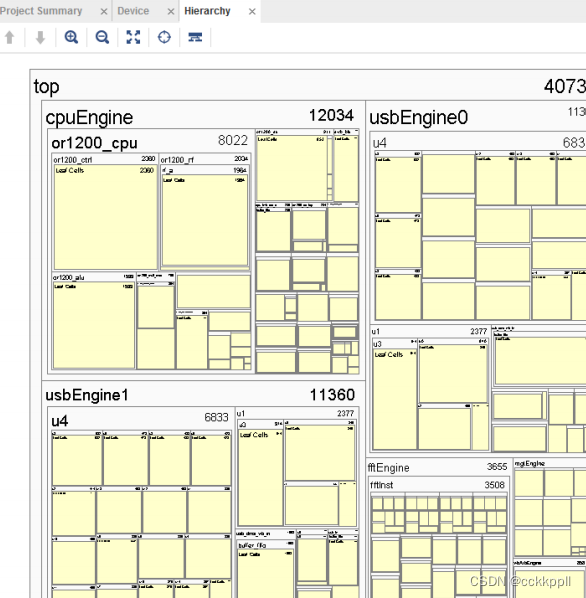

此窗口用于以物理方式浏览层级以了解资源使用率。

“

Tools > Show Hierarchy”

(

工具

>

显示层级

)

。 “Hierarchy

”窗口中显示了选定层级的层级映射。层级映射将叶节点单元显示为黄色块

,

并嵌套在对应 其父层级的矩形中。层级中每个层次的大小均根据该层次上的实例数量与设计中实例总数的占比关系来设置。

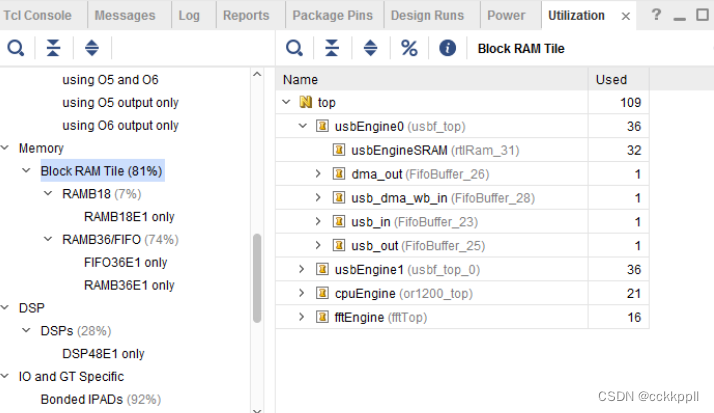

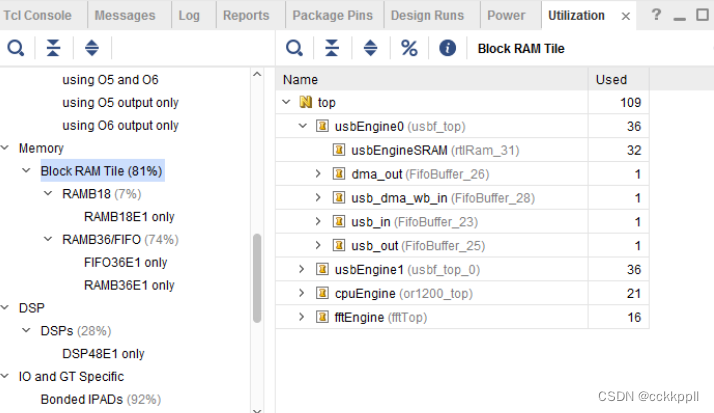

3、

“

Utilization

”报告

“

Utilization Report

”

(

使用率报告

)

可根据资源类型细分设计使用率。左侧面板提供按资源类型汇总的使用率

,

右侧 面板按层级显示使用率。 “Reports

” → “

Report Utilization

”

(

报告

>

使用率报告

)。

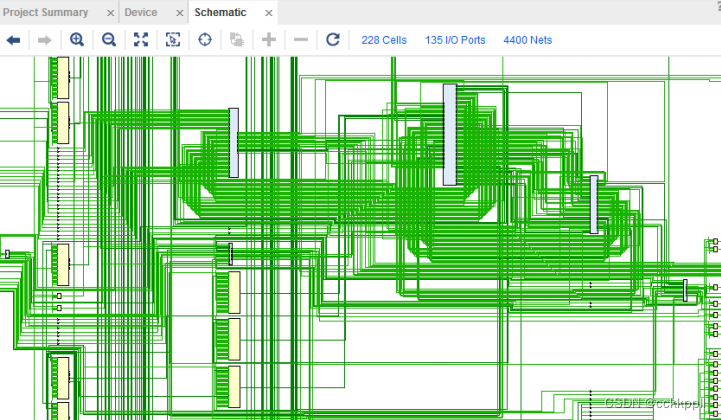

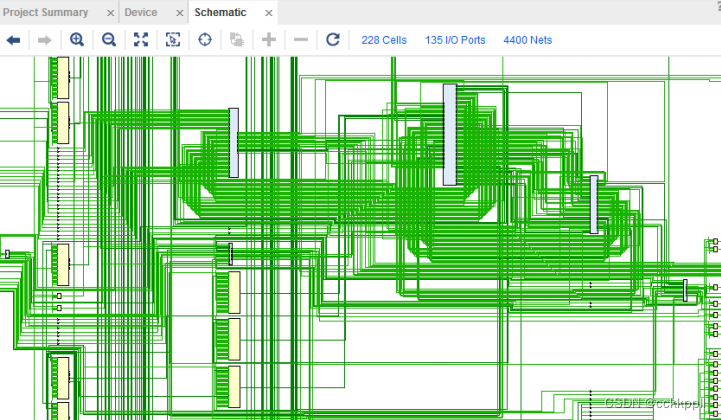

4、

“

Schematic

”窗口

“

Schematic

”

(

板级原理图

)

是网表的一种图形化表示法。通过查看板级原理图即可

:

• 查看网表的图形化表示。

• 检查门电路、层级以及连接。

• 追踪并扩展逻辑椎。

• 分析设计。

• 更准确了解设计内部发生的状况。

在“

Elaborated Design

”

(

细化设计

)

中的

RTL

层级上可查看工具对代码的解释。在“

Synthesize Design

”

(

综合设 计)

和“

Implemented Design

”

(

实现设计

)

中

,

可查看由综合工具生成的门电路。“Tools > Schematic

”

(

工具

>

板级原理图

)

。如果不选择任何项

,

门电路、层级和连接会显示在设计顶层。

本文介绍了逻辑设计中的三个关键窗口:Netlist展示设计层级的网表,Hierarchy用于物理资源查看,Schematic提供图形化表示。此外,还提到Utilization报告对设计资源使用的详细分析。

本文介绍了逻辑设计中的三个关键窗口:Netlist展示设计层级的网表,Hierarchy用于物理资源查看,Schematic提供图形化表示。此外,还提到Utilization报告对设计资源使用的详细分析。

2235

2235

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?