前言

verilog (硬件描述语言)是FPGA主要开发语言。良好的代码规范是与人合作、交流等必备的前提。博主阅读相关文献整理一份基础的verilog代码规范(暂时仅限可综合部分,不包含仿真)。

一、通用代码结构

1.1 头文件

设计verilog的第一步就是文件头,其中包含作者、创建日期、摘要以及详细介绍修改历史记录与日期和作者一起做了哪些更改以及版权标题,位于每个文件标题的顶部,头文件格式实例:

//////////////////////////////////////////////////////////////////////////////////

//Company:

//Engineer: DaMi

//Create Date: 11:14 09/22/2019

//Design Name:

//Module Name: AD9226

//Project Name: DFBDriverV2.0

//Target Devices: XC6LX9-TQG144

//Tool versions: ISE14.6

//Description:

// 1 . this file is ADC AD9226 interface;

//Dependencies:

//

//Revision:

// Revision 0.01 – File Created

//Additional Comments:

// (C)COPYRIGHT 2020 xxxxx. ALL RIGHT RESERVED

///////////

///////////////////////////////////////////////////////////////////////

1.2 命名规则

对于命名一般做的见名知意,文字较长可以使用相应的缩写。不同的地方命名还有些许差别。

-

文件命名

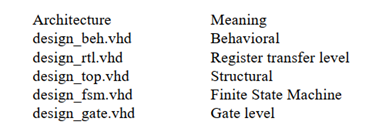

- 针对文件命名时,将后缀添加到文件名中,标识该模块的结构。文件命名示如下。虽然文件后缀为vhd,verilog命名规则相同。

而对于包含公共函数、任务和常量。命名这些文件的约定如下所示。标题文件内容在更多中描述本文档稍后将详细介绍。

- 针对文件命名时,将后缀添加到文件名中,标识该模块的结构。文件命名示如下。虽然文件后缀为vhd,verilog命名规则相同。

-

变量命名

- 对所有信号名、变量名和端口名使用小写字母。

- 对宏和用户定义类型的名称使用大写字母。

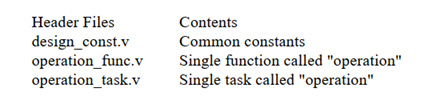

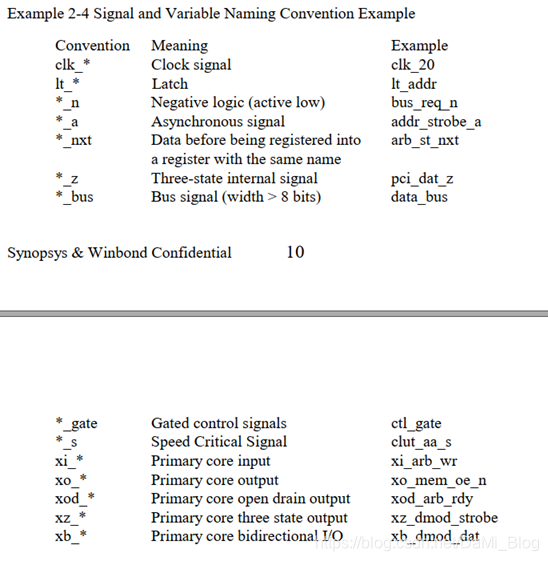

- 对信号、端口、函数和参数使用有意义的名称。例如,不要将ra用于RAM地址总线。相反,使用ram_addr。如果设计使用多个参数,请使用简短但描述性的名称。 时钟信号的名称前缀clk。如果设计中有一个以上的时钟,使用clk作为所有时钟信号(例如,clk1、clk2或clk_接口)的前缀。

- 对从同一个源驱动的所有时钟信号使用相同的名称。

- 对于低有效信号,用下划线结束信号名称,后跟小写字符(例如,b或n)。使用相同的小写字符表示整个设计中都有低信号。标准化指南,我们建议您使用n来表示低信号。但是,只要使用小写字符,就可以接受一贯地。

- 使用复位信号rst。如果复位信号为低激活状态,则使用rst(或用表示活动低位的小写字符替换n信号)。

- 多位端口或信号(0:x)。而是始终使用(x:0)。如果可能,请为端口和信号使用相同或相似的名称连(.a(a),.a(a)in Verilog)。

常用的名词前缀如下图:

-

注释

在编写代码时注释代码,提高代码的可读性、可维护性、易性重用、易于审阅和可追溯到规范。注释用英文,一段功能性代码注释可以插入式,单句可以在该句后面进行注释。

二、逻辑结构

2.1 latch综合

在进行条件语句时,状态没有完全描述,则会综合出latch(latch的特性,请自行百度)。因此if、case等语句时,注意:

if条件之后,跟else语句,对相关寄存器进行赋值;

case语句,最好加上default语句进行幅值;

2.2 有限状态机

有限状态机设计时,至少将时序逻辑和组合逻辑分离,即使用两个独立的always块。还需要将控制流和数据流逻辑分开。不需要隔离分层分区。根据通过将硬件功能分解为独立的进程或并发。此代码片段是单进程状态机。它并没有把序列和组合分开,所以所有分配给进程的信号或变量都被注册。它没有将控制流与数据流隔离,这样状态逻辑(state)和数据输出(y,count)全部合并成一个大型控件或数据流图。

总结

本文简单总结了Verilog基本的代码风格。主要也是针对FPGA开发,涉及ASIC的相关并未细致区分。博主也是阅读了相关的文档之后进行简单总结,更细致的内容请看相关文档。博主参考的文档部分链接会在贴在附近内。

参考文献

synopsys —《RTL Coding Style Gold Book_Coding_Guidelines》

Freescale —《Verilog Code style-Freescale》

Verilog 代码规范与最佳实践

Verilog 代码规范与最佳实践

本文介绍了Verilog(硬件描述语言)的代码规范,适用于FPGA开发。内容涵盖通用代码结构,如头文件和命名规则,以及逻辑结构,包括避免latch综合和有限状态机的设计原则。强调了良好的代码风格对于可读性和可维护性的重要性。

本文介绍了Verilog(硬件描述语言)的代码规范,适用于FPGA开发。内容涵盖通用代码结构,如头文件和命名规则,以及逻辑结构,包括避免latch综合和有限状态机的设计原则。强调了良好的代码风格对于可读性和可维护性的重要性。

342

342

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?