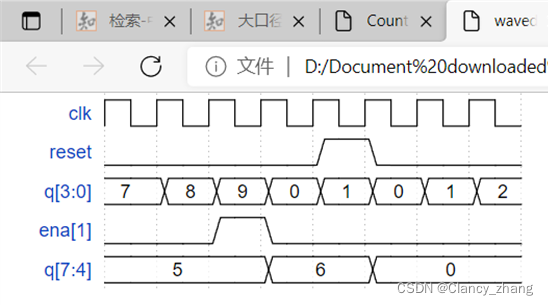

QUESTION:Build a 4-digit BCD (binary-coded decimal) counter. Each decimal digit is encoded using 4 bits: q[3:0] is the ones digit, q[7:4] is the tens digit, etc. For digits [3:1], also output an enable signal indicating when each of the upper three digits should be incremented.

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output [15:0] q);

bitc_module bitc_module_inst1(clk,reset,'b1,q[3:0]);

bitc_module bitc_module_inst2(clk,reset,ena[1],q[7:4]);

bitc_module bitc_module_inst3(clk,reset,ena[2],q[11:8]);

bitc_module bitc_module_inst4(clk,reset,ena[3],q[15:12]);

assign ena={q[7:4]==4'd9&&q[3:0]==4'd9&&q[11:8]==4'd9,q[7:4]==4'd9&&q[3:0]==4'd9,q[3:0]==4'd9};

endmodule

module bitc_module (

input clk,

input reset, // Synchronous active-high reset

input ena,

output [3:0] q);

always@(posedge clk)begin

if(reset==1)

q<='d0;

else

if (ena)

begin

if(q == 4'd9)

q <= 4'd0;

else

q <= q + 1'b1;

end

end

endmodule

本文介绍了一种4位二进制编码十进制(BCD)计数器的设计方案,每个十进制位使用4位进行编码。通过模块化的方法实现了一位到四位的BCD计数,并输出了使能信号来指示何时应该递增高三位。

本文介绍了一种4位二进制编码十进制(BCD)计数器的设计方案,每个十进制位使用4位进行编码。通过模块化的方法实现了一位到四位的BCD计数,并输出了使能信号来指示何时应该递增高三位。

802

802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?