接上篇博客,继续流程!

3、板上验证

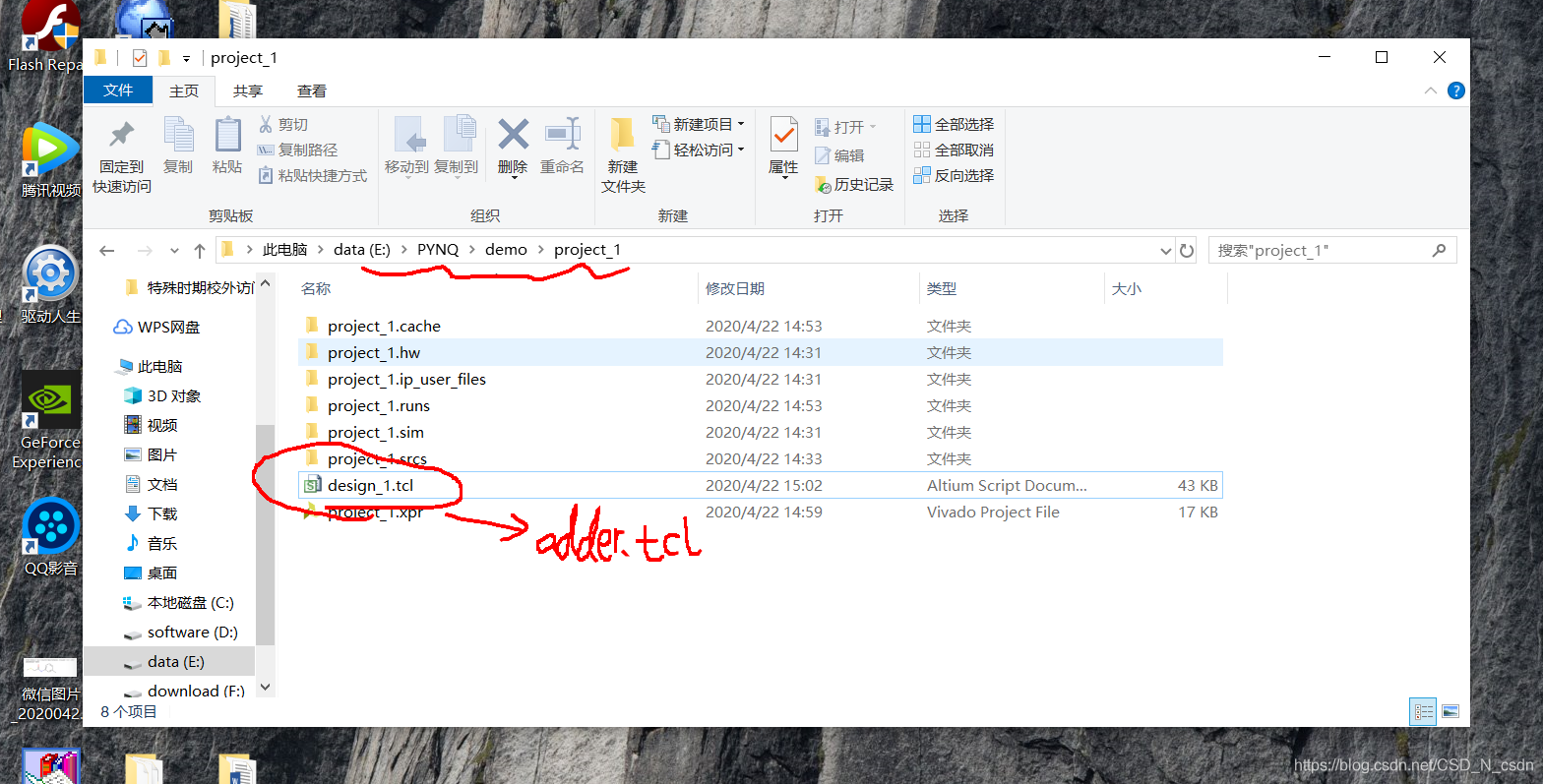

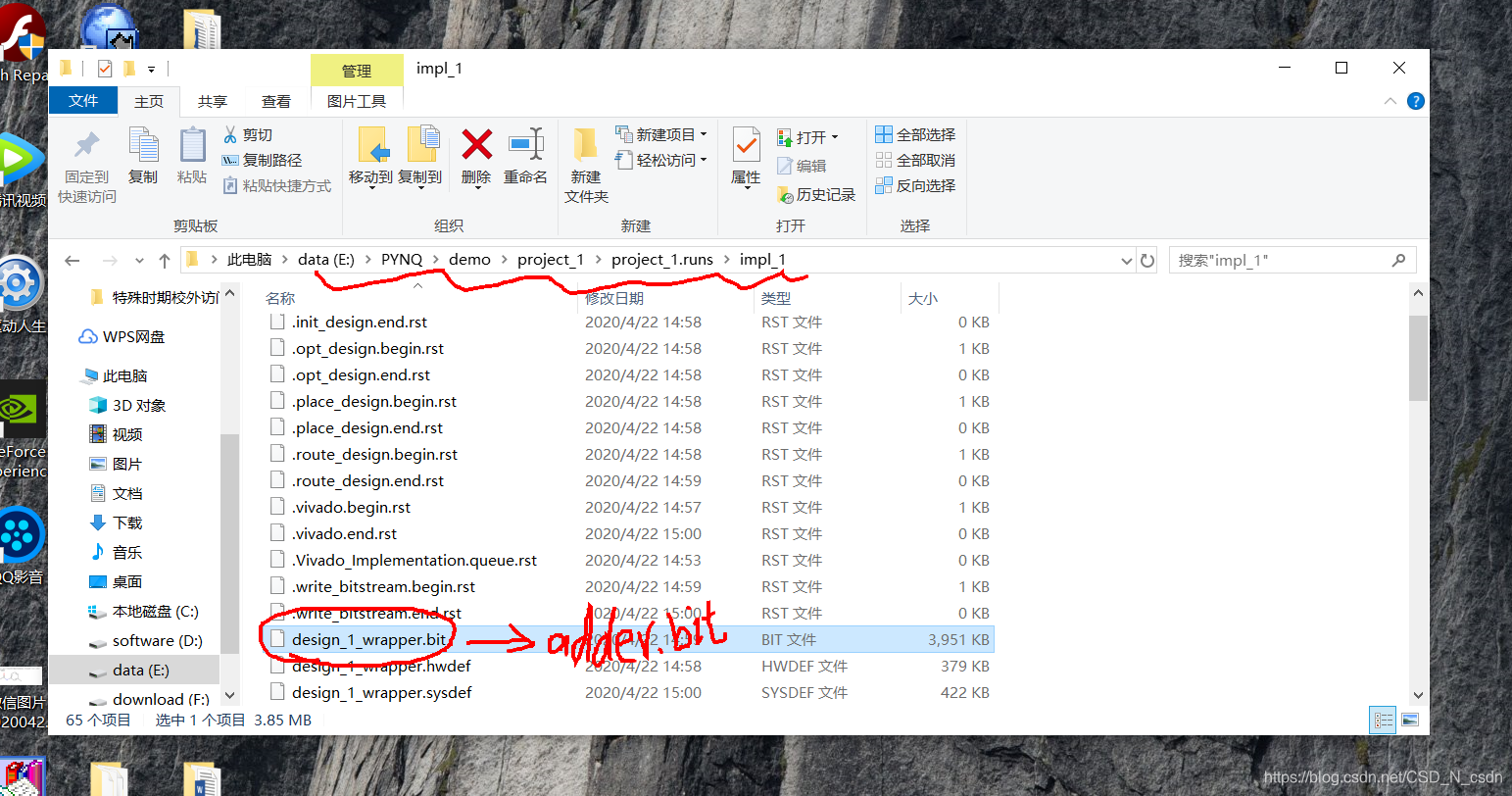

打开Vivado软件生成的工程的,找到Tcl文件,找到bit文件,统一修改名字为adder,后缀文件类型不改,并放在一起。如下:

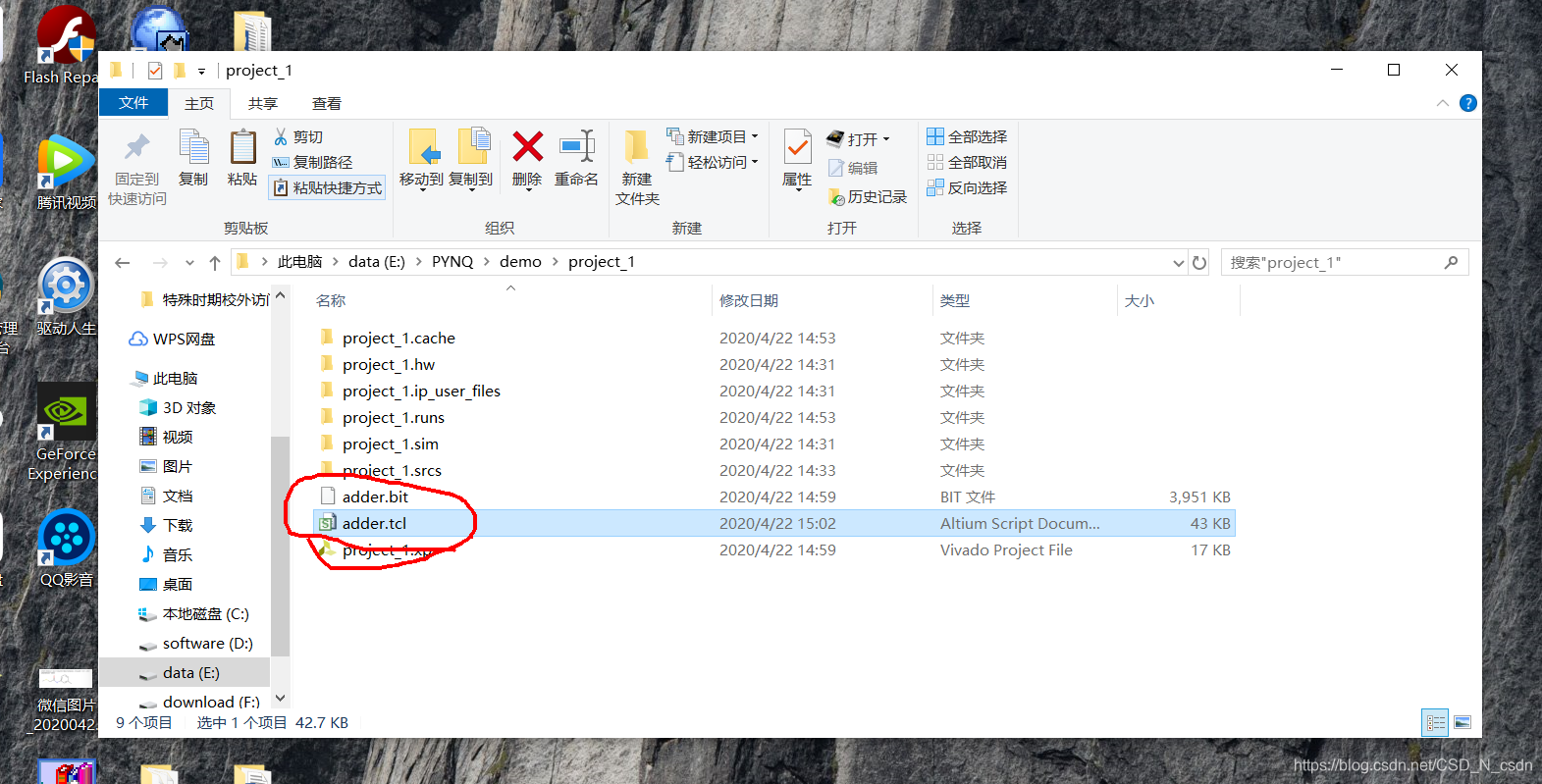

修改后如下:

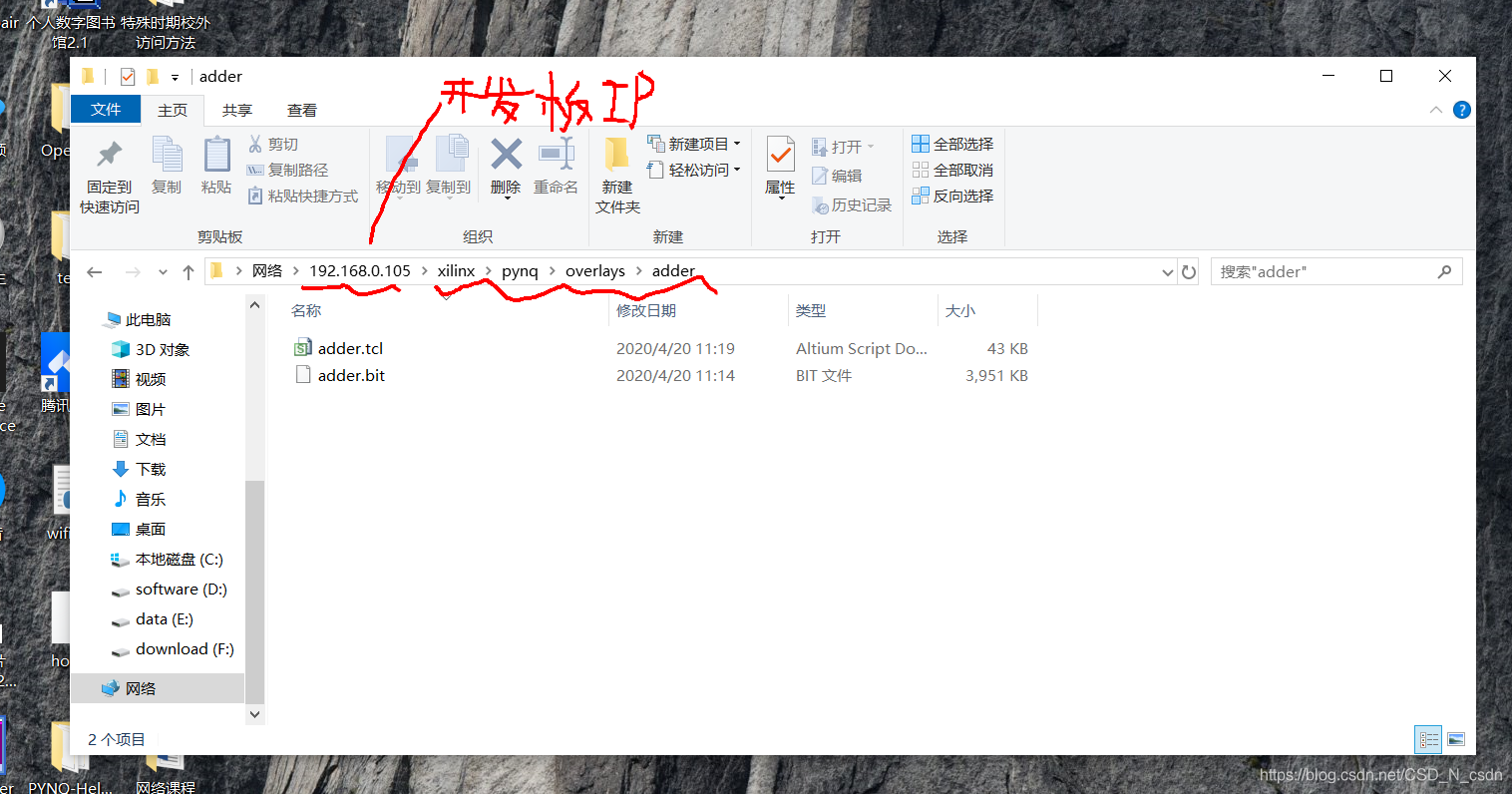

下面进行板级验证,通过电脑与开发板的共享文件夹,打开xilinx/pynq/overlays文件夹,如图新建一个adder文件夹,两个文件存放在此文件夹下。

准备就绪,开始验证。浏览器打开jupyter-notebook,新建Python3文件,改名为demo,在cell中输入如下代码(此代码及以下代码可在上篇的官方手册中找到):

from pynq import Overlay

overlay = Overlay('/home/xilinx/pynq/overlays/adder/adder.bit')#即bit文件所在位置点击Run,效果如下,warn

本文详细介绍了在ZYNQ FPGA上使用Vivado和PYNQ验证自定义加法器IP核的过程,包括生成工程、修改文件名、板级验证、创建驱动等步骤,并提供了代码示例。

本文详细介绍了在ZYNQ FPGA上使用Vivado和PYNQ验证自定义加法器IP核的过程,包括生成工程、修改文件名、板级验证、创建驱动等步骤,并提供了代码示例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3199

3199

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?