介绍

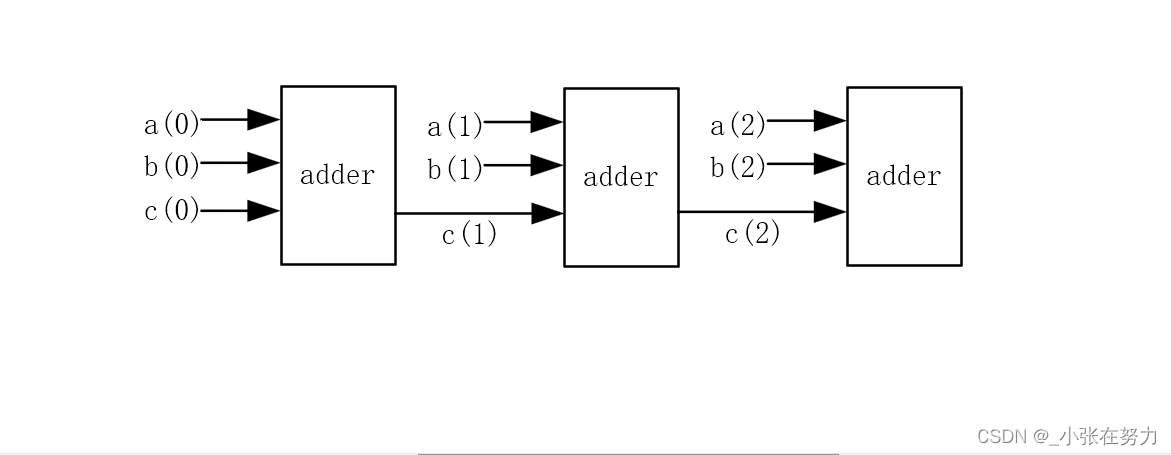

逐级进位加法器就是将上一位的输出作为下一位的进位输入,依次这样相加。下面以一个8位逐级进位加法器给大家展示。

我增加了电路结构,应该很容易理解吧。

下面我也列举了一位加法器,可以看下。

电路结构

设计文件

1位加法器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity adder1 is

port (a,b,cin : in std_logic;

sum,s : out std_logic);

end adder1;

--architecture

architecture adder1 of adder1 is

begin

sum <= a xor b xor cin;

s <= (a and b) or (a and cin) or (b and cin);

end adder1;

8位逐级进位加法器

library ieee;

use ieee.std_logic_1164.all;

entity adder2 is

generic (length : integer := 8);

port (a,b : in std_logic_vector(length-1 downto 0);

cin : in std_l

本文详细介绍了1位和8位逐级进位加法器的电路结构,包括基本逻辑门的使用和std_logic_1164库的应用,以及给出了测试文件和仿真结果。读者可以了解数字逻辑设计中的进位加法过程。

本文详细介绍了1位和8位逐级进位加法器的电路结构,包括基本逻辑门的使用和std_logic_1164库的应用,以及给出了测试文件和仿真结果。读者可以了解数字逻辑设计中的进位加法过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?