目的:采用有限状态机设计序列检测器,实现串行序列11010的检测器。

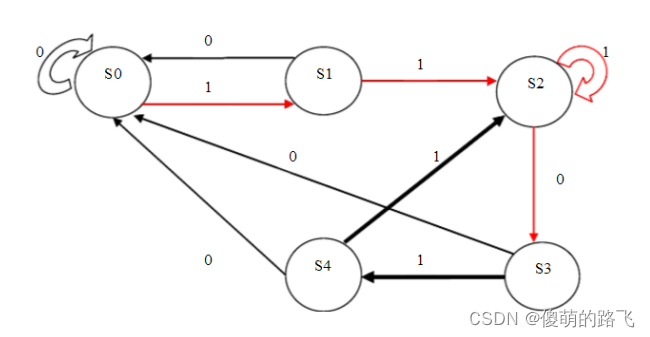

设计思想:使用有限状态机,定义五个状态即s0,s1,s2,s3,s4,实现序列11010的检测。在状态机中,每个状态的下一个状态都有两个转移方向,画出状态转移图,如下。

程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity state is

port(

clk,clr :in std_logic; --clk时钟脉冲,clr回到初始状态

input :in std_logic; --input序列信号输入

output :out std_logic --output序列检测输出

);

end state;

architecture behave of state is

type state_type is(st0,st1,st2,st3,st4); --定义状态位s0,s1,s2,s3,s4)

signal s :std_logic_vector(4 downto 0);

signal q :state_type;

signal flag :integer range 0 to 1; --标志位

begin

s <= "11010";

process(clk)

begin

if(clr = '1') then

flag <= 0;

q <= st0;

elsif (clk'event and clk = '1') then

case q is

when st0 => if(input = s(4)) then q <= st1;flag <= 1;else q <= st0;flag <= 0;end if;

when st1 => if(input = s(3)) then q <= st2;flag <= 1;else q <= st0;flag <= 0;end if;

when st2 => if(input = s(2)) then q <= st3;flag <= 1;else q <= st2;flag <= 0;end if;

when st3 => if(input = s(1)) then q <= st4;flag <= 1;else q <= st0;flag <= 0;end if;

when st4 => if(input = s(0)) then q <= st0;flag <= 1;else q <= st2;flag <= 0;end if;

when others => q <= st0;flag <= 0;

end case;

end if;

end process;

process(q,flag)

begin

if(q = st0 and flag = 1) then

output <= '1';

else

output <= '0';

end if;

end process;

end behave;

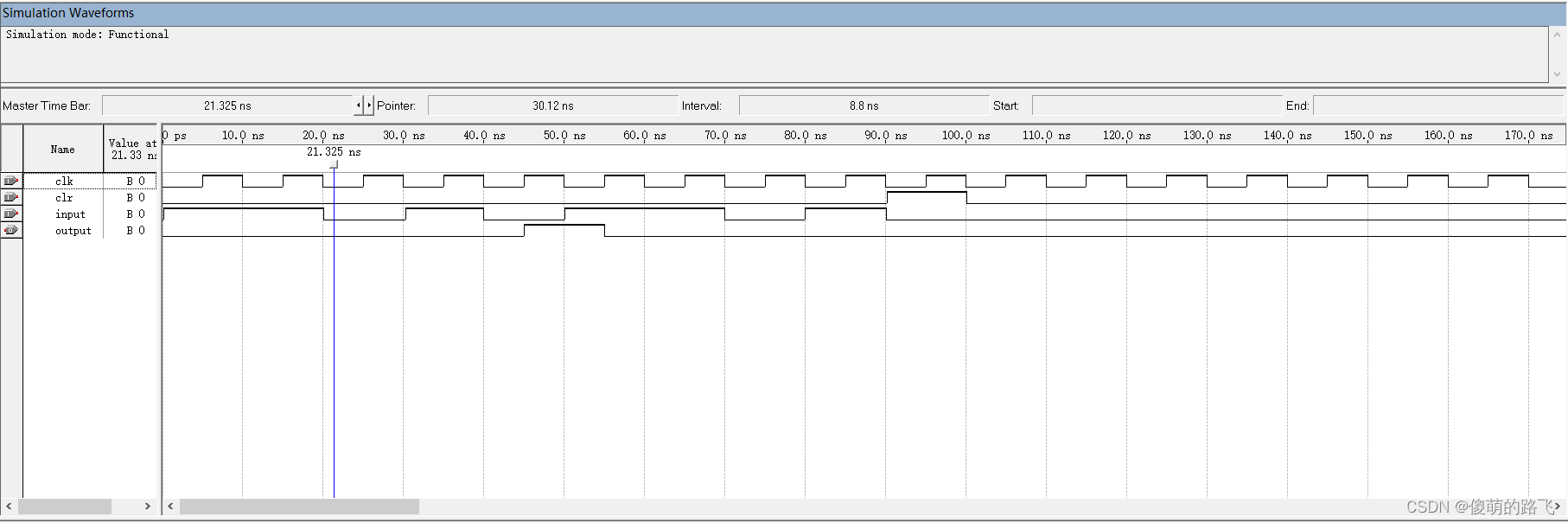

波形仿真图

本文介绍了如何使用VHDL设计一个序列检测器,专注于检测11010的串行序列。通过阐述有限状态机的概念,详细描述了五个状态s0到s4的转换,并提供了程序代码及波形仿真的结果。

本文介绍了如何使用VHDL设计一个序列检测器,专注于检测11010的串行序列。通过阐述有限状态机的概念,详细描述了五个状态s0到s4的转换,并提供了程序代码及波形仿真的结果。

1395

1395

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?