提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

时钟IP核实现的功能对输入的时钟进行时钟的倍频时钟的分频或者是调整相位等等。对于比较复杂的系统而言,单个时钟已经无法满足设计要求。

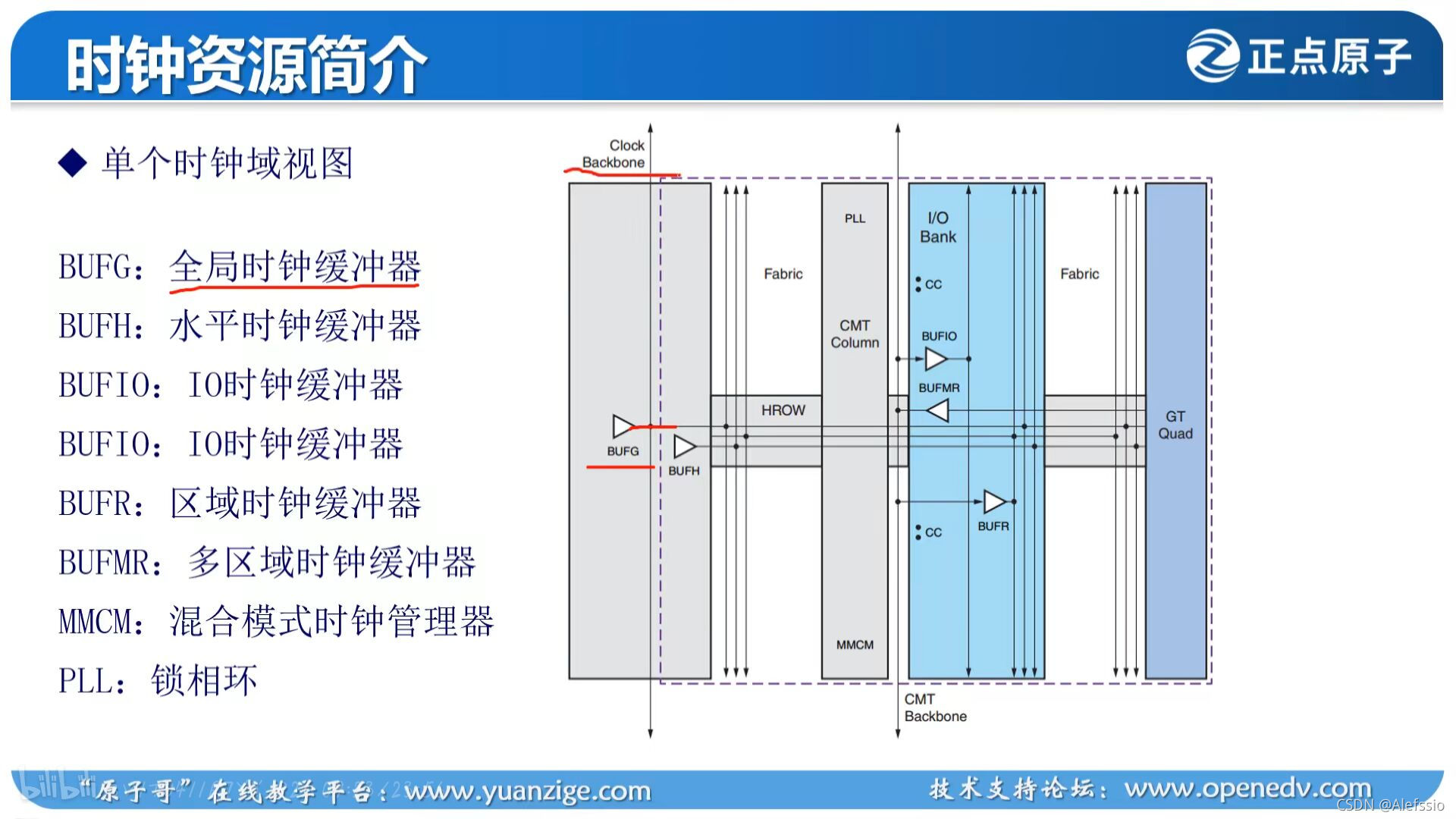

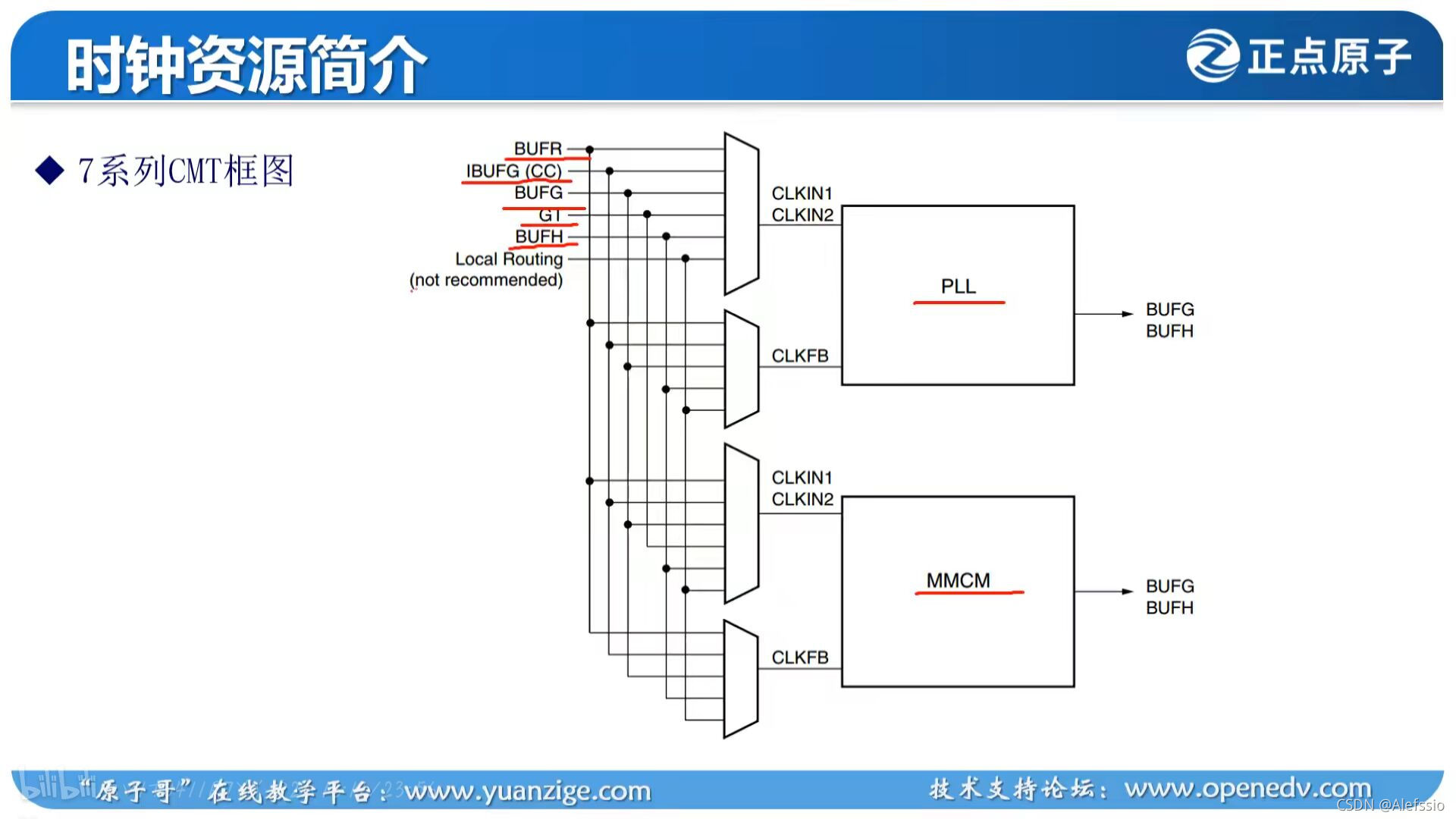

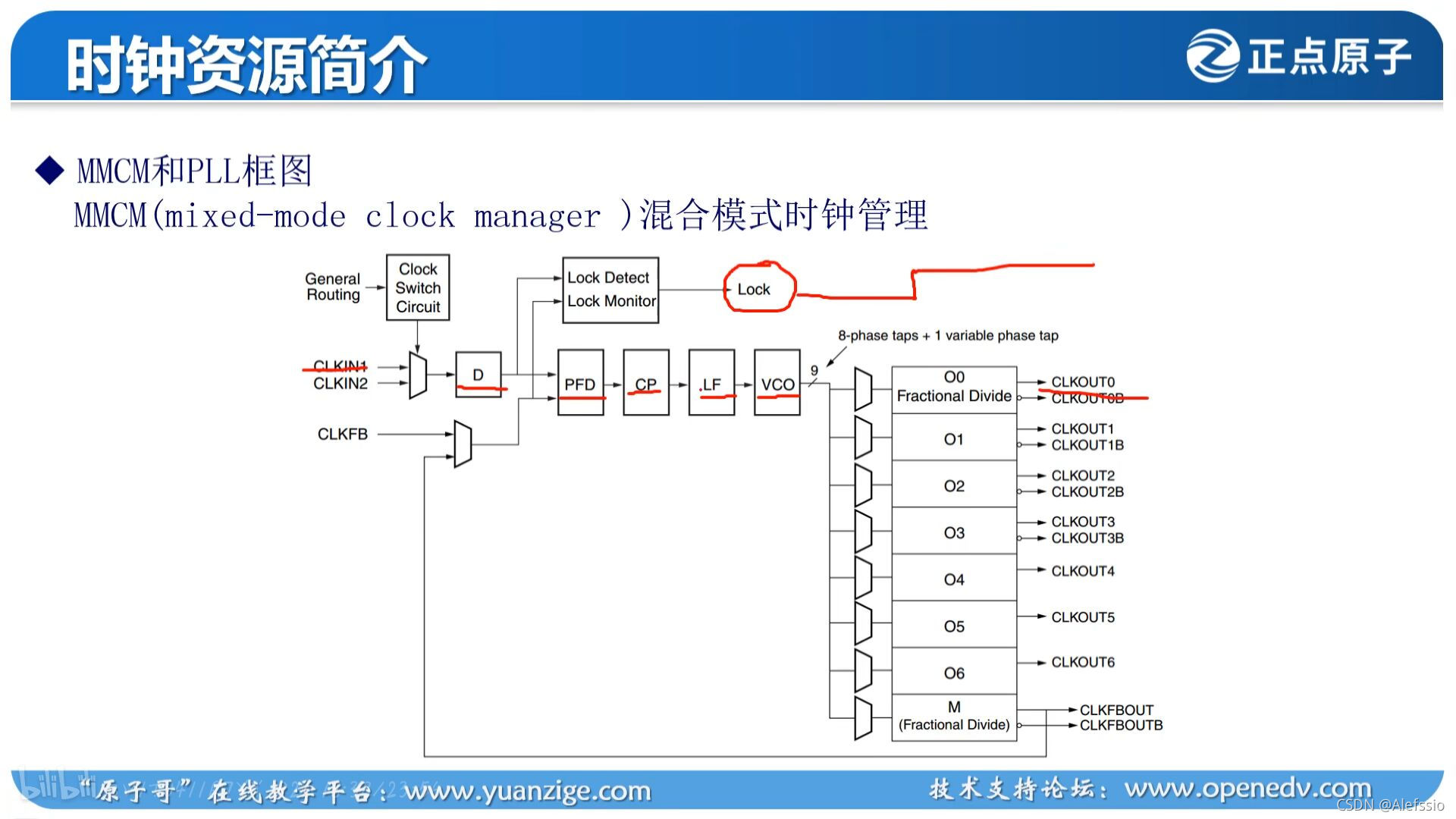

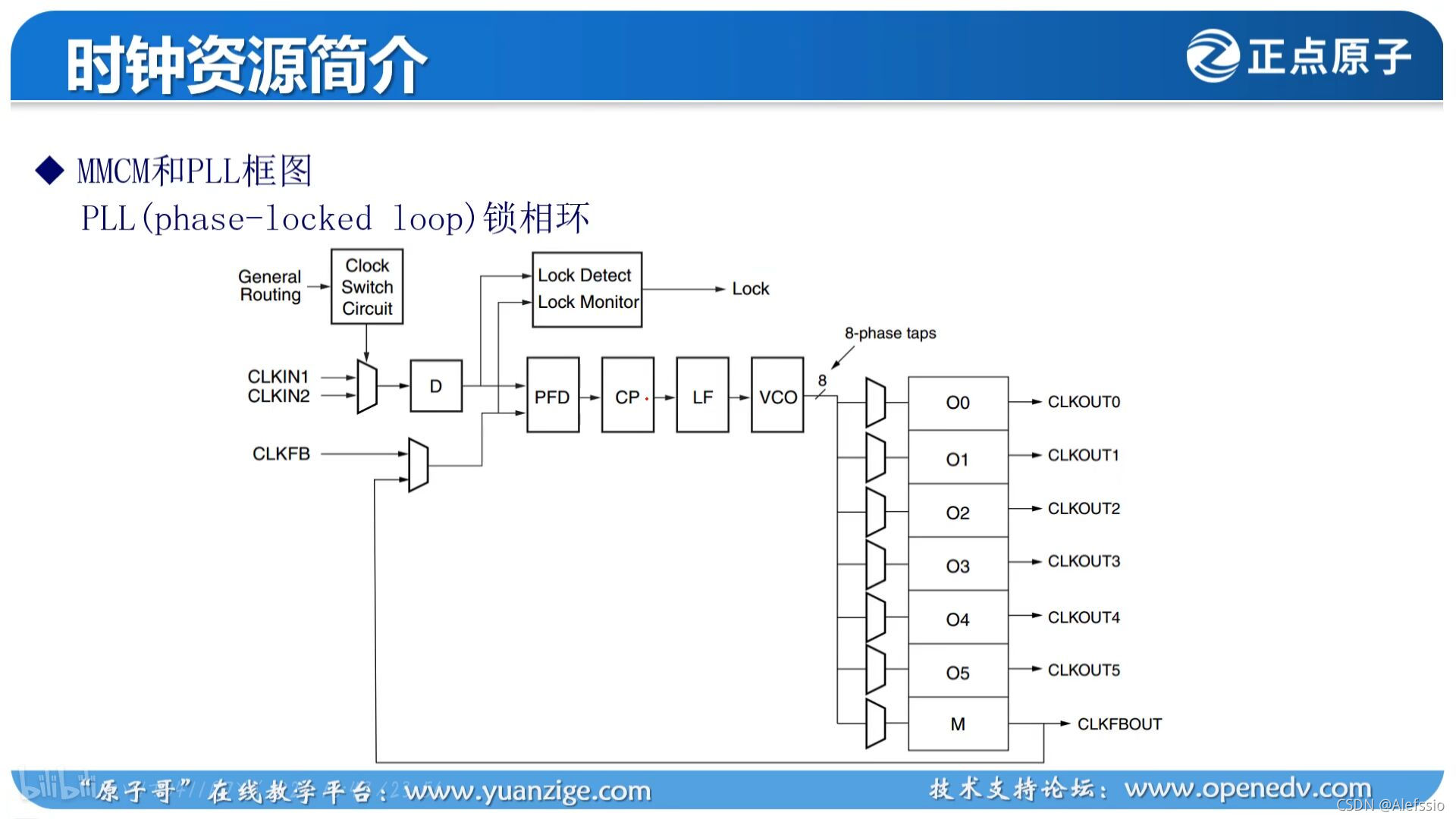

一、MMCM核PLL

- MMCM:混合模式时钟管理器

- PLL:锁相环

MMCM比PLL的功能更加强大

二、时钟IP核的使用

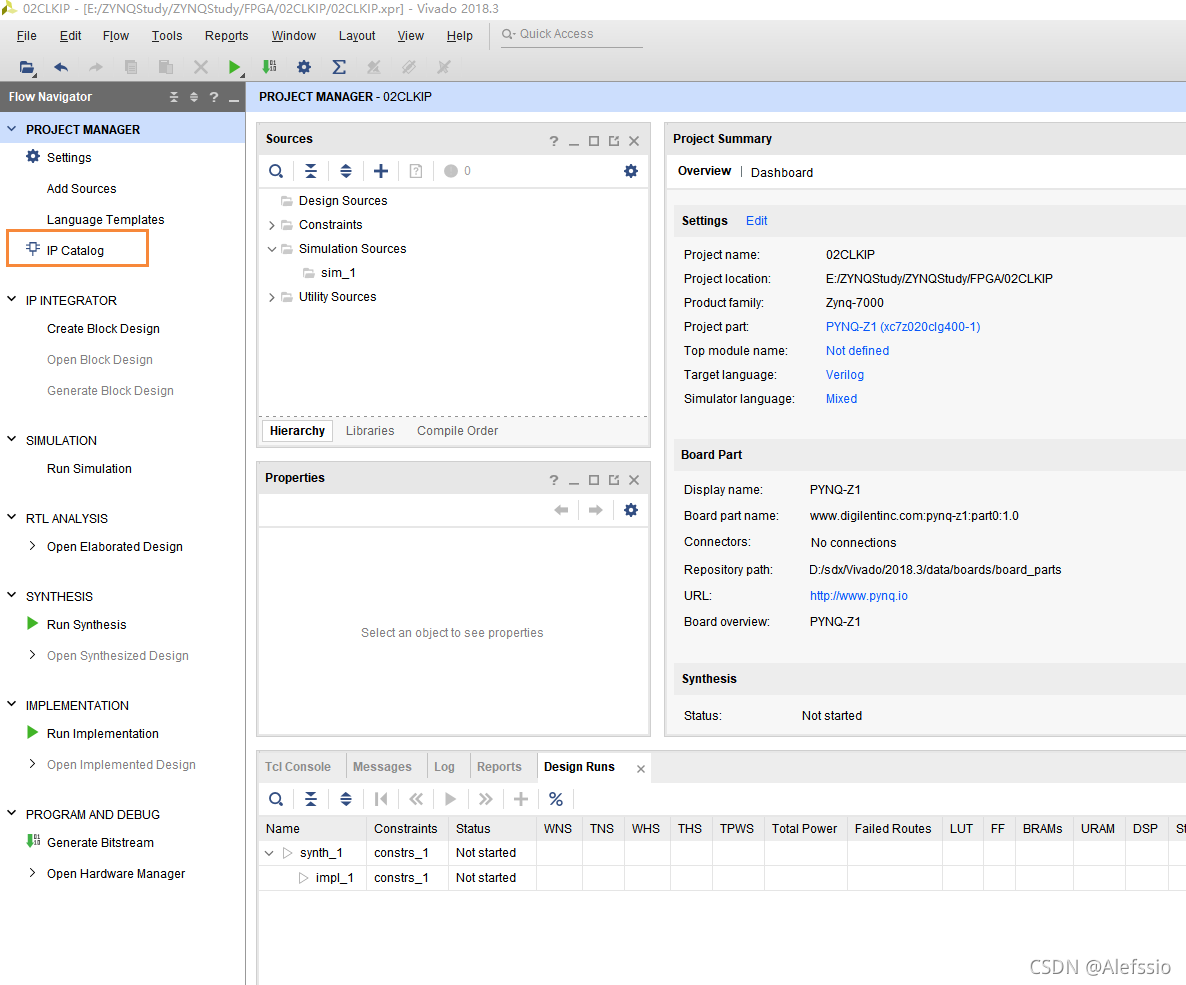

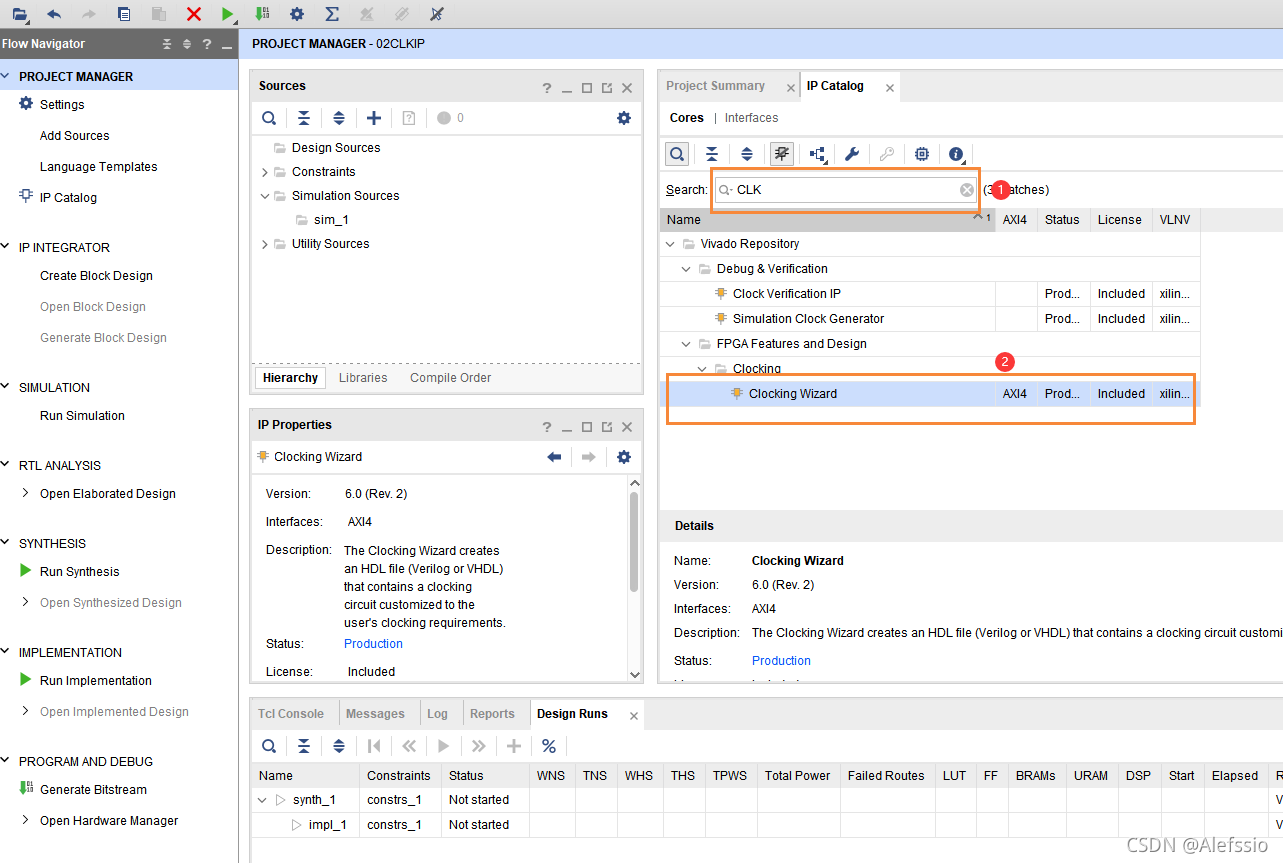

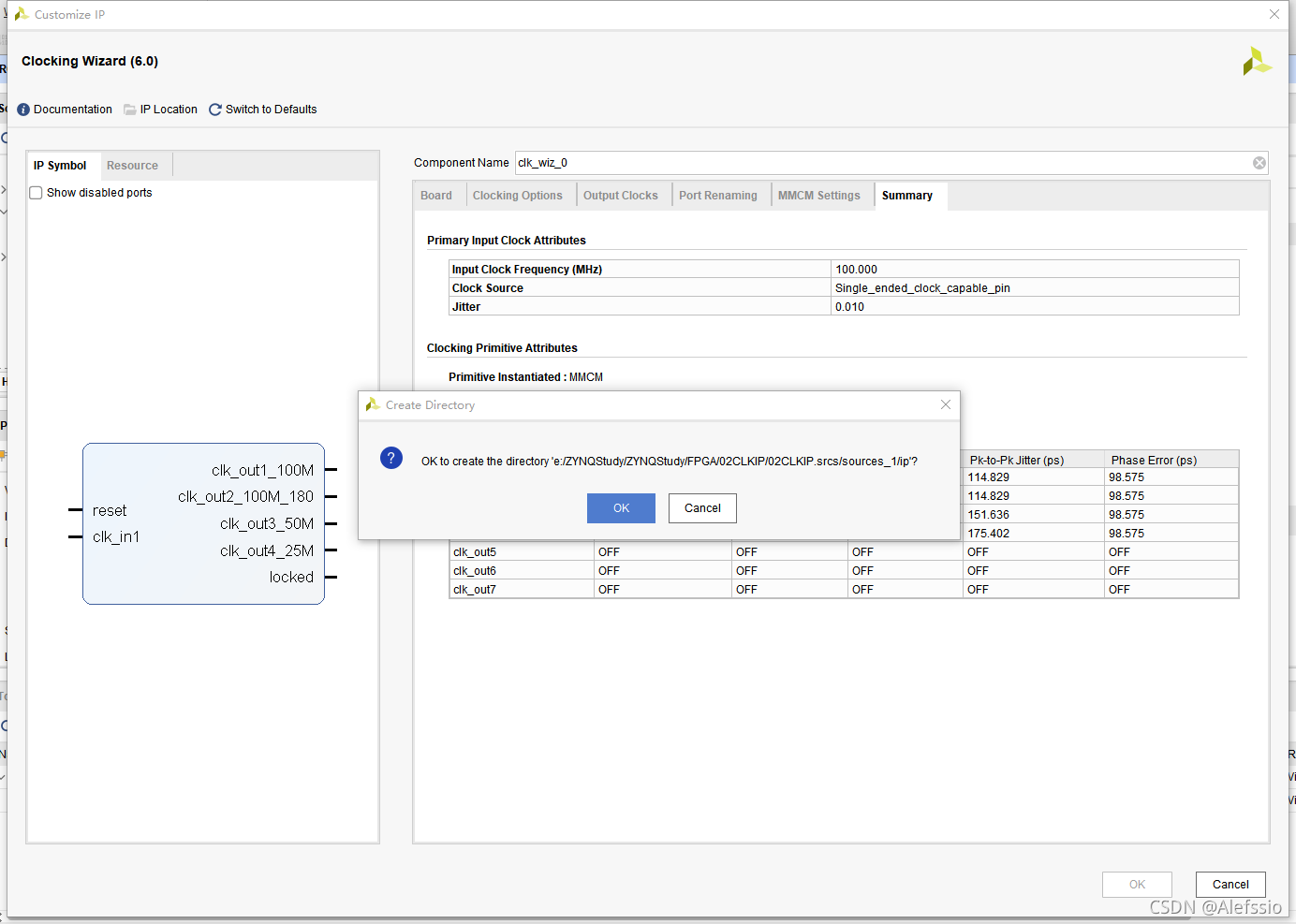

1.创建和设置IP核

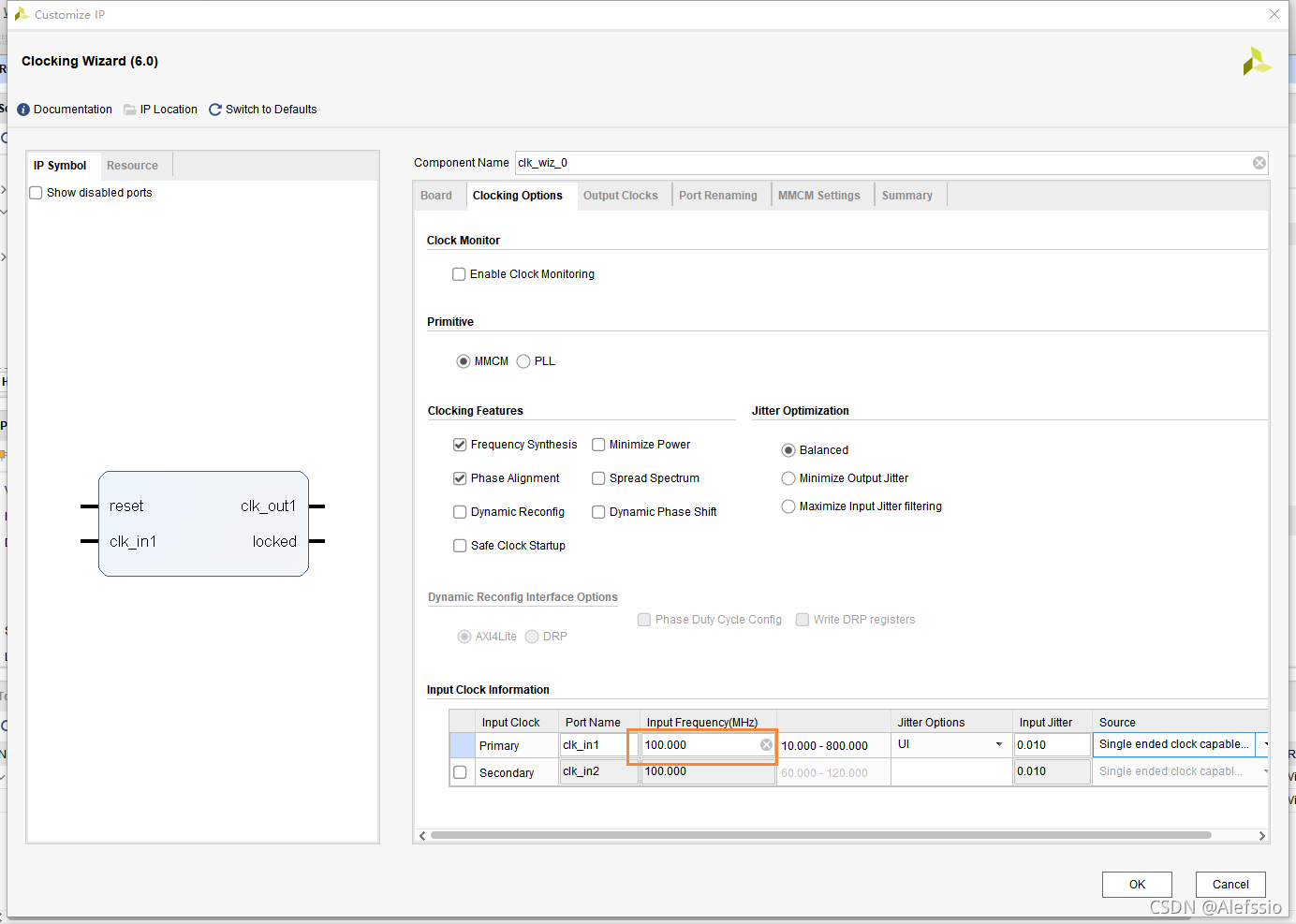

PYNQ本地时钟晶振为100HZ

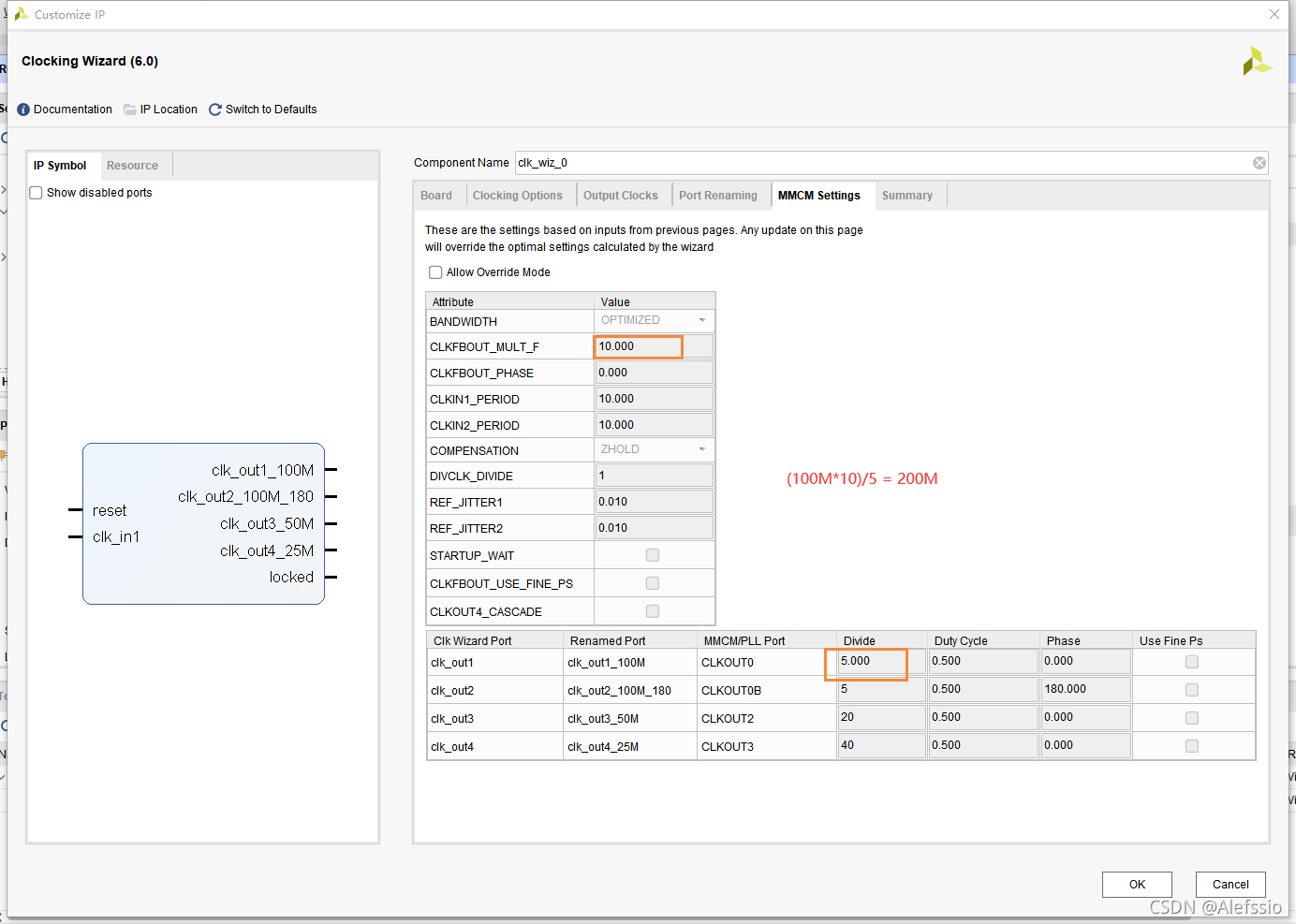

添加四路时钟信号输出

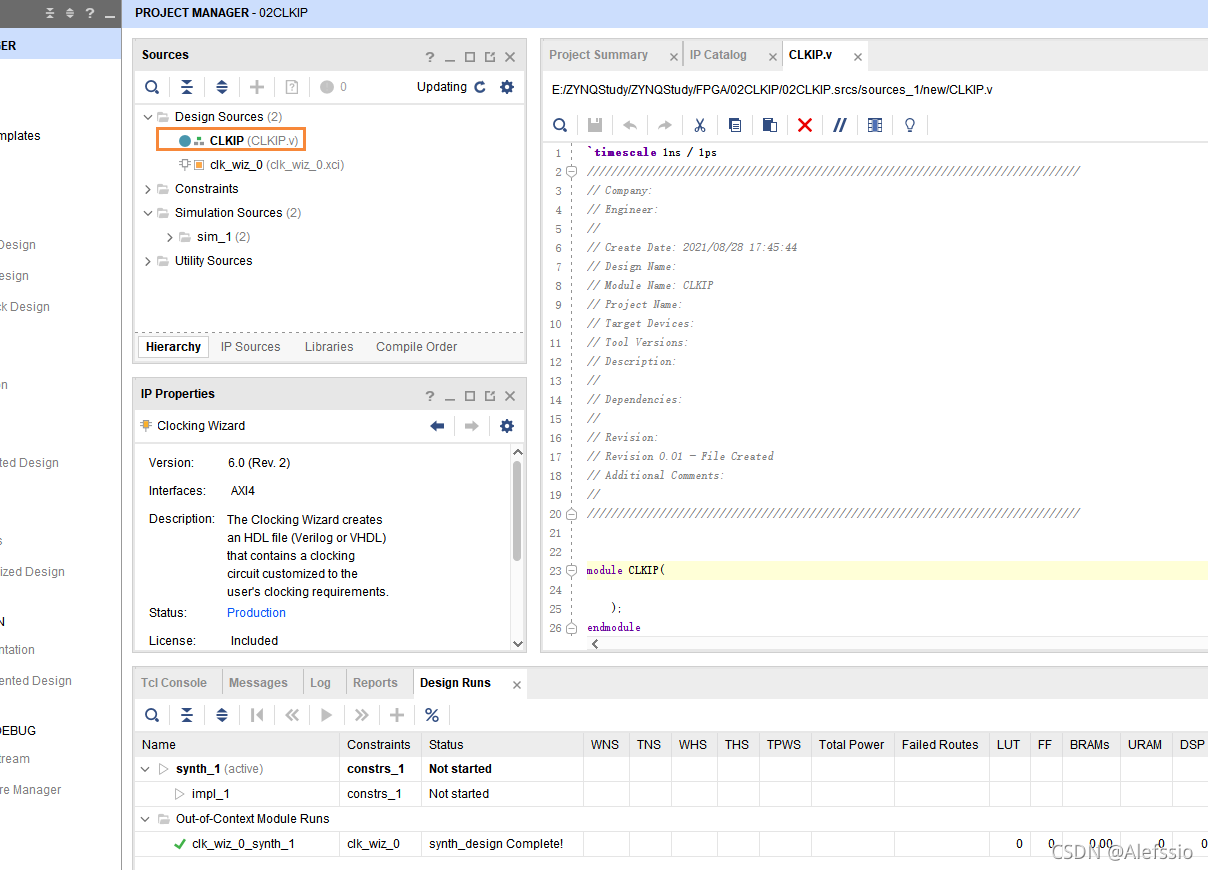

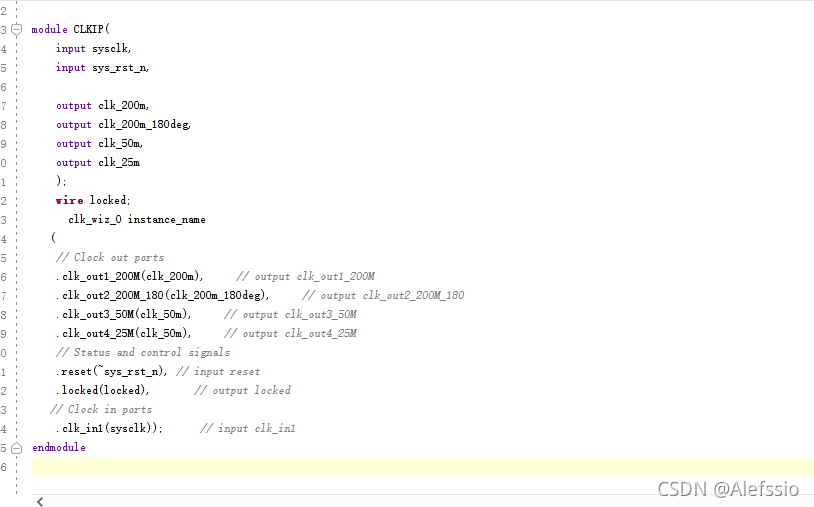

增加一个.v文件

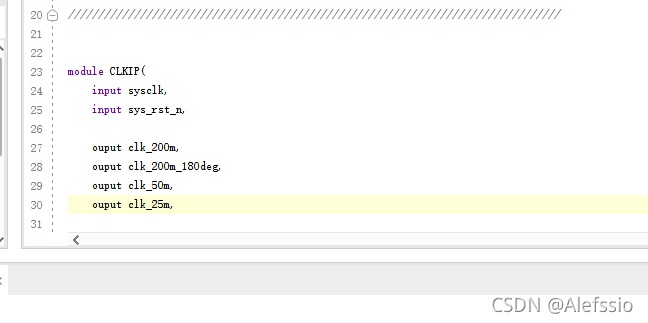

填写参数

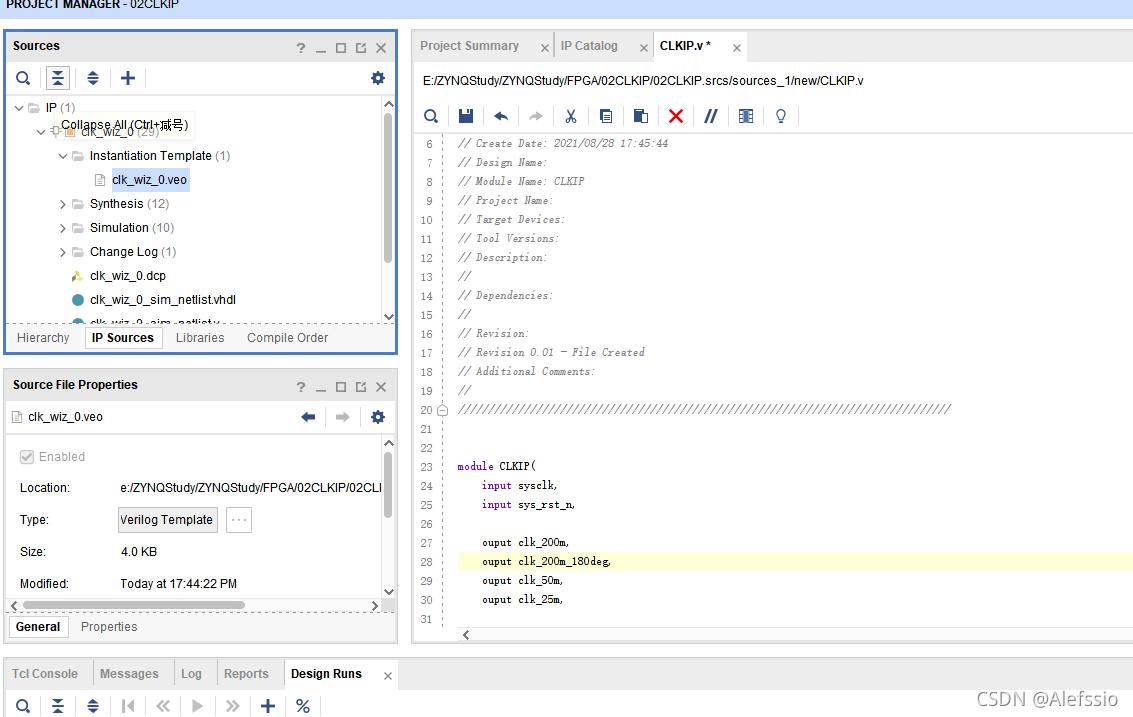

复制例化模版,例化ip核

2.检测数据

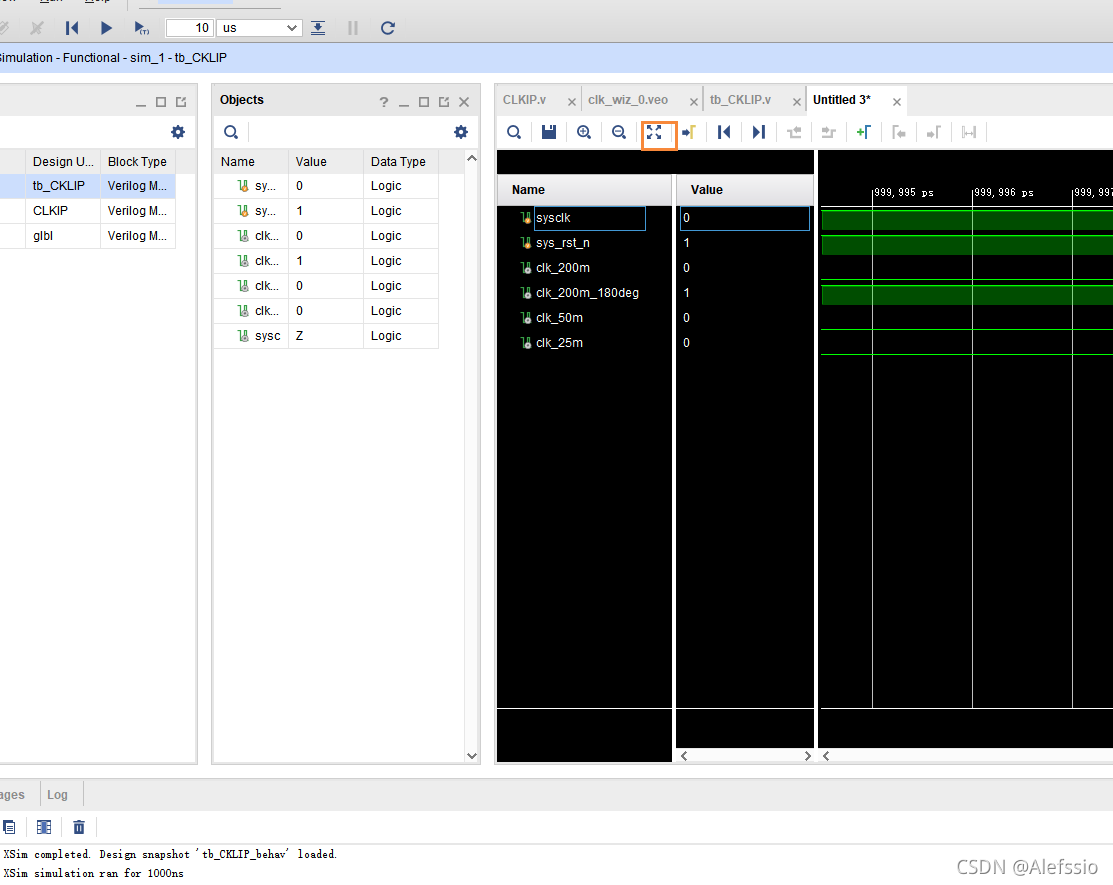

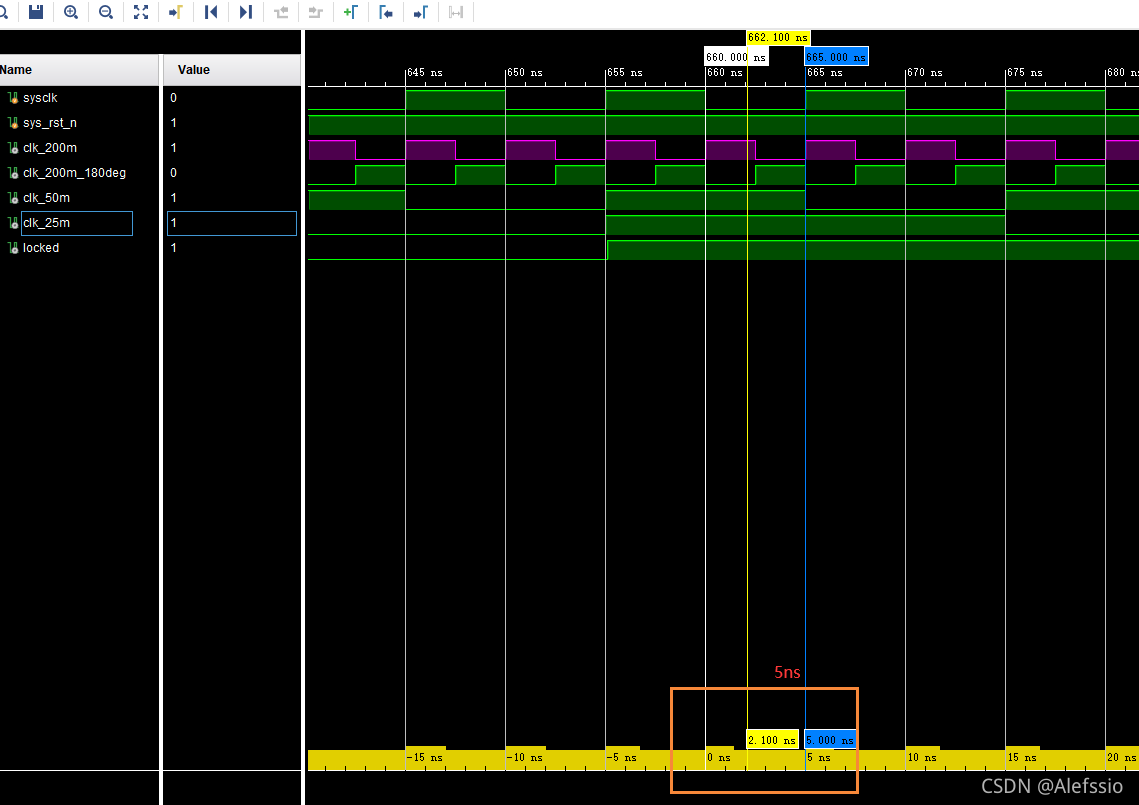

通过仿真查看输出时钟信号是否正确

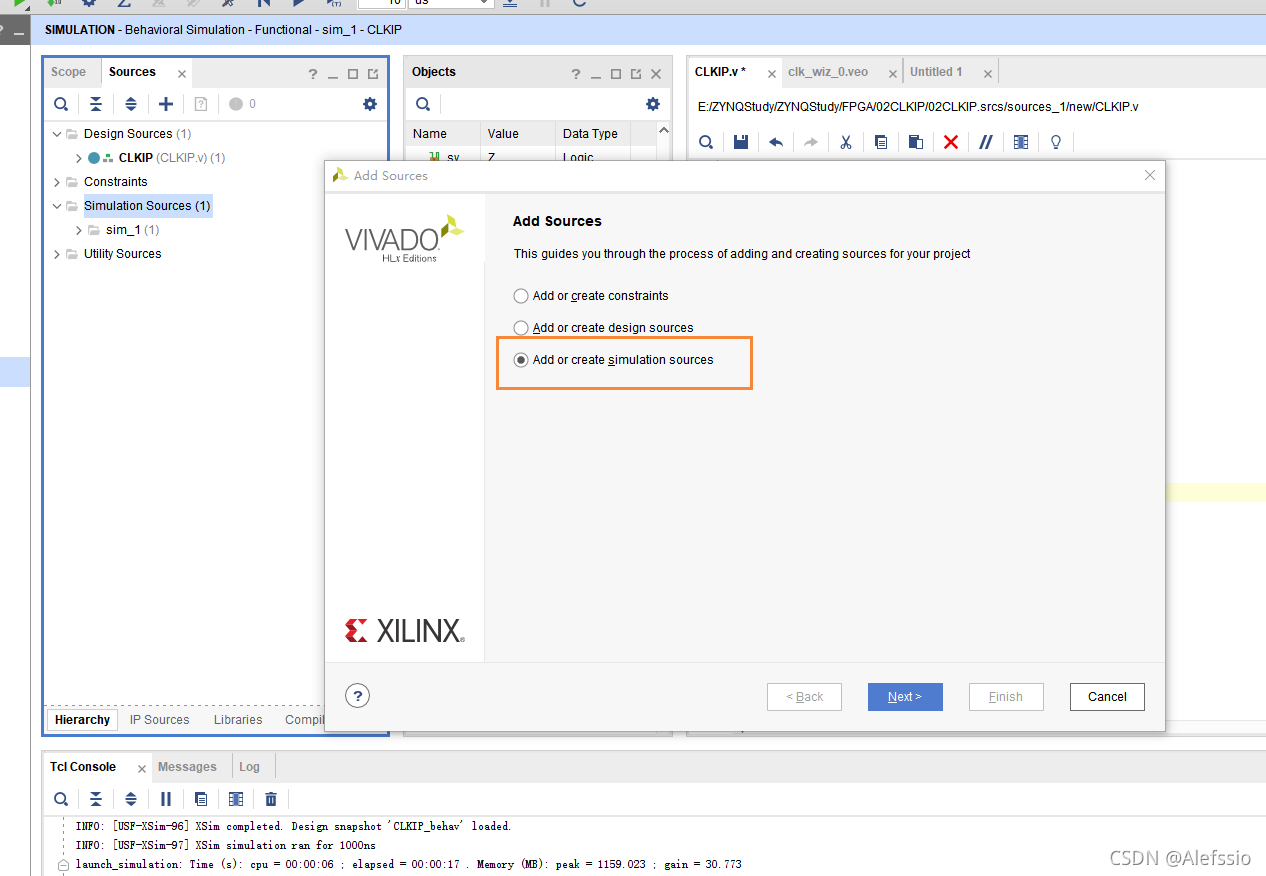

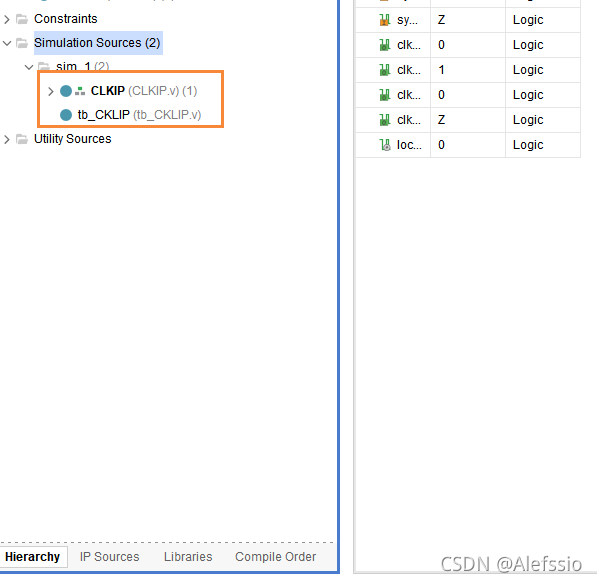

添加仿真文件

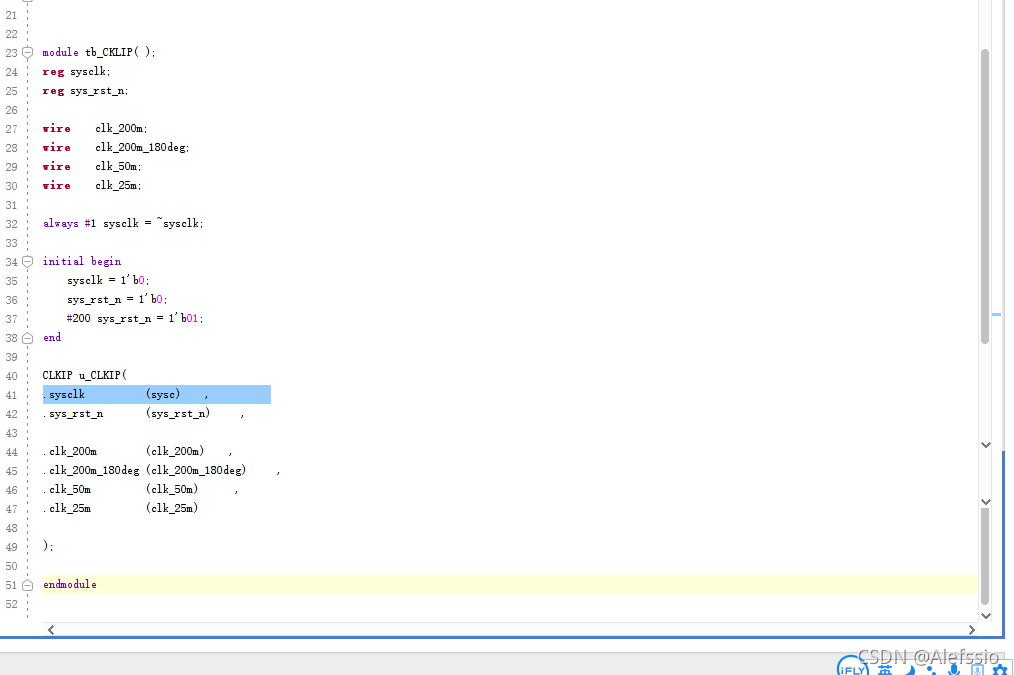

编写代码

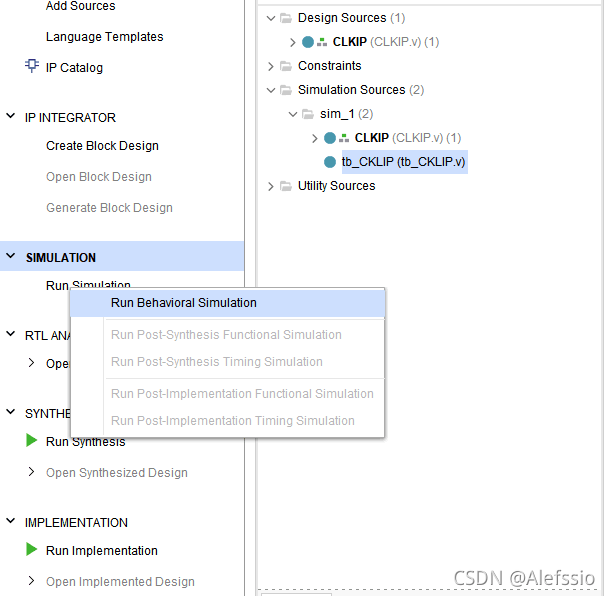

点击最上方RUN

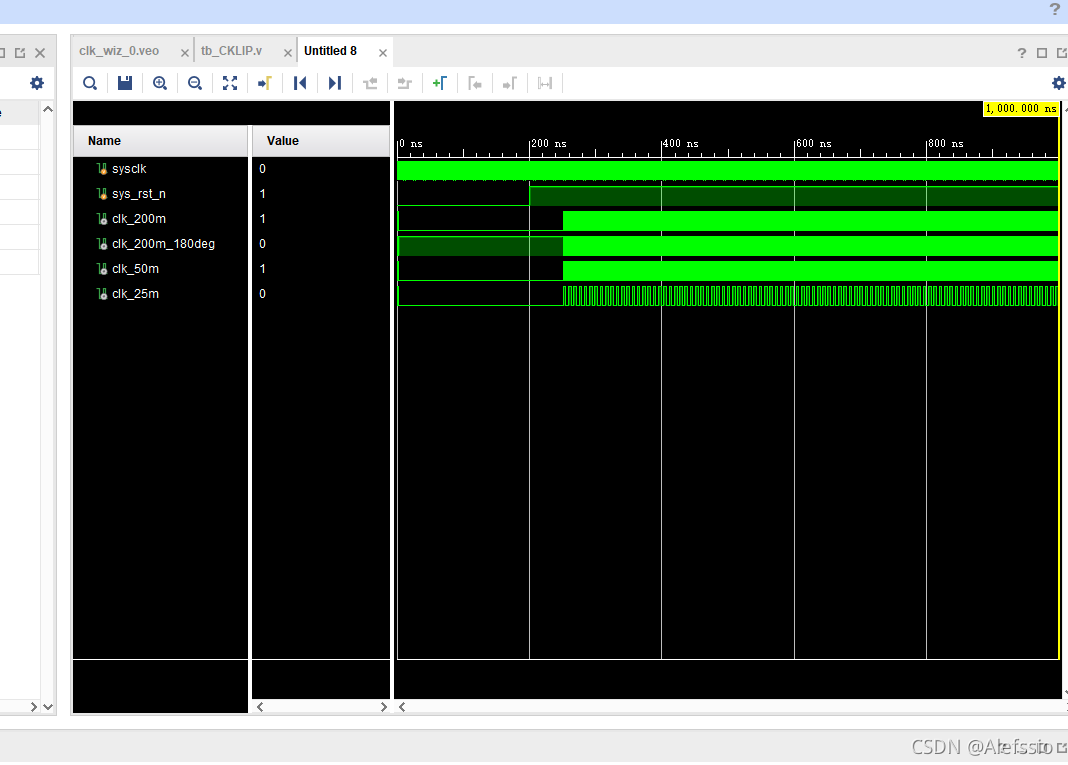

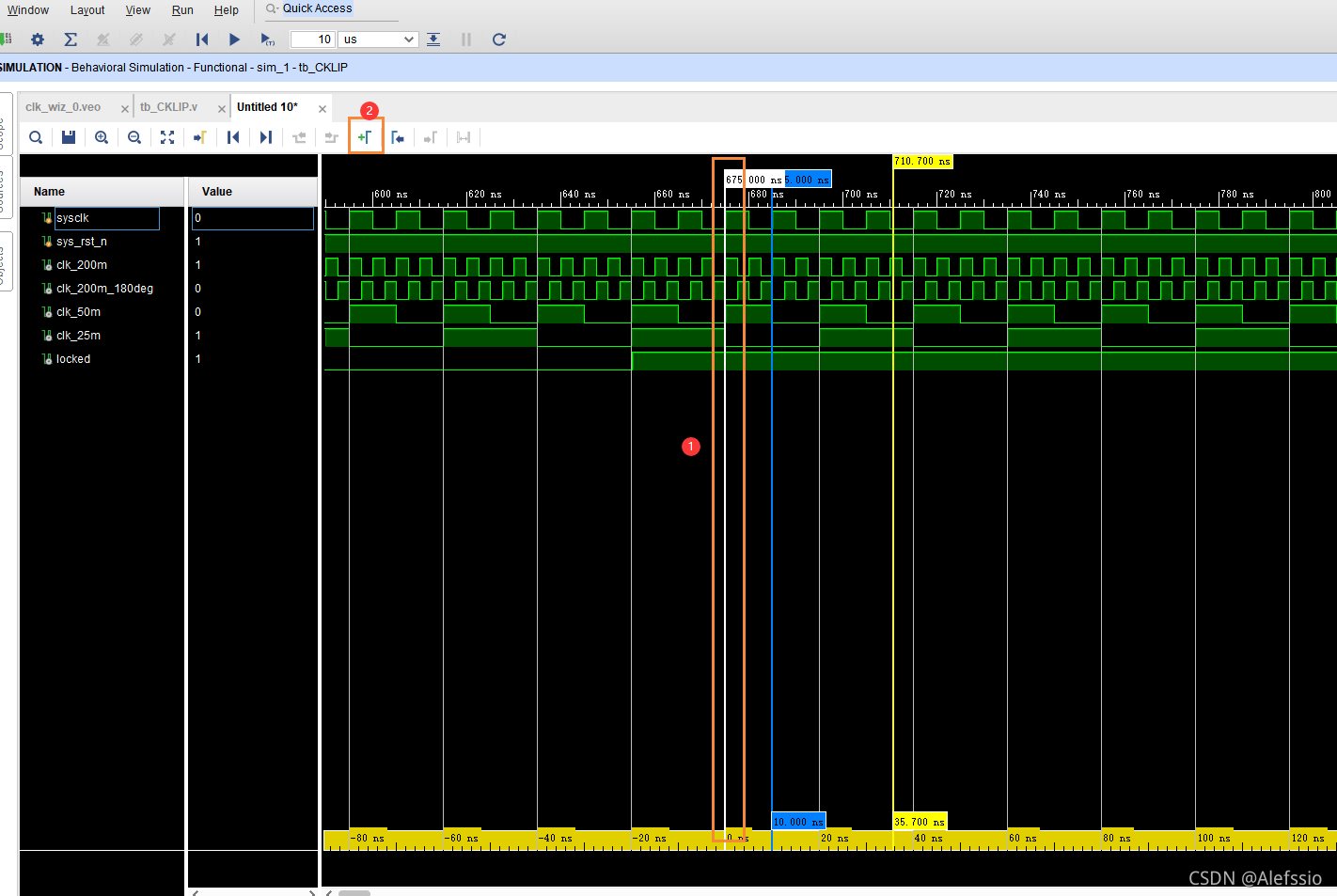

添加标记

双击任意一标记即可查看其信号由于标记为其上升沿以及下个上升沿其周期为10ns即为100MHZ

对200Mhz进行查看(紫色)为5ns 200Mhz

通过观察发现都符合。

747

747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?